FPGA----只读存储器(ROM)

Verilog HDL:

module ROM_ex1 (addr, data, en);

input [:] addr;//地址选择信号

input en; //使能端

output reg [:] data;//数据输出端

reg[:] data1 [:];

always @(*)

begin

data1[] <= 'b1010_1001;

data1[] <= 'b1111_1101;

data1[] <= 'b1110_1001;

data1[] <= 'b1101_1100;

data1[] <= 'b1011_1001;

data1[] <= 'b1100_0010;

data1[] <= 'b1100_0101;

data1[] <= 'b0000_0100;

data1[] <= 'b1110_1100;

data1[] <= 'b1000_1010;

data1[] <= 'b1100_1111;

data1[] <= 'b1100_0001;

data1[] <= 'b1001_1111;

data1[] <= 'b1010_0101;

data1[] <= 'b0101_1100;

if (en)

begin

data[:] <= data1[addr];

end

else

begin

data[:] <= 'bzzzz_zzzz;

end

end

endmodule

Testbench:

`timescale ps/ ps

module ROM_ex1_vlg_tst();

reg [:] addr;

reg en;

wire [:] data; ROM_ex1 i1 (

.addr(addr),

.data(data),

.en(en)

);

initial

begin

addr = 'd0;

en = 'b0;

# addr = 'd5;

en = 'b1;

# addr = 'd9;

# addr = 'd12;

# addr = 'd15;

$display("Running testbench");

end endmodule

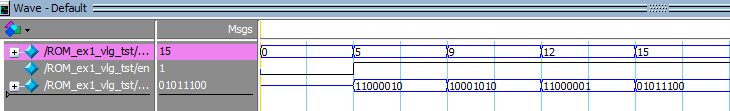

仿真波形:

观察波形可知,当 en 为“1”时,data 输出数据,否则 data 为高阻态,addr 为地址选择信号,当其输入不同的值时,data 输出相应的存储的数据。

FPGA----只读存储器(ROM)的更多相关文章

- FPGA中ROM与RAM相关知识总结(五)

把看到的关于存储的一些东西整理一下,有些话来自于网友,所以还是那句话,看到的人要带着自己的思考去看,记住尽信书不如无书,fighting!!! 一.基本概念 最熟悉的两个词语应该是RAM与ROM,RA ...

- Xilinx FPGA使用——ROM初始化文件

在调用ROM的IP Core时,需要对其进行初始化,利用MATLAB生成其初始化数据文件. 工具:ISE 14.7.MATLAB.notepad++ 废话不多说,直接上MATLAB代码,生成了一个10 ...

- 【MATLAB】产生FPGA中ROM需要的余弦表

产生的二进制数为带符号二进制数,最高位是符号位. function [ DATA ] = cos_gen( Num_addr,Num_out ) % 用来产生ROM需要的余弦表,输出为有符号二进制数 ...

- 谈谈IC、ASIC、SoC、MPU、MCU、CPU、GPU、DSP、FPGA、CPLD

IC (integrated circuit) 集成电路:微电路.微芯片.芯片:集成电路又分成:模拟集成电路(线性电路).数字集成电路.数/模混合集成电路: 模拟集成电路:产生.放大.处理各种模拟信号 ...

- ROM与RAM知识

“ROM”和“RAM”的意思: “ROM”:N年前代表一种只能写入和读取,而不能改写和擦除的设备,可以用光驱CD-ROM来说明这个道理.目前的“ROM”已经不是这个道理了,它的技术已经飞快的发展到现在 ...

- ROM及其他知识

ROM--Read Only Memory 中文意思是:只读存贮器 以前的游戏机用的都是卡带,里面是一块或几块集成电路芯片,游戏程序就是在生产厂家一次性写入这几块芯片,以后用户玩游戏的时候只能读出 ...

- 【小梅哥FPGA进阶教程】第十四章 TFT屏显示图片

十四.TFT屏显示图片 本文由杭电网友曾凯峰贡献,特此感谢 学习了小梅哥的TFT显示屏驱动设计后,想着在此基础上通过TFT屏显示一张图片,有了这个想法就开始动工了.首先想到是利用FPGA内部ROM存储 ...

- GSM BTS Hacking: 利用BladeRF和开源BTS 5搭建基站

引文 如果你已经购买了Nuand(官方)BladeRF x40,那么就可以在上面运行OpenBTS并可以输入一些指令来完成一些任务.一般来说HackRF,是一款覆盖频率最宽的SDR板卡.它几乎所有的信 ...

- 数字逻辑实践6-> 从数字逻辑到计算机组成 | 逻辑元件总结与注意事项

00 一些前言 数字逻辑是计算机组成与体系结构的前导课,但是在两者的衔接之间并没有那么流畅,比如对面向硬件电路的设计思路缺乏.这篇总结是在数字逻辑和计组体系结构的衔接阶段进行的. 虽然这篇文是两门课的 ...

- 调用altera IP核的仿真流程—上

调用altera IP核的仿真流程—上 在学习本节内容之后,请详细阅读<基于modelsim-SE的简单仿真流程>,因为本节是基于<基于modelsim-SE的简单仿真流程>的 ...

随机推荐

- 字典序的第K小数字

今天zyb参加一场面试,面试官听说zyb是ACMer之后立马抛出了一道算法题给zyb:有一个序列,是1到n的一种排列,排列的顺序是字典序小的在前,那么第k个数字是什么?例如n=15,k=7, 排列顺序 ...

- 1095 解码PAT准考证 (25 分)

PAT 准考证号由 4 部分组成: 第 1 位是级别,即 T 代表顶级:A 代表甲级:B 代表乙级: 第 2~4 位是考场编号,范围从 101 到 999: 第 5~10 位是考试日期,格式为年.月. ...

- npm install 卡住的时候的处理

[From] http://www.eguidedog.net/doc/what-to-do-when-npm-install-hangs.php 翻译一下,npm install 经常卡在下载某个包 ...

- SPOJ - AMR11

A Thanks a lot for helping Harry Potter in finding the Sorcerer's Stone of Immortality in October. D ...

- 论文笔记 | Self-organized Text Detection with Minimal Post-processing via Border Learning

论文链接:http://openaccess.thecvf.com/content_ICCV_2017/papers/Wu_Self-Organized_Text_Detection_ICCV_201 ...

- oracle12C--DG 状态集

一,物理备库 01,状态查询与状态详解 select switchover_status from v$database 02,状态转换到备用数据库 alter database commit to ...

- ansible 入门学习(一)

一,ansible 目录结构 (来自于ansible权威指南) 二,ansible.cfg 配置项说明 /etc/ansible/ansible.cfg --> ———————————————— ...

- nodejs基础知识查缺补漏

1. 单线程.异步I/O.对比php nodejs是单线程的,但是是异步I/O,对于高并发时,它也能够快速的处理请求,100万个请求也可以承担,但是缺点是非常的耗内存,但是我们可以加大内存, 所以能用 ...

- RabbitMQ学习整理

1.什么是消息队列? 概念: 消息队列(Message Queue,简称MQ),本质是个队列,FIFO先入先出,只不过队列中存放的内容是一些Message. 2.为什么要用消息队列,应用场景? 不同系 ...

- Linux下MySQL数据库主从同步配置

说明: 操作系统:CentOS 5.x 64位 MySQL数据库版本:mysql-5.5.35 MySQL主服务器:192.168.21.128 MySQL从服务器:192.168.21.129 准备 ...