7 Serial Configuration 理解 (一)

reference : ug470- 7 series config.pdf

7系列器件有5种配置接口,每种配置接口对应一种或者多种配置模式和总线位宽。配置时序相对于引脚的CCLK,即使在内部产生CCLK的主模式下也是如此。

Master模式包括: serial / spi / bpi / selectMAP ; JTAG模式 ; Slave模式包括:serial/selectMAP ;

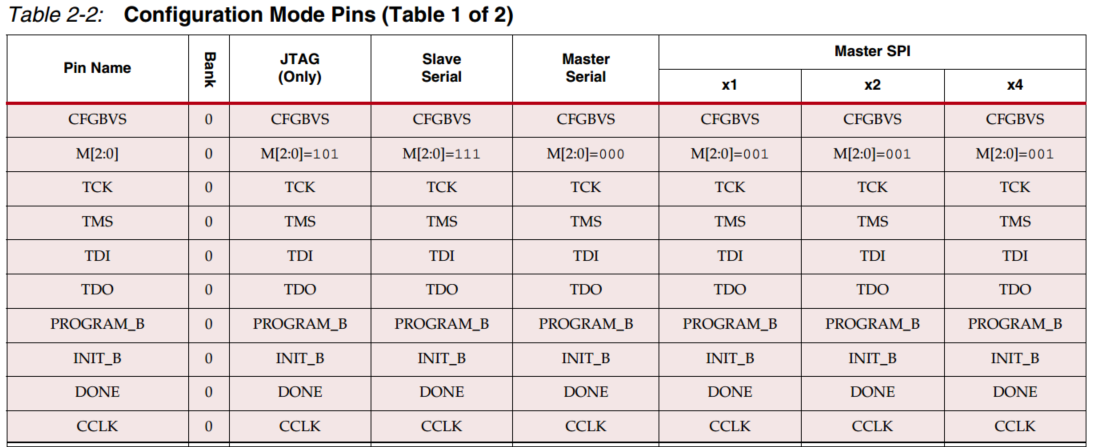

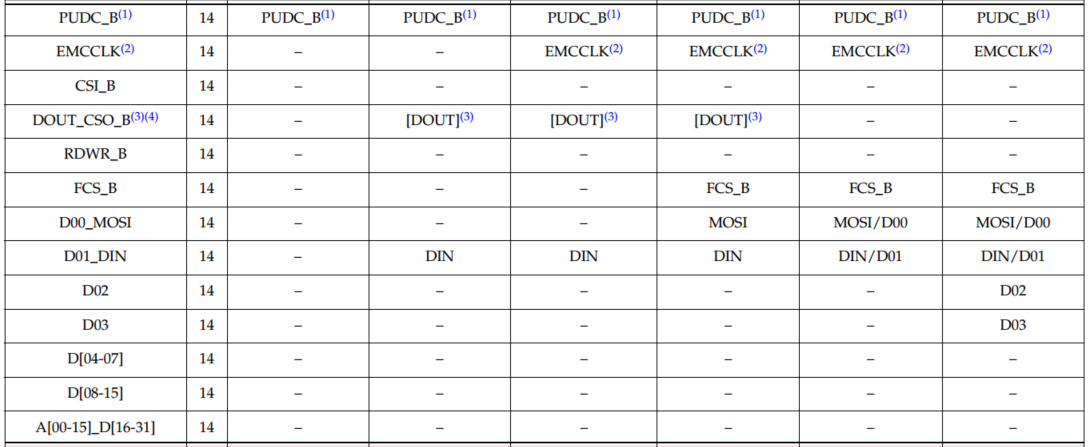

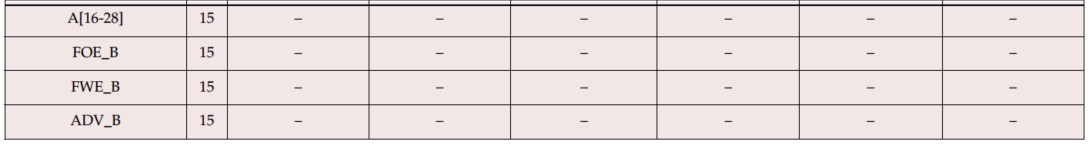

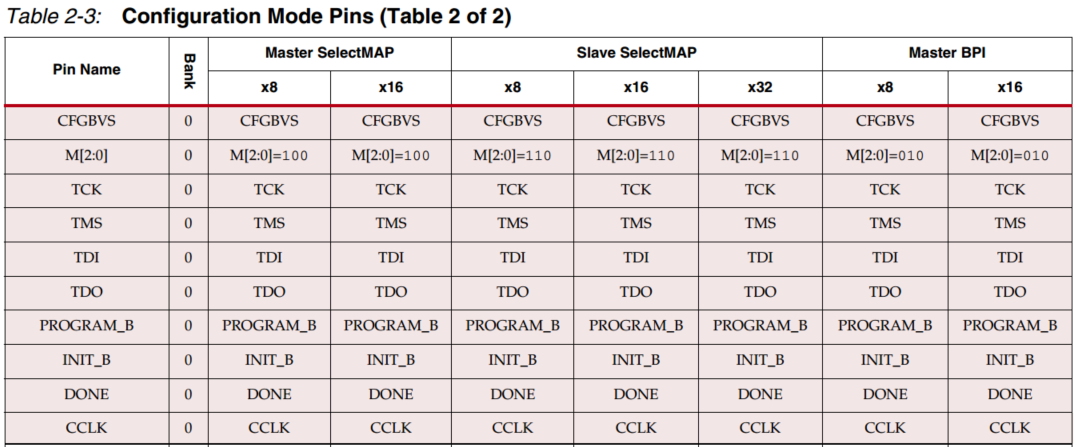

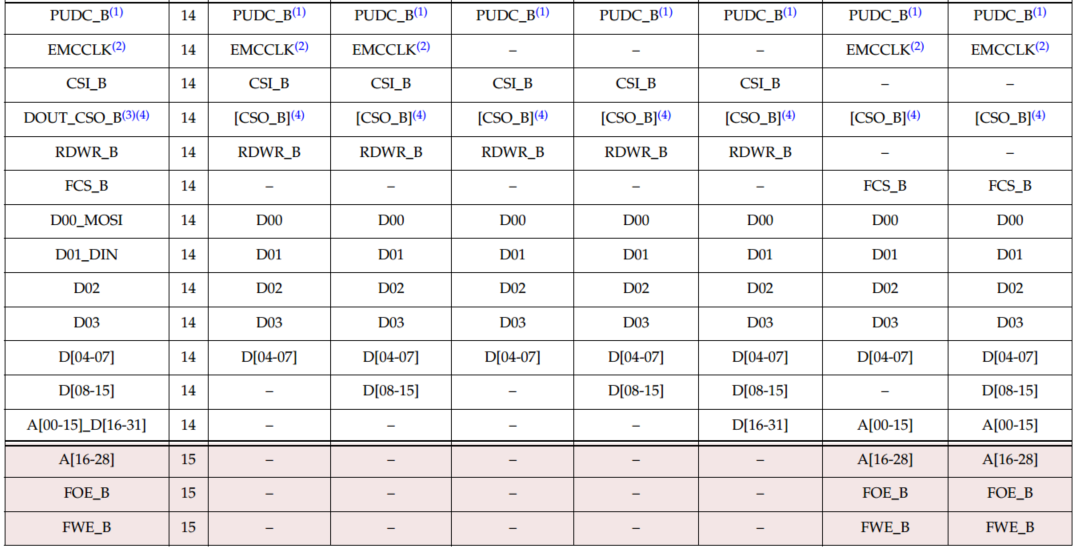

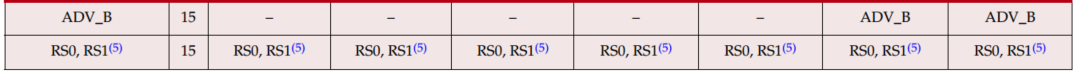

每种配置模式都有一组相应的接口引脚,跨越了7系列FPGA上的一个或多个I / O bank。 Bank 0包含专用配置引脚,始终是每个配置接口的一部分。 Bank 14和Bank 15包含涉及特定配置模式的多功能引脚。 在7系列FPGA数据手册中规定工作在3.3V,2.5V,1.8V或1.5V的bank中配置引脚的开关特性。

所有JTAG和专用配置引脚都位于一个独立的专用bank 0中,该bank具有专用电源(VCCO_0)。多功能引脚位于bank14和15中。

所有专用输入引脚均工作在VCCO_0 LVCMOS电平(LVCMOS18,LVCMOS25或LVCMOS33)。所有有源专用输出引脚均在VCCO_0电压电平下工作,输出标准设置为LVCMOS,12 mA驱动,快速摆率。对于使用多功能I / O的所有模式,必须将关联的VCCO_14或VCCO_15连接到适当的电压,以匹配配置器件的I / O标准。多功能引脚在配置时也是LVCMOS,12 mA驱动,快速摆率。 如果使用Persist选项,所选配置模式的多功能I / O,在配置后保持激活状态,I / O标准设置为LVCMOS的通用默认值,12 mA 驱动,慢摆率。

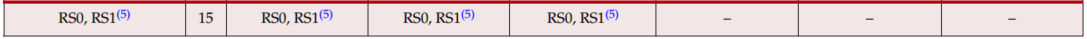

*配置模式引脚及其在I / O bank上的位置

注:

1. PUDC_B在配置期间具有特殊功能,但独立于所有配置接口,即PUDC_B不需要与配置接口中的其他引脚电压兼容。

2. EMCCLK仅在ExtMasterCclk_en选项启用EMCCLK作为主时钟配置模式的输入时使用。

3. DOUT仅用于串行配置菊花链,用于将数据输出到下游FPGA(或用于DebugBitstream选项)。 否则,DOUT为高阻抗。

4. CSO_B仅用于并行配置菊花链,用于向下游设备输出芯片使能信号。 否则,CSO_B为高Z.

5. RS0和RS1仅在启动MultiBoot事件或启用ConfigFallback选项并发生Fallback事件时被驱动。否则,RS0和RS1为高阻态。 使用RS [1:0]引脚进行配置时,建议不要在用户模式下使用它们。

6. 空单元表示引脚未在配置模式下使用,并且在配置期间被忽略并且为高阻态。

*配置引脚定义

| 引脚名称 | bank | 类型 | 方向 | 描述 |

| CFGBVS | 0 | 专用 | 输入 |

Configuration Banks Voltage Select VCCO0电压为3.3/2.5v时,CFGBVS为高电平,即接到VCCO0; VCCO0电压为1.8v时,CFGBVS为低电平,即接到GND。 |

| M[2:0] | 0 | 专用 | 输入 | Configuration Mode |

| TCK | 0 | 专用 | 输入 | JTAG Test Clock |

| TMS | 0 | 专用 | 输入 | JTAG TEST Mode Select |

| TDI | 0 | 专用 | 输入 | JTAG Test Data Input |

| TDO | 0 | 专用 | 输出 | JTAG Test Data Output |

| PROGRAM_B | 0 | 专用 | 输入 |

Program Bar 低电平有效复位配置逻辑。当PROGRAM_B脉冲为低电平时,FPGA配置被清零并启动新的配置序列。 在下降沿启动配置复位,并且配置(即编程)序列在随后的上升沿开始。 注意:上电时保持PROGRAM_B为低电平不会使FPGA配置保持复位状态。 而是使用INIT_B来延迟上电配置序列。 |

| INIT_B | 0 | 专用 | 双向(开漏) |

Initialization (bar) 低电平有效的FPGA初始化引脚或配置错误信号。 当FPGA处于配置复位状态,FPGA正在初始化(清除)其配置存储器时,或者当FPGA检测到配置错误时,FPGA将此引脚驱动为低电平。 完成FPGA初始化过程后,INIT_B释放到高阻态,此时外部电阻预计将INIT_B拉高。 在上电期间,INIT_B可以在外部保持低电平,以在初始化过程结束时停止上电配置序列。 当初始化过程后在INIT_B输入检测到高电平时,FPGA继续执行M [2:0]引脚设置所指示的配置序列的其余部分。 将INIT_B连接至一个≤4.7kΩ的上拉电阻至VCCO_0,以确保从低到高的转换。 |

| DONE | 0 | 专用 | 双向 |

Done DONE引脚上的高电平信号表示配置序列已完成。 |

| CCLK | 0 | 专用 | 输入/输出 |

Configuration Clock 除JTAG模式外,CCLK在所有模式下运行同步FPGA配置序列。 |

| PUDC_B | 14 | 多功能 | 输入 |

Pull-Up During Configuration (bar) 低电平有效PUDC_B输入使能上电后和配置期间的SelectIO引脚上的内部上拉电阻。 |

| EMCCLK | 14 | 多功能 | 输入 |

External Master Configuration Clock •对于主模式:FPGA可以选择切换到EMCCLK作为时钟源,而不是内部振荡器,用于驱动内部配置引擎。 EMCCLK频率可以选择通过比特流设置(ExtMasterCclk_en)进行分频,并作为主CCLK信号转发输出。 |

| CSI_B | 14 | 多功能 | 输入 |

Chip Select Input (bar) 低电平有效输入,用于启用FPGA SelectMAP配置接口。 |

| CSO_B | 14 | 多功能 | 输出(开漏) |

Chip Select Output (bar) 低电平有效开漏输出,可以驱动低电平,以便在并行配置菊花链中启用下游FPGA的从属SelectMAP配置接口。 |

| DOUT | 14 | 多功能 | 输出 |

Data Output DOUT是串行配置菊花链的数据输出。 •对于BPI和SelectMAP模式:DOUT是一个多用途引脚,用作CSO_B引脚。 |

| RDWR_B | 14 | 多功能 | 输入 |

Read/Write (bar) RDWR_B确定SelectMAP数据总线的方向。 当RDWR_B为高电平时,FPGA将输出读数据到SelectMAP数据总线上。 当RDWR_B为低电平时,外部控制器可以通过SelectMAP数据总线将数据写入FPGA。 |

| D00_MOSI | 14 | 多功能 | 双向 |

Master-Output Slave-Input FPGA(主)SPI模式输出,用于向SPI(从)flash器件发送命令。 |

| D01_DIN | 14 | 多功能 | 双向 |

Data Input DIN是串行数据输入引脚。 默认情况下,来自DIN的数据在CCLK的上升沿捕获。 |

| D[00-31] | 14 | 多功能 | 双向 |

Data Bus |

|

D [00-31]引脚的子集或全部是SPI x2,SPI x4,BPI或SelectMAP模式的数据总线接口。 |

||||

| A[00-28] | 14 or 15 | 多功能 | 输出 |

Address Bus A[00-28]引脚输出地址到并行NOR(BPI)闪存。 A00是最低的地址位。 |

| FCS_B | 14 | 多功能 | 输出 |

Flash Chip Select (bar) 低电平有效芯片选择输出,支持SPI或BPI闪存器件进行配置。 |

| FOE_B | 15 | 多功能 | 输出 |

Flash Output-Enable(bar) 用于并联NOR闪存的低电平有效输出使能控制信号。 |

| FWE_B | 15 | 多功能 | 输出 |

Flash Write-Enable (bar) 用于并行NOR闪存的低电平有效写入使能控制信号。 |

| ADV_B | 15 | 多功能 | 输出 |

Address Valid (bar) 用于并行NOR闪存的低电平有效地址有效输出信号。 |

| RS0,RS1 | 15 | 多功能 | 输出 |

Revision Selection RS0和RS1引脚是版本选择输出引脚,用于驱动并行闪存上的高位地址线。 通常,RS0和RS1在配置期间为高阻态。 但是,FPGA可以在两种可能的条件下驱动RS0和RS1引脚。 *启用ConfigFallback选项后,FPGA会在检测到配置错误之后的回退配置过程中将RS0和RS1驱动为低电平。 *当启动用户调用的MultiBoot配置时,FPGA可以在MultiBoot配置过程中将RS0和RS1引脚驱动为用户定义的状态。 如果禁用回退(默认)并且未使用MultiBoot,或者使用SPI模式,则RS0和RS1为高阻态且可以保持未连接状态。 |

| VCCBATT | N/A | Supply Voltage | N/A |

Battery Backup Supply VCCBATT是FPGA内部易失性存储器的电池备份电源,用于存储AES解密器的密钥。 对于需要来自易失性密钥存储区的解密密钥的加密比特流,将此引脚连接到电池以在FPGA未供电时保留密钥。 如果不要求使用易失性密钥存储区中的解密密钥,请将此引脚连接到GND或VCCAUX。 引脚名称包含“_0”存储区标识,但它不是I / O,不受VCCO_0的影响。 |

注:每个I/O都参考所在bank的VCCO电源电压。如:“0”表示I / O以Bank 0的VCCO_0为参考。

7 Serial Configuration 理解 (一)的更多相关文章

- 7 Serial Configuration 理解(二)

*Serial Configuration Mode 串行配置模式分为:Master Serial 和 Slave Serial (如下图)两类: 两者的区别在与CCLK的输入输出方向:主动模式下为输 ...

- 7 Serial Configuration 理解(三)

*Dynamic Reconfiguration Port(DRP) 动态重配置端口:在7系列FPGA中,配置存储器主要用于实现用户逻辑,连接和I / O,但它也用于其他目的. 例如,它用于指定功能块 ...

- ASP.Net Core Configuration 理解与源码分析

Configuration 在ASP.NET Core开发过程中起着很重要的作用,这篇博客主要是理解configuration的来源,以及各种不同类型的configuration source是如何被 ...

- linux中serial driver理解【转】

转自:http://blog.csdn.net/laoliu_lcl/article/details/39967225 英文文档地址:myandroid/kernel_imx/Documentatio ...

- Spartan-6 FPGA Configuration

These configuration pins serve as the interface for a number of different configuration modes: • JTA ...

- Jmeter使用入门

修改时间 修改内容 修改人 2016.3.12 创建 刘永志 2016.6.18 完成 刘永志 Jmeter简介 Jmeter的基本概念 百度百科: Apache JMeter是Apache组织开发的 ...

- Jmeter 测试工具

Jmeter的基本概念 百度百科: Apache JMeter是Apache组织开发的基于Java的压力测试工具.用于对软件做压力测试,它最初被设计用于Web应用测试,但后来扩展到其他测试领域. 它可 ...

- Jmeter安装和启动和使用

一.安装配置JDK 1.下载安装jdk,地址:http://www.oracle.com/technetwork/java/javase/downloads/index.html 2.配置JDK环境变 ...

- SoC FPGA开发板的FPGA配置数据下载和固化

小梅哥编写,未经许可,严禁用于任何商业用途 2018年7月2日星期一 soc fpga的烧写和固化方式与传统的纯fpga固化方式即存在形式上的相同,也存在细节上的差异,特整理此文. AC501-So ...

随机推荐

- Fat jar用途

1.Fat jar用途 我们都知道默认的eclipse下打包jar时,是无法连同外部引用包一起打包的.所以一般我们可以自己编写MINIFEST.MF文件来手动将需要的jar包加入进来,但是这样对于引用 ...

- springBoot springSecurty: x-frame-options deny禁止iframe调用

springBoot springSecurty: x-frame-options deny禁止iframe调用 https://blog.csdn.net/whiteforever/article ...

- javascript之封装(引用网络)

一. 例:事件监听封装 jQuery 中的事件监听,完全可以用 addEventListener/attachEvent 模拟,分别对应于现代浏览器和 IE ,可以把两个方法封装一下,但是为了方便,这 ...

- 2017-09-21xlVBA_蒸发SQL循环查询1

'ARRAY("1991","1992","1993","1994","1996","19 ...

- BFS+二进制状态压缩 hdu-1429

好久没写搜索题了,就当练手吧. vis[][][1025]第三个维度用来维护不同key持有状态的访问情况. 对于只有钥匙没有对应门的位置,置为'.',避免不必要的状态分支. // // main.cp ...

- DAG最长路问题 hdu-1224

用DFS+记忆化写了一下,拓扑排序+DP的我还没弄明白.据说Codeforces 721C就是这类题目,因为有费用限制,DFS不太好写,有时间把DP法想明白来. #include <iostre ...

- Codeforces 1151F Sonya and Informatics (概率dp)

大意: 给定01序列, 求随机交换k次后, 序列升序的概率. 假设一共$tot$个$0$, 设交换$i$次后前$tot$个数中有$j$个$0$的方案数为$dp[i][j]$, 答案即为$\frac{d ...

- 【JS】【2】ajax传的参数为数组时,后台接收为null的处理

前言: 1,参考博客:解决JavaScript中使用$.ajax方式提交数组参数 - Just_Do - 博客园(http://www.cnblogs.com/caoyc/p/5710702.html ...

- node模块之net模块——socket

当我们去面试的时候,常常会遇到这样一个问题:当用户在浏览器地址栏输入一段url发出资源请求后,到服务端返回数据呈现给用户的这个过程都发生了什么? 我们把进行通信的这两个端(这里指的是,浏览器和资源获取 ...

- python-flask-配置文件的源码分析

方式一:app.config['xx'] = 'xxx'源码分析:#第1步:class Flask(_PackageBoundObject): self.config = self.make_c ...