verilog语法实例学习(11)

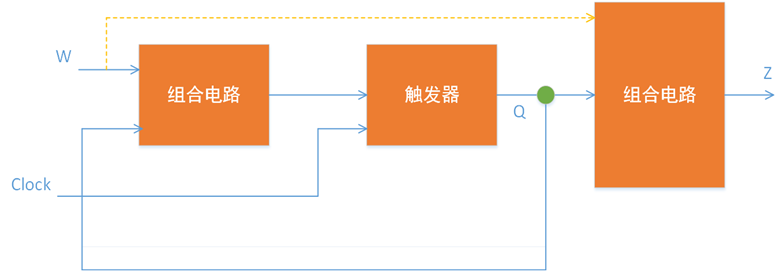

同步时序电路的一般形式

时序电路由组合逻辑以及一个或多个触发器实现。一般的架构如下图所示:W为输入,Z为输出,触发器中存储的状态为Q。在时钟信号的控制下,触发器通过加在其输入端的组合逻辑输入,使得电路从一个状态变成另一个状态。采用边沿触发的触发器可以确保一个时钟周期内只发生一次状态变化。它们可以由时钟上升沿或下降沿触发,产生这种状态变化的时钟边沿称为有效时钟边沿。

发器有两路组合逻辑输入,分别为原始输入W和触发器的当前输出Q,因此当前状态的改变不仅却决于触发器的当前状态,还取决于电路的原始输入。在上图中,可以得知,时序电路的输出由另一个组合电路产生,该组合电路是当前原始输入和触发器当前状态的函数。时序电路输出总取决于电路当前状态,却不一定直接依赖原始输入,图中的虚线表示可能存在也可能不存在。为了区分这两种存在,通常将输出仅由电路状态决定的时序电路称为Moore型,而输出由电路状态和原始输入共同决定的称为Mealy型。

摩尔有限状态机

一个实际问题的描述:假设自动驾驶的汽车,以一定的速度运行,w=0,表示运行速度正常,w=1,表示运行超速。速度控制的策略,等间隔时间检测速度,如果两次或多次连续超速(w=1),则在一个时间间隔后开始设置减速信号z=1,否则z=0。如果用电路描述上述问题,则等时间间隔为时钟周期,在每个时钟的上升沿进行状态判断。输入输出信号时序序列如下:

| 时钟周期 | t0 | t1 | t2 | t3 | t4 | t5 | t6 | t7 | t8 | t9 | t10 |

| w | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 1 |

| z | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 |

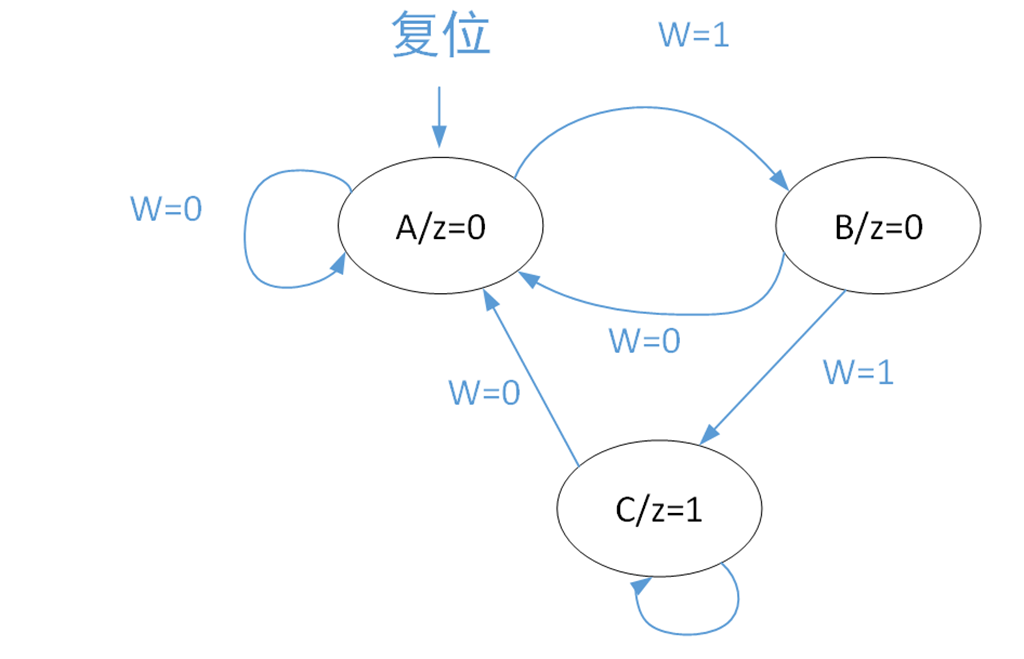

我们用状态机来描述该问题:首先有一个起始状态A,电路加载或复位后为该状态。假设当前为A状态,如果w=0,不做任何事情,输出z=0,在时钟上升沿检测后,仍保持A状态,输出z=0,如果w=1,仍输出z=0,在下一个时钟周期边沿进入状态B,输出z=0;假设当前为B状态,如果w=0,输出z=0,在下一个时钟上升沿进入A状态,输出z=0,如果w=1,此时z输出仍为0,在下一个时钟上升沿,进入状态C,此时输出z=1;假设当前状态为C状态,如果w=0,此时仍有z=1,在下一个时钟上升沿进入A状态,此时输出z=0,如果w=1,在下一个时钟上升沿,仍操持状态C,输出z=1。

该状态机的状态表如下:

| 现在状态 | 下一状态 | 输出 z | |

| w=0 | w=1 | ||

| A | A | B | 0 |

| B | A | C | 0 |

| C | A | C | 1 |

状态机状态图如下:复位信号强制电路进入A状态,任何条件下复位都成立,图中用箭头表示。

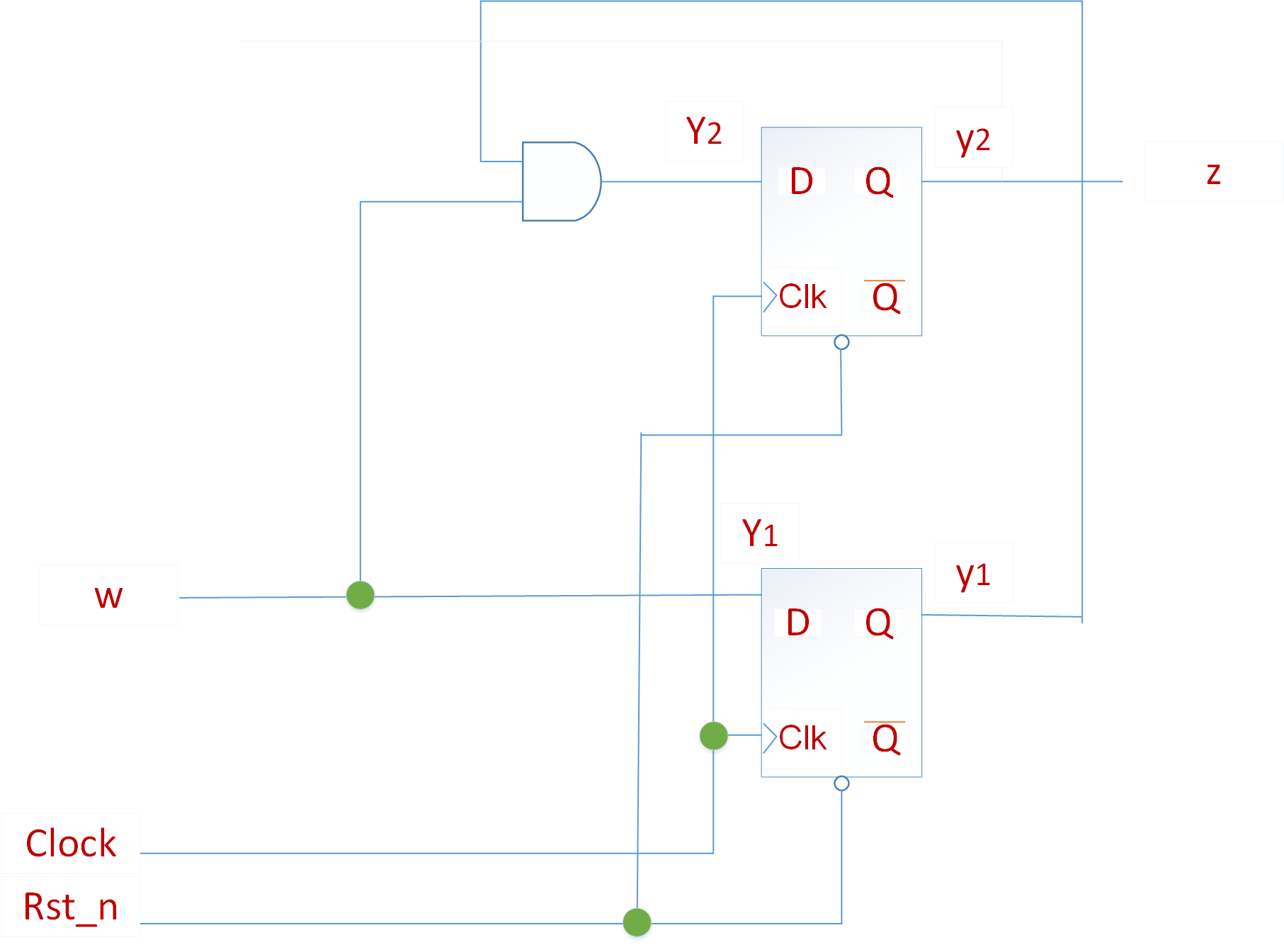

上面的状态图和状态表中,我们用了3个状态A,B,C。在逻辑电路实现过程中,每个状态用状态变量的特定取值(值的组合)来表示。每个状态变量可能以触发器来实现。由于需要实现3种状态,因此采用2个状态变量就可以满足要求,令两个状态变量分别用y1,y2,来表示电路当前状态。另外用Y1,Y2表示下一状态,它由反馈电路和输入w决定。

从而,我们得到详细的状态赋值表。根据这个赋值表,我们能设计出具体电路,状态11在这个电路中没有使用。

| 现在状态 | 下一状态 | 输出 | ||

| w=0 | w=1 | |||

| y2y1 | Y2Y1 | Y2Y1 | z | |

| A | 00 | 00 | 01 | 0 |

| B | 01 | 00 | 10 | 0 |

| C | 10 | 00 | 10 | 1 |

| 11 | dd | dd | d | |

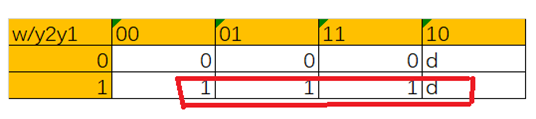

Y1的真值表

| w/y2y1 | 00 | 01 | 11 | 10 |

| 0 | 0 | 0 | d | 0 |

| 1 | 1 | 0 | d | 0 |

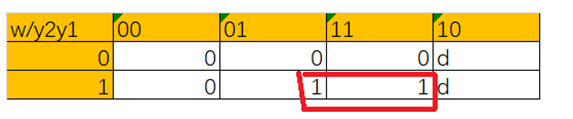

Y2的真值表

| w/y2y1 | 00 | 01 | 11 | 10 |

| 0 | 0 | 0 | d | 0 |

| 1 | 0 | 1 | d | 1 |

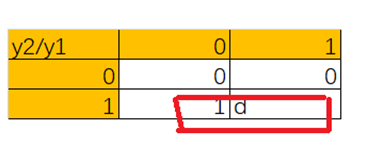

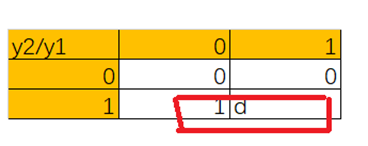

z的真值表

| y2/y1 | 0 | 1 |

| 0 | 0 | 0 |

| 1 |

1 |

d |

从上面赋值表中,我们能够得到下一个状态Y1,Y2的逻辑表达式为:

Y1=w~y1~y2

Y2=wy1~y2+w~y1y2(或w(y1+y2))

z=~y1y2(或z=y2)

考虑11状态,可以画出卡诺图来简化电路,简化后的电路Y2和z如上面括号中的蓝色表达式。

状态机的verilog代码:

module moore(clk, w, Rst_n, z); input clk; //时钟信号

input w;

input Rst_n; //复位信后

output z;

reg [1:0] y, Y; //现在的状态 parameter A=2'b00,B=2'b01,C=2'b10; always @(w,y)

begin

case(y)

A:

if(w==0) Y=A;

else Y=B;

B:

if(w==0) Y=A;

else Y=C;

C:

if(w==0) Y=A;

else Y=C;

default: Y=2'bxx;

endcase end always @(posedge clk,negedge Rst_n)

begin

if(Rst_n==0)

y <= A;

else

y <= Y;

end assign z=(y==C);

endmodule

testbench为:

`timescale 1ns/1ns

`define clock_period 20 module moore_tb;

reg w;

reg clk=1;

reg Rst_n;

wire z; moore moore0(.clk(clk),.w(w),.Rst_n(Rst_n),.z(z));

always # (`clock_period/2) clk = ~clk; initial

begin

w = 1'b0;

Rst_n = 1'b1;

#(`clock_period)

Rst_n = 1'b0;

#(`clock_period)

Rst_n = 1'b1;

w = 1'b0;

#(`clock_period)

w = 1'b1;

#(`clock_period)

w = 1'b0;

#(`clock_period)

w = 1'b1;

#(`clock_period)

w = 1'b1;

#(`clock_period)

w = 1'b0;

#(`clock_period)

w = 1'b1;

#(`clock_period)

w = 1'b1;

#(`clock_period)

w = 1'b1;

#(`clock_period)

w = 1'b0;

#(`clock_period)

w = 1'b1;

#(`clock_period)

w = 1'b1; #(`clock_period*20)

$stop;

end endmodule

如果用2’b11表示状态C,则有下面的状态表:

| 现在状态 | 下一状态 | 输出 | ||

| w=0 | w=1 | |||

| y2y1 | Y2Y1 | Y2Y1 | z | |

| A | 00 | 00 | 01 | 0 |

| B | 01 | 00 | 11 | 0 |

| C | 11 | 00 | 11 | 1 |

| 10 | dd | dd | d | |

Y1的真值表

| w/y2y1 | 00 | 01 | 11 | 10 |

| 0 | 0 | 0 | 0 | d |

| 1 | 1 | 1 | 1 | d |

Y2的真值表

| w/y2y1 | 00 | 01 | 11 | 10 |

| 0 | 0 | 0 | 0 | d |

| 1 | 0 | 1 | 1 | d |

Z的真值表

| y2/y1 | 0 | 1 |

| 0 | 0 | 0 |

| 1 | 1 | d |

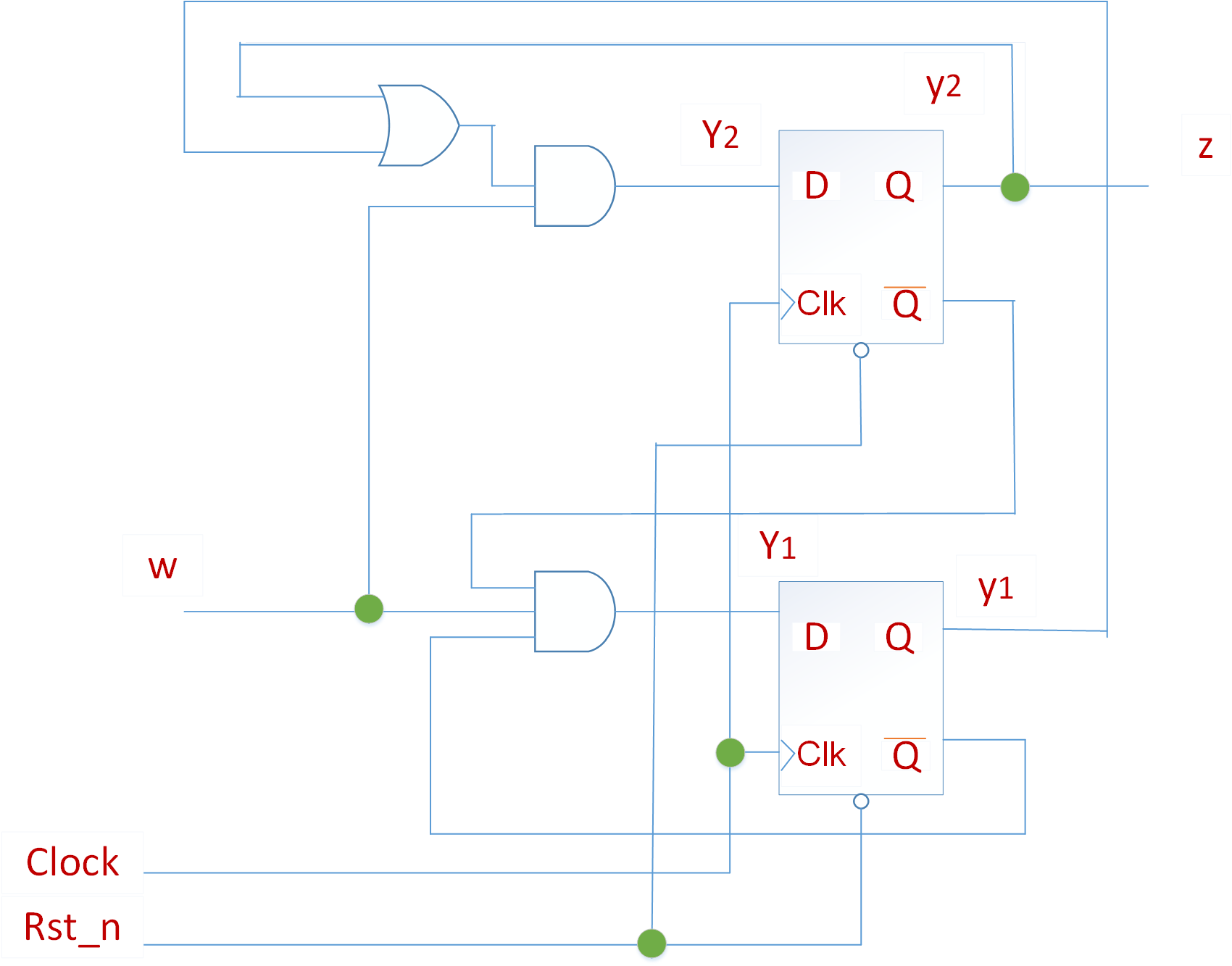

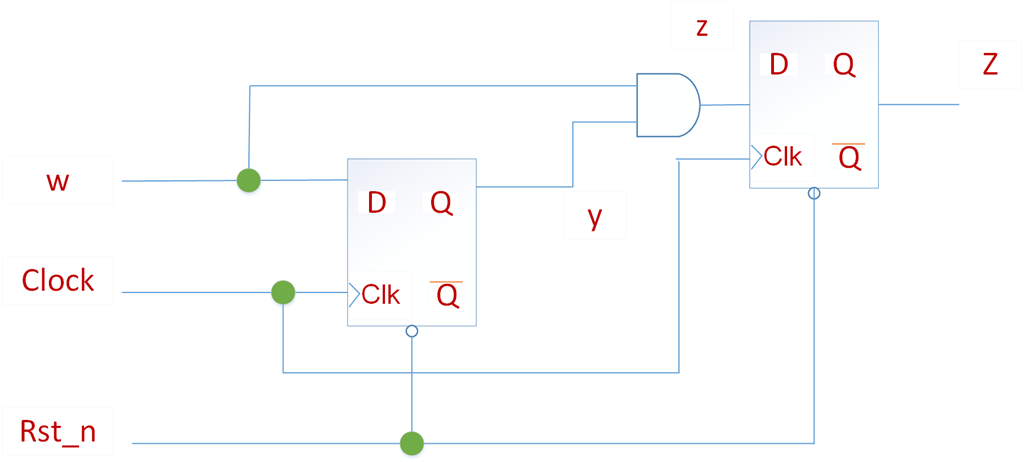

用卡诺图简化输出表达式,

则有Y1=w

Y2=wy1

z=y2

可以用下面更简化的电路实现:

假设用独热码表示状态A,B,C,则需要三位状态码,如下面的表格所示:

| 现在状态 | 下一状态 | 输出 | |

| w=0 | w=1 | ||

| y3y2y1 | Y3Y2Y1 | Y3Y2Y1 | z |

| 001 | 001 | 010 | 0 |

| 010 | 001 | 100 | 0 |

| 100 | 001 | 100 | 1 |

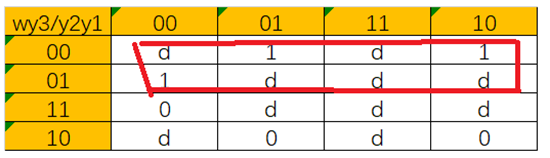

Y1的真值表

| wy3/y2y1 | 00 | 01 | 11 | 10 |

| 00 | d | 1 | d | 1 |

| 01 | 1 | d | d | d |

| 11 | 0 | d | d | d |

| 10 | d | 0 | d | 0 |

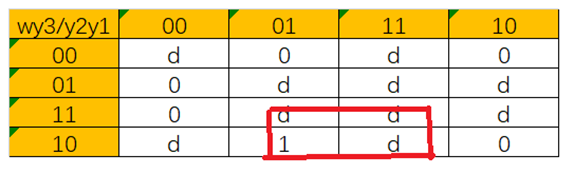

Y2的真值表

| wy3/y2y1 | 00 | 01 | 11 | 10 |

| 00 | d | 0 | d | 0 |

| 01 | 0 | d | d | d |

| 11 | 0 | d | d | d |

| 10 | d | 1 | d | 0 |

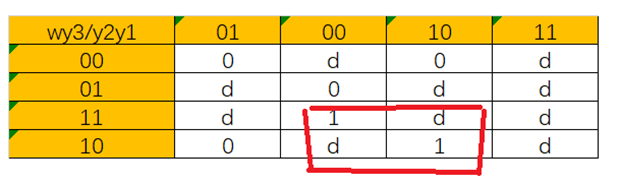

Y3的真值表

| wy3/y2y1 | 01 | 00 | 10 | 11 |

| 00 | 0 | d | 0 | d |

| 01 | d | 0 | d | d |

| 11 | d | 1 | d | d |

| 10 | 0 | d | 1 | d |

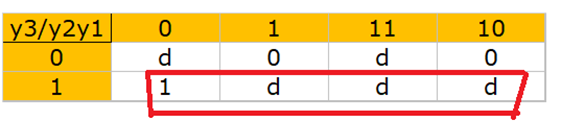

Z的真值表

| y3/y2y1 | 00 | 01 | 11 | 10 |

| 0 | d | 0 | d | 0 |

| 1 | 1 | d | d | d |

用卡诺图简化输出表达式,所以有

Y1=~w

Y2=wy1

Y3=w~y1

z=y3

没有下一个状态与y2有关,所以可以优化掉y2触发器。

梅利有限状态机

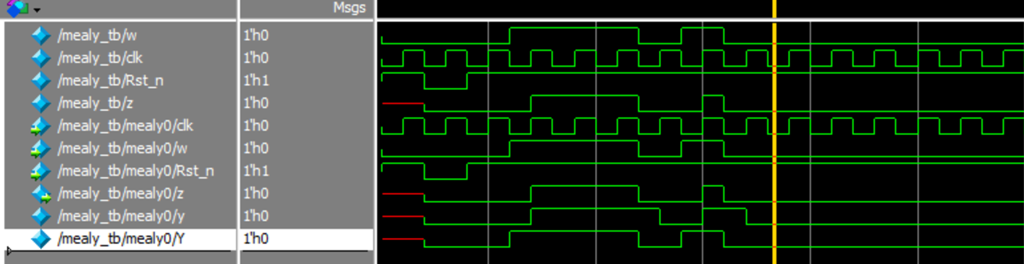

一个实际问题的描述:假设前面自动驾驶的例子中,我们做一个修改,第二次检测到w=1的相同的周期内,z=1。输入输出信号时序序列如下:

| 时钟周期 | t0 | t1 | t2 | t3 | t4 | t5 | t6 | t7 | t8 | t9 | t10 |

| w | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 1 |

| z | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 |

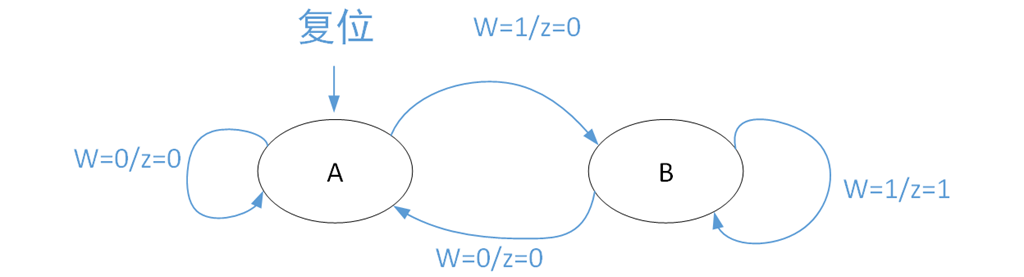

我们用状态机来描述该问题:首先有一个起始状态A,电路加载或复位后为该状态。假设当前为A状态,如果w=0,输出z=0,如果w=1,输出z=0,在下一个时钟周期边沿进入状态B;假设当前为B状态,如果w=0,输出z=0,在下一个时钟上升沿进入A状态,如果w=1,输出z=1,在下一个时钟上升沿,仍保持状态B。

状态图如下:

该状态机的状态表如下:

| 现在状态 | 下一状态 | 输出 z | ||

| w=0 | w=1 | w=0 | w=1 | |

| A | A | B | 0 | 0 |

| B | A | B | 1 | 1 |

状态分配表如下:

| 现在状态 | 下一状态 | 输出 z | |||

| w=0 | w=1 | w=0 | w=1 | ||

| y | Y | Y | z | z | |

| A | 0 | 0 | 1 | 0 | 0 |

| B | 1 | 0 | 1 | 0 | 1 |

Y的真值表:

| w/y | 0 | 1 |

| 0 | 0 | 0 |

| 1 | 1 | 1 |

z的真值表:

| w/y | 0 | 1 |

| 0 | 0 | 0 |

| 1 | 0 | 1 |

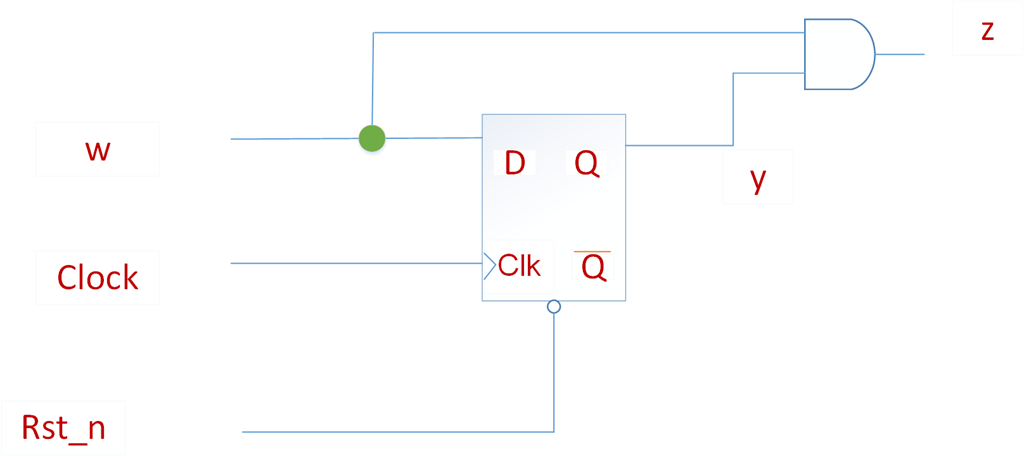

Y=w

z=wy

状态机的实现电路:

module mealy(clk, w, Rst_n, z); input clk; //时钟信号

input w;

input Rst_n; //复位信后

output reg z;

reg y, Y; //现在的状态 parameter A=1'b0,B=1'b1 ; always @(w,y)

begin

case(y)

A:

if(w==0)

begin

Y=A;

z=0;

end

else

begin

Y=B;

z=0;

end B:

if(w==0)

begin

Y=A;

z=0;

end

else

begin

Y=B;

z=1;

end

//default: Y=1'bx;

endcase end always @(posedge clk,negedge Rst_n)

begin

if(Rst_n==0)

y <= A;

else

y <= Y;

end endmodule

可以看到,相比moore型电路,mealy型电路更简单。另外从波形中,我们可以看到mealy型的电路输出z要比moore型早一个时钟周期。如果要得到和moore型一样时钟周期的输出,可以在mealy型实现电路上加一个触发器,打一拍,则可以得到和moore型一样的z输出时序。这时,mealy型也就转化成了对应的moore型电路。

verilog语法实例学习(11)的更多相关文章

- verilog语法实例学习(4)

Verilog模块 Verilog中代码描述的电路叫模块,模块具有以下的结构: module module_name[ (portname {, portname})]; //端口列表 [parame ...

- verilog语法实例学习(1)

本文档中通过verilog实例来学习verilog语法.Verilog是一种硬件描述语言,它具有并发性和时序性.并发性是指不同硬件模块的同时操作,时序性是指信号的赋值或操作在时钟的边沿进行.由于作者本 ...

- verilog语法实例学习(12)

verilog中的综合和不可综合总结 Verilog中综合的概念 综合就是EDA工具或者说综合工具把我们编写的verilog代码转化成具体电路的过程.Verilog中有很多语法,结构,过程,语句,有些 ...

- verilog语法实例学习(6)

函数和任务 函数 https://wenku.baidu.com/view/d31d1ba8dd3383c4bb4cd283.html verilog中函数的目的是允许代码写成模块的方式而不是定义独立 ...

- verilog语法实例学习(10)

常用的时序电路介绍 T触发器和JK触发器 在D触发器输入端添加一些简单的逻辑电路,可以生成另一种类型的存储元件.比如下图所示的T触发器.该电路有一个上升沿触发的触发器和两个与门,一个或门,以及一个反相 ...

- verilog语法实例学习(8)

常用的时序电路介绍 在电平敏感的锁存器时钟信号有效期(高电平)期间,锁存器的状态随着输入信号的变化而变化.有时候,我们需要存储器的状态在一个时钟周期只改变一次,这个时候就用到了触发器.触发器(flip ...

- verilog语法实例学习(5)

子电路模块 子电路模块的使用 一个verilog模块能够作为一个子电路包含在另一个模块中.采用这种方式,所有的模块都必须定义在一个文件中,那么verilog编译器就必须被告知每个模块的所属.模块例化的 ...

- verilog语法实例学习(3)

Verilog 操作运算符 算术运算符 +,-,*,/,**(加/减/乘/除/幂运算),乘法运算的结果的位宽是乘数和被乘数位宽的和. 在进行整数的除法运算时,结果要略去小数部分,只取整数部分:而进行取 ...

- verilog语法实例学习(2)

Verilog中的信号类型 线网类型 线网类型表示一个或多个门或者其它类型的信号源驱动的硬件连线.如果没有驱动源,则线网的默认值为z.verilog中定义的线网类型有以下几种: wire,tr ...

随机推荐

- OCM_第十七天课程:Section7 —》GI 及 ASM 安装配置 _管理和配置 GRID /实施 ASM 故障组 /创建 ACFS 文件系统

注:本文为原著(其内容来自 腾科教育培训课堂).阅读本文注意事项如下: 1:所有文章的转载请标注本文出处. 2:本文非本人不得用于商业用途.违者将承当相应法律责任. 3:该系列文章目录列表: 一:&l ...

- MarkDown常用语法及word转MarkDown

介绍 Markdown 的目标是实现「易读易写」. 可读性,无论如何,都是最重要的.一份使用 Markdown 格式撰写的文件应该可以直接以纯文本发布,并且看起来不会像是由许多标签或是格式指令所构成. ...

- 解决Oracle出现以0开头的小数,开头的0消失的问题

项目中碰到了个问题,本来报表需要显示“0.49%”,结果就是显示成“.49%” 找问题 首先在pl/sql工具里执行sql,发现原始的数据就是“.49%”,那么问题来了,原始sql的问题,跟工具无关了 ...

- C/S权限系统(一)

父窗体的代码: 扩展Enter键相当于Tab键的思路: 1.创建 窗体的父类2.在父类中重写Form中的ProcessCmdKey方法,在相关控件上按回车键相当于按了Tab 键3.让窗体继承新建的窗体 ...

- django url解析中的ResolverMatch

了解这个问题,源于昨天开发时遇到的一个小小的问题. 问题描述如下: 比如,我有一个url,定义如下: path('res_edit/<app>/<env>/', AppResE ...

- POJ 1742 Coins 【多重背包DP】

题意:有n种面额的硬币.面额.个数分别为A_i.C_i,求最多能搭配出几种不超过m的金额? 思路:dp[j]就是总数为j的价值是否已经有了这种方法,如果现在没有,那么我们就一个个硬币去尝试直到有,这种 ...

- bzoj3687

3687: 简单题 Time Limit: 10 Sec Memory Limit: 512 MBSubmit: 700 Solved: 319[Submit][Status][Discuss] ...

- 不同git仓库版本控制

场景: 我们有一个开源项目托管在github上面,现在打算在gitlab上进行私有托管开发,当适合发布一个版本的时候提交到github. Git合并特定commits 到另一个分支 实现如下: 1.获 ...

- asp.net core 2.0 cookie的使用

本文假设读者已经了解cookie的概念和作用,并且在传统的.net framework平台上使用过. cookie的使用方法和之前的相比也有所变化.之前是通过cookie的add.set.clear. ...

- Python3 - 基础知识、基本了解

一.Python到底是什么? (抄自 金角大王) 1. Python是一门解释型语言? 我初学Python时,听到的关于Python的第一句话就是,Python是一门解释性语言,我就这样一直相信下去, ...