外同步信号检测---verilog---状态机

外同步信号检测---verilog---状态机

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: chensimin

//

// Create Date: 2018/02/08 11:39:20

// Design Name:

// Module Name: signal_detect

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

////////////////////////////////////////////////////////////////////////////////// module signal_detect #

(

parameter TOTAL_TIME_CNT = ,

parameter THRESHOLD_VALUE = ,

parameter WIDTH =

)

(

input wire clk,

input wire rst,

input wire signal,

output wire signal_existence

); //--------------------------------------------------------------

外部信号边沿检测

reg signal_delay_1;

reg signal_delay_2;

wire signal_rise;

always @(posedge clk or posedge rst)

begin

if( rst )

begin

signal_delay_1 <= 'b0;

signal_delay_2 <= 'b0;

end

else

begin

signal_delay_1 <= signal;

signal_delay_2 <= signal_delay_1;

end

end assign signal_rise = !signal_delay_2 && signal_delay_1; //----------------------------------------------------------------

计数器1 用来在第一个状态计数

reg [ WIDTH- : ] time_cnt_1;

always @(posedge clk or posedge rst)

begin

if( rst )

time_cnt_1 <= ;

else if( time_cnt_1 < TOTAL_TIME_CNT - && current_state == 'b01)

time_cnt_1 <= time_cnt_1 + 'b1;

else

time_cnt_1 <= ;

end //----------------------------------------------------------------

计数器2 用来在第二个状态计数

reg [ WIDTH- : ] time_cnt_2;

always @(posedge clk or posedge rst)

begin

if( rst )

time_cnt_2 <= ;

else if( time_cnt_2 < TOTAL_TIME_CNT - && current_state == 'b10)

time_cnt_2 <= time_cnt_2 + 'b1;

else

time_cnt_2 <= ;

end //----------------------------------------------------------------

计算第一个状态下 signal_rise 的脉冲个数

reg [ WIDTH- : ] i;

always @(posedge clk or posedge rst)

begin

if( rst )

i <= ;

else if ( time_cnt_1 == )

i <= ;

else if( signal_rise && current_state == 'b01)

i <= i + 'b1;

end //----------------------------------------------------------------

计算第二个状态下 signal_rise 的脉冲个数

reg [ WIDTH- : ] j;

always @(posedge clk or posedge rst)

begin

if( rst )

j <= ;

else if ( time_cnt_2 == )

j <= ;

else if( signal_rise && current_state == 'b10)

j <= j + 'b1;

end //---------------------------------------------------------------- localparam NO_SIGNAL = 'b01;

localparam HAVE_SIGNAL = 'b10; reg [:]current_state;

reg [:]next_state;

always @ (posedge clk or posedge rst)

begin

if( rst )

current_state <= NO_SIGNAL;

else

current_state <= next_state;

end //--------------------------------------------------------------

状态机跳变条件:

1.在NO_SIGNAL状态下,先是在一定时间段内,数脉冲的个数,当脉冲的个数大于了某个阈值时,立刻判断为,外同步信号存在。

2.在HAVE_SIGNAL状态下,同样也是数脉冲的个数,当一段时间内,脉冲总数量小于某个阈值时,则判断为外同步信号丢失,状态跳转到NO_SIGNAL状态

always @(*)

begin

next_state = NO_SIGNAL;

case( current_state ) NO_SIGNAL:

begin

if( i >= THRESHOLD_VALUE )

next_state = HAVE_SIGNAL;

else

next_state = NO_SIGNAL;

end HAVE_SIGNAL:

begin

if( (time_cnt_2 == TOTAL_TIME_CNT - ) && j < THRESHOLD_VALUE )

next_state = NO_SIGNAL;

else

next_state = HAVE_SIGNAL;

end endcase

end //-------------------------------------------------------------

状态机输出信号驱动

reg signal_existence_r;

always @(posedge clk or posedge rst)

begin

if (rst)

begin

signal_existence_r <= 'b0;

end

else

begin case( current_state ) NO_SIGNAL:

begin

signal_existence_r <= 'b0;

end HAVE_SIGNAL:

begin

signal_existence_r <= 'b1;

end endcase end

end assign signal_existence = signal_existence_r; endmodule /* add_force {/signal_detect/clk} -radix hex {1 0ns} {0 50000ps} -repeat_every 100000ps

add_force {/signal_detect/rst} -radix hex {1 0ns} {0 150ns}

add_force {/signal_detect/signal} -radix hex {0 0ns} {1 300ns} {0 400ns} -repeat_every 500ns */

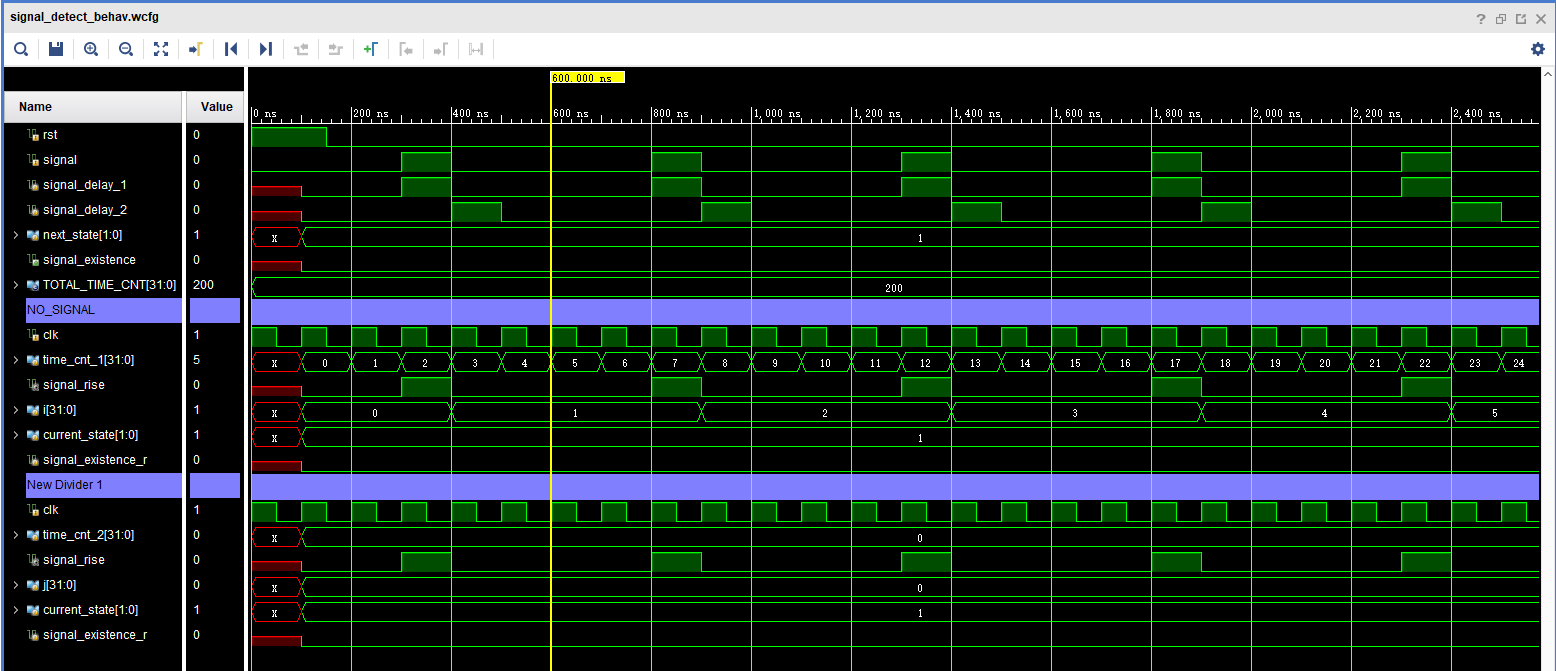

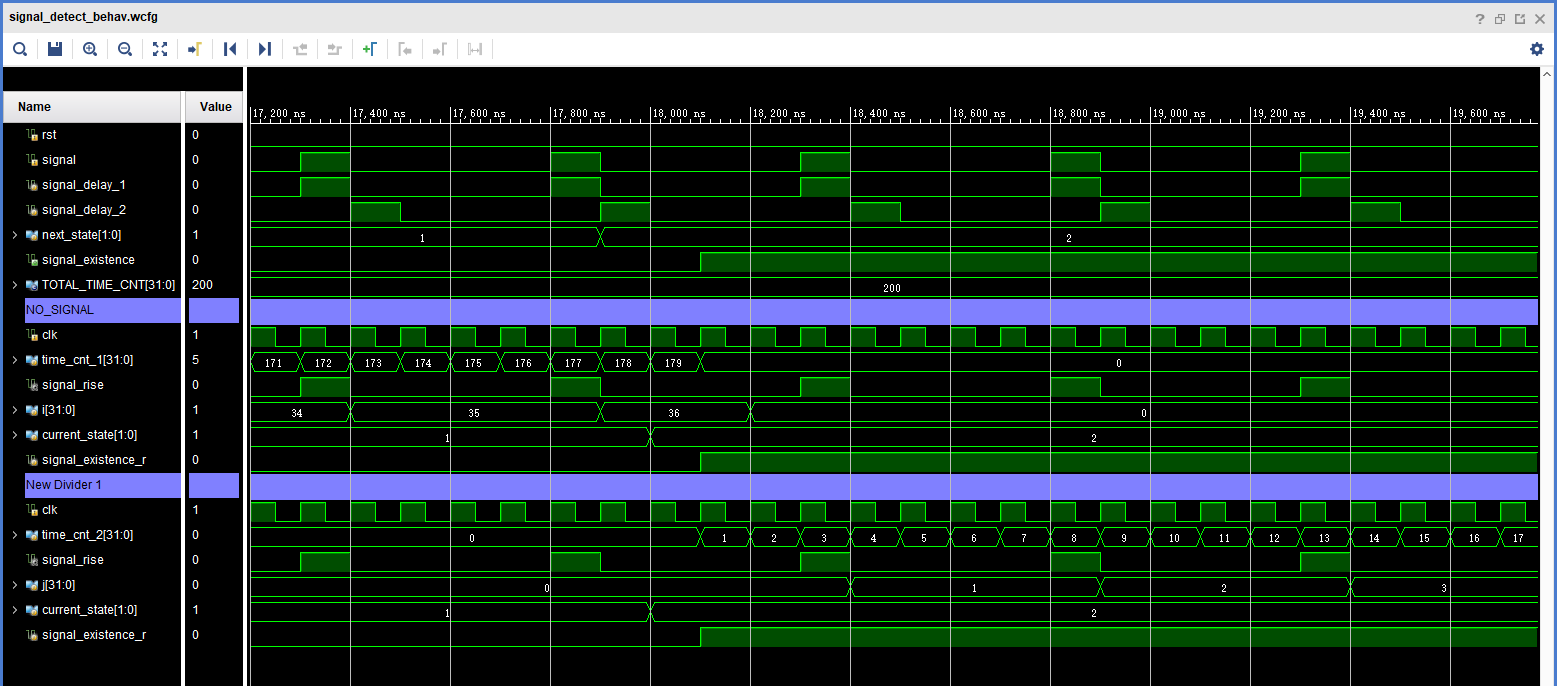

仿真波形:

1.

2.

3.

外同步信号检测---verilog---状态机的更多相关文章

- 视频外同步信号研究---fvh

视频外同步信号研究---fvh 一个时钟周期有两个edge,分别称为:(1)Leading edge=前一个边沿=第一个边沿,对于开始电压是1,那么就是1变成0的时候:对于开始电压是0,那么就是0变成 ...

- C# 同步 异步 回调 状态机 async await Demo

源码 https://gitee.com/s0611163/AsyncAwaitDemo 为什么会研究这个? 我们项目的客户端和服务端通信用的是WCF,我就想,能不能用异步的方式调用WCF服务呢?或者 ...

- Verilog状态机使用技巧

“没有什么难处是通过增加一个状态机不能够解决的,如果不行,那就俩..” 在实现某种功能时,若感觉该功能的各种可能状态间的切换太绕了,此时,增加一个状态机往往能使思路变得清晰,功能的实现也就简单明了了. ...

- Verilog状态机

以1011为例 代码如下: //1011(Meay型) module state1(clk,in,rst_n,out); input clk; input rst_n; input in; outpu ...

- (原创)Verilog三段式状态机

下面以上图一个简单的FSM说明三段式Verilog状态机范式: `timescale 1ns / 1ps module FSM( clk,rst_n, in1,in2, out1,out2, CS,N ...

- RSync实现文件备份同步详解

1.rsync简介 rsync是Unix下的一款应用软件,它能同步更新两处计算机的文件与目录,并适当利用差分编码以减少数据传输.rsync中一项与其他大部分类似程序或协议中所未见的重要特性是镜像对每个 ...

- linux高级技巧:rsync同步(一个)

1.rsync基本介绍 rsync这是Unix下的一款应用软件,它能同步更新两处计算机的文件与文件夹,并适当利用差分编码以降低数据传输.rsync中一项与其它大部分类似程序或协议中所未 ...

- 160407、java实现多线程同步

多线程就不说了,很好理解,同步就要说一下了.同步,指两个或两个以上随时间变化的量在变化过程中保持一定的相对关系.所以同步的关键是多个线程对象竞争同一个共享资源. 同步分为外同步和内同步.外同步就是在外 ...

- [笔记][FPGA]有限状态机FSM学习笔记(三)

0. 简介 在数电FPGA中,FSM是一个重要的部分,藉此可以完成一些复杂算法的硬件实现等.其中有关于FSM的写法按照always块的个数来划分,又分为一段式.两段式.三段式状态机.顾名思义,一段式就 ...

随机推荐

- Jsoup的学习

一 . 什么是jsoup jsoup 是一款Java 的HTML解析器,可直接解析某个URL地址.HTML文本内容.它提供了一套非常省力的API,可通过DOM,CSS以及类似于jQuery的操作方法来 ...

- 前端笔记 (3.JavaScript 2)

一般来说,js代码越来越庞大的时候,最好要把它存在一个js文件中, 通过src引入即可,这样具有维护性高,可缓存(加载一次,无需加载) 方便未来拓展的特性 正确写法: <script type= ...

- HDU1548- A strange lift (BFS入门)

题目传送门:http://acm.hdu.edu.cn/showproblem.php?pid=1548 A Strrange lift Time Limit: 2000/1000 MS (Java/ ...

- [转]How rival bots battled their way to poker supremacy

How rival bots battled their way to poker supremacy http://www.nature.com/news/how-rival-bots-battle ...

- 文件系统--fs(读)--fs.read

var fs = require('fs');var buf=new Buffer(1024);//fs.open(); //fs.open(path,flags,mode,callback);/* ...

- Java中的国际化

一.什么是国际化? 国际化是指应用程序运行时,可根据客户端请求来自的国家/地区.语言的不同而显示不同的界面. 二.Java如何实现国际化? Java程序的国际化思路是将程序中的标签.提示等信息放在资源 ...

- NOI-1.1-06-空格分隔输出-体验多个输入输出

06:空格分隔输出 总时间限制: 1000ms 内存限制: 65536kB 描述 读入一个字符,一个整数,一个单精度浮点数,一个双精度浮点数,然后按顺序输出它们,并且要求在他们之间用一个空格分隔. ...

- XXS level1

level1 (1)查看PHP源码,发现可以通过调用window,alert()完成任务 window.alert = function() { confirm("完成的不错!") ...

- soft-nms

https://blog.csdn.net/app_12062011/article/details/77963494 ----> NMS-非极大值抑制进行后处理. 通常的做法是将检测框按得分排 ...

- .net core 微服务架构-docker的部署-包括网关服务(Ocelot)+认证服务(IdentityServer4)+应用服务(asp.net core web api)

本文主要介绍通过Docker来部署通过.Net Core开发的微服务架构,部署的微服务主要包括统一网关(使用Ocelot开发).统一认证(IdentityServer4).应用服务(asp.net c ...