RTL 与 technology schematic的区别,包含概念与实例

2013-06-25 16:40:45

下面是xilinx官网上的问答贴:

http://china.xilinx.com/support/answers/41500.htm#solution

The difference between RTL and technology schematic

Description

After XST synthesis is completed, I am able to view both RTL and technology schematic.I frequently observe discrepancies between these two schematics.

What is the difference between them?

Solution

RTL View

Viewing an RTL schematic opens an NGR file that can be viewed as a gate-level schematic.

This schematic is generated after the HDL synthesis phase of the synthesis process. It shows a representation of the pre-optimized design in terms of generic symbols, such as adders, multipliers, counters, AND gates, and OR gates, that are independent of the targeted Xilinx device.

查看RTL schematic,将会打开NGR文件,该文件被看做门级的schematic。RTL schematic在synthesis过程的HDL synthesis phase之后产生,他是用通用的symbol表征的优化前的设计,比如 adders, multipliers, counters, AND gates, and OR gates,与目标器件是独立的。

Technology View

Viewing a Technology schematic opens an NGC file that can be viewed as an architecture-specific schematic.

This schematic is generated after the optimization and technology targeting phase of the synthesis process. It shows a representation of the design in terms of logic elements optimized to the target Xilinx device or "technology"; for example, in terms of of LUTs, carry logic, I/O buffers, and other technology-specific components. Viewing this schematic allows you to see a technology-level representation of your HDL optimized for a specific Xilinx architecture, which might help you discover design issues early in the design process.

You should always refer to technology schematic for synthesized result.

To disable RTL schematic generation to speed up synthesis, you can set XST property Generate RTL Schematic (-rtlview) to "No".

查看RTL schematic,将会打开NGC文件,该文件被看做基于结构的schematic。

该schematic在synthesis过程的optimization and technology targeting phase之后产生,该schematic示的是根据 Xilinx的device or "technology优化之后,用logic elements组成的schematic。例如,用 LUTs, carry logic, I/O buffers, and other technology-specific components。查看该schematic,可以看到杜宇一个特定的xilinx器件结构优化之后的technology-level的表示,这将帮助你在设计过程中尽早发现设计问题。

下面是网上找的一些看法:

rtl视图,其实就是寄存器级传输图,它在综合及布局布线前就生成了,并非设计的最终电路结构,是设计输入的最忠实的体现,它的主要作用是帮助设计者检查设计输入中的问题。就像是用XST综合的时候,有一个view rtl schematic和一个view technology schematic,区别是前者仅仅是语法分析得到的结构,是你的设计单纯的综合效果,可以帮助你理解你的算法;而后者才是放在FPGA中综合的效果,是用chipscope可以看到的,反映了实际的电路和资源使用情况。

RTL类似于你用原理图设计的形式,而后者就是后续要实现需要的ngc,fpga内部的一些基本单元组成的。

RTL Schematic仅仅是语法分析得的结果,Technology Schematic才是实际的结果,后者中能看到的就是你能在CHIPSCOPE里抓得到的。

rtl视图就是你的设计单纯的综合效果;技术视图是你的设计放在fpga中的综合效果!!!

RTL Viewer可以帮助你理解你设计的算法,Technology Viewer查看LUT的工作方式。

我的理解:

RTL Schematic

- 是gate-level的;

- 是用通用的symbol表征的优化前的设计,比如 adders, multipliers, counters, AND gates, and OR gates;

- 与目标器件是独立的;

- 在ISE中对应RTL Viewer的文件输入格式为NGR,也就是RTL Viewer通过NGR文件打开RTL Schematic。

Technology Schematic

- 是architecture-specific 的;

- 是根据 Xilinx的device or "technology优化之后,是综合后的,根据目标器件的结构优化后的,用logic elements组成的schematic。例如,用 LUTs, carry logic, I/O buffers, and other technology-specific components;

- 是基于所使用器件的结构的;

- 在ISE中对应RTL Viewer的文件输入格式为NGC,也就是RTL Viewer通过NGC文件打开TechnologySchematic。

另外,对于planahead,有:

- 在planahead中,没有 RTL Schematic 与Technology Schematic的概念,而是在不同的设计步骤有不同的schematic;

- 在RTL Design后,看到的schematic对应ISE中的RTL Schematic,RTL Design是综合之前的步骤;

- 在Netlist Design后,看到的schematic对应ISE中的Technology Schematic,Netlist Design是综合之后的步骤。

注:

- RTL Viewer是通过打开NGR或NGR文件来查看RTL Schematic 与Technology Schematic的,看到的Schematic不能保存,也没有对应的文件,如下面ISE help中对RTL Viewer的描述,是不产生输出文件的;

- 通过planahead可以将Schematic保存为pdf文件,具体方法见:http://www.cnblogs.com/youngforever/p/3151559.html

RTL Viewer Files

RTL Viewer works with the following files.

Input Files

NGR files are read as input. Xilinx® Synthesis Technology (XST) generates the NGR file from the register transfer level (RTL) netlist. RTL Viewer opens the NGR file, and you can select a block to view as a schematic.

Output Files

The RTL Viewer does not generate output files. It only allows you to view, not save, NGR files.

下面通过一个简单的例子对比RTL Schematic 与Technology Schematic。

代码:

写一个两级寄存器的例子,代码如下:

module block_nonblock(

clk,

a,

b,

c

); input clk;

input a; output b;

output c; reg b;

reg c; always@(posedge clk)

begin

b <= a;

c <= b;

end endmodule

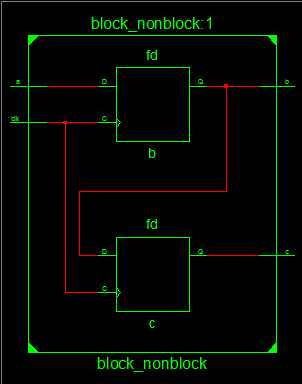

综合之后,RTL Schematic为:

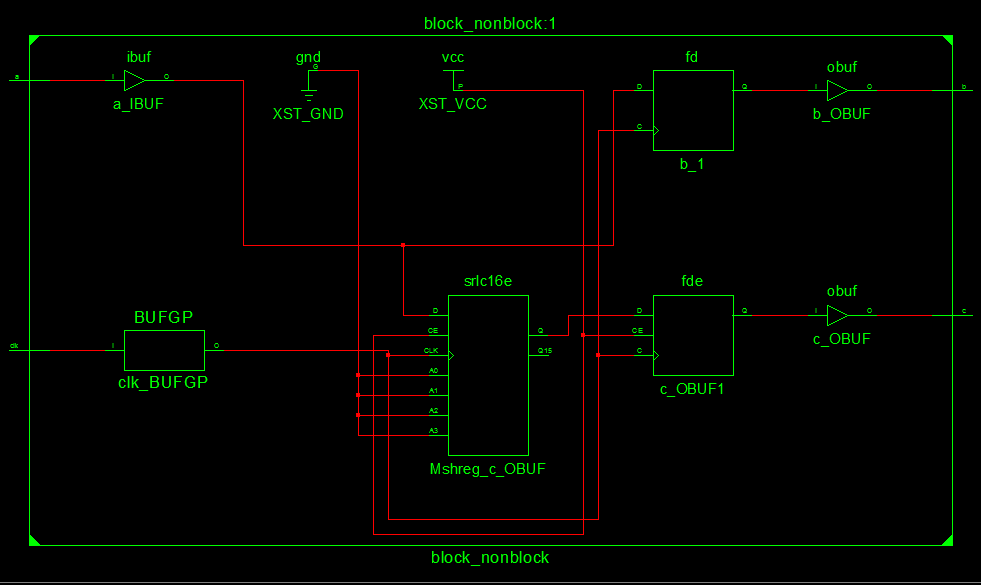

Technology Schematic为:

可以看到,RTL Schematic只是用两个D触发器表示设计,是用通用的符号表征的电路,在实际的FPGA电路中,仅有触发器肯定是不行的;而Technology Schematic则包含了输入缓冲ibuf、输出缓冲obuf等元件,是FPGA实际工作对应的的电路。

当然,上面这个例子很简单,但已经可以看出两者的区别了,对于复杂的设计这个区别应该更明显,此处不再赘述。

RTL 与 technology schematic的区别,包含概念与实例的更多相关文章

- Web开发中 MTV模式与MVC模式的区别 联系 概念

MTV 与 MVC模式的区别 联系 概念: MTV: 所谓MTV指的就是: M:model (模型),指的是ORM模型. T:template (模板),一般Python都是使用模板渲染的方式来把HT ...

- Javascript单例模式概念与实例

前言 和其他编程语言一样,Javascript同样拥有着很多种设计模式,比如单例模式.代理模式.观察者模式等,熟练运用Javascript的设计模式可以使我们的代码逻辑更加清晰,并且更加易于维护和重构 ...

- C#反射概念以及实例详解【转】

2009-08-28 13:12 佚名 互联网 我要评论(1) 字号:T | T C#反射概念以及实例向你介绍了C#反射的基本内容以及C#反射实例的简单应用,希望对你了解和学习C#反射以及C#反射实例 ...

- 【37】String,StringBuffer,StringBuilder区别和概念

基本的概念: 查看 API 会发现,String.StringBuffer.StringBuilder 都实现了 CharSequence 接口,内部都是用一个char数组实现,虽然它们都与字符串相关 ...

- Accounting_权责发生制和收付实现值的区别(概念)

2014-07-11 BaoXinjian

- http和https区别及概念

HTTP:是互联网上的应用广泛的一种网络协议,是一个客户端和服务器端请求和应答的传输协议,它可以使浏览器更加高效,使网络传输减少. HTTPS:是以安全为目标的HTTP通道,简单讲是HTTP的安全版, ...

- OAF_文件系列11_实现OAF读写Excel包JXL和POI的区别(概念)

20150803 Created By BaoXinjian

- AMD机制与cMD的区别和概念简要介绍

1.http://www.cnblogs.com/dojo-lzz/p/4707725.html 2.http://blog.chinaunix.net/uid-26672038-id-4112229 ...

- SQL Server 2008各版本介绍区别(包含企业版 开发者版 标准版 Web版 工作组版 Express版 Compact版)

SQL Server 2008分为SQL Server 2008企业版.标准版.工作组版.Web版.开发者版.Express版.Compact 3.5版,其功能和作用也各不相同,其中SQL Serve ...

随机推荐

- MySQ binlog三种模式

MySQ binlog三种模式及设置方法 1.1 Row Level 行模式 日志中会记录每一行数据被修改的形式,然后在slave端再对相同的数据进行修改 优点:在row level模式下,bin- ...

- spring 计划任务:cron表达式

Cron表达式是一个字符串,字符串以5或6个空格隔开,分开工6或7个域,每一个域代表一个含义,Cron有如下两种语法 格式: Seconds Minutes Hours DayofMonth Mont ...

- 【ASP.NET+MVC4+Web+编程】读书笔记

模型:数据和业务逻辑 视图:展示 控制器:接收视图输入数据,通过模型层业务逻辑处理后 返回给视图 分离关注点(模型 视图 控制器).惯例优先原则 browser-->routing-->c ...

- 玩转Slot Machine

最近在做一个有关Slot Machine小游戏的开发,其中遇到了不少的坑,现将个人遇到的问题总结如下,希望今后对大家开发的过程中有所的帮助. 这个项目是部署到微信朋友圈广告的,两天时间,PV就有14 ...

- 同时存在两个或多个homestead 虚拟box

开发中发现,不同版本的homestead 里面的环境各不相同,里面的node,npm等版本都不一致,如果需要添加 不同版本的homestead同时存在可以按照以下办法处理. tips: 提供可以离线下 ...

- JavaScript的语法要点 4 - 面向对象的基础

在传统的面向对象语言如C++.C#.Java中有类.对象.继承等概念.在JavaScript中又如何表示呢?JavaScript中没有class关键字,JavaScript中的类.对象.继承的概念是通 ...

- 解决 Chrome 浏览器自动调整小于11px字体的问题

不知道说是 Chrome 智能呢?还是说它多此一举?Chrome 浏览器中存在默认会自动将小于11px大小的字体调整为12px.我在写 BlueNight 主题的最新评论时候就设置了评论发布时间为11 ...

- TDBAdvGrid 只读状态下复制功能

DataSource1.AutoEdit := false;

- Spark Tungsten揭秘 Day3 内存分配和管理内幕

Spark Tungsten揭秘 Day3 内存分配和管理内幕 恭喜Spark2.0发布,今天会看一下2.0的源码. 今天会讲下Tungsten内存分配和管理的内幕.Tungsten想要工作,要有数据 ...

- Programming Collective Intelligence

最近正在拜读 O'reilly出版的Programming Collective Intelligence,准备研究研究搜索引擎了,童鞋们,到时候会考虑公布源码哦!