【ZYNQ学习】如何使用ZYNQ

本篇博客建立一套ZYNQ系统开发的一般方法和流程,并对ZYNQ的硬件和软件的设计流程进行概述

设计工具:

- vivado IDE:创建SoC设计中的硬件系统部分,同时和设计套件中的其他工具有交互,包含集成和打包IP的工具

- SDK:基于Eclipse平台开发的软件设计工具,使用c和c++语言且支持ARM和NEON扩展的GCC库

- vivado simulator:提供硬件描述语言的仿真环境

- vivado logic analyser:提供系统内验证的工具,例如一些包含在硬件设计里的特殊的核心,可以探测芯片行为并将捕捉的数据传回主机,然后在逻辑分析器上显示

- vivado serial I/O analyser:针对特定高速通信接口的仿真工具

- vivado high-level synthesis:从c语言描述来综合硬件的工具

- system generator for DSP:用于DSP设计的创建和仿真

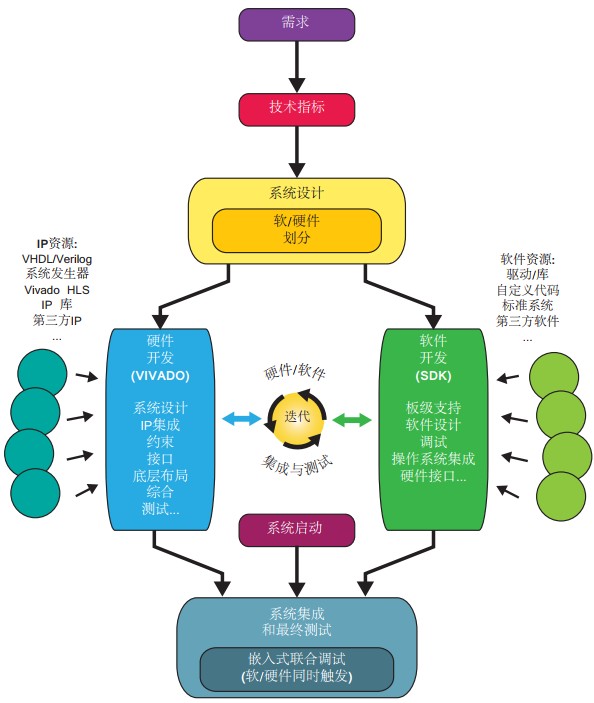

ZYNQ设计流程概述:

- 系统架构的设计通常采用自上而下的方法,即先定义顶层的接口和参数,再确定底层的子系统或功能

- 软件常常用来完成一些一般性的顺序执行的任务,比如操作系统、用户应用程序和图形界面,而偏向于数据流计算或者具有并行限制的软件算法适合在PL端实现,因此这也类似于"协处理器"模型,可以把处理器从那些重在计算且具有并行性的任务中解放出来改为硬件处理,从而从整体上提升性能

- ZYNQ的一个特别的优势就是处理器和可编程逻辑之间的强耦合,在PS和PL之间以低延时、高性能的AXI连接,在通信开销上有大量减少

- 通常以vivado IDE作为设计起点,在顶层设计的创建过程中起到"驾驶舱"的作用,套件内工具和其他部分(特别是system generator和vivado HLS)的集成支持多种功能不同的子系统,当硬件设计完成后,就会被导入到SDK进行软件开发,还可以在SDK和vivado IDE之间进行设计的迭代

硬件开发与测试

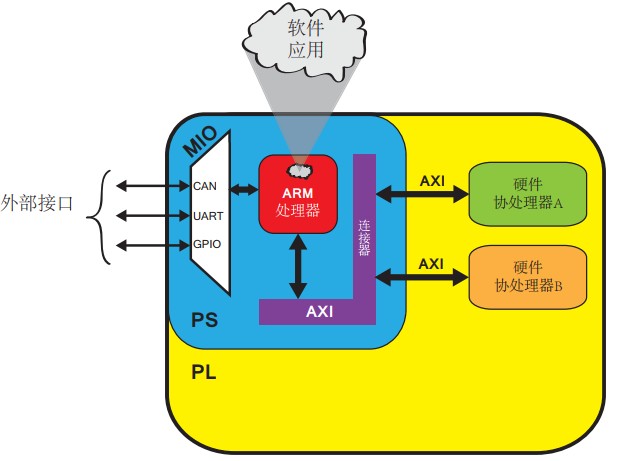

硬件系统开发包括在PL上设计和实现的外部模块和其他逻辑单元,在这些模块和PS之间创建合适的连接,以及恰当的配置PS,比如一个硬件系统可能包括CAN总线接口、一个调试用的UART接口以及GPIO,这些协处理器一起支持软件在ARM上的运行:

硬件系统开发由vivado IDE套件承担,用户可以从IP库(IP Integrator)中选出模块来组成所期望的系统框图,配置模块参数,以及设计合适的内部连接和外部接口

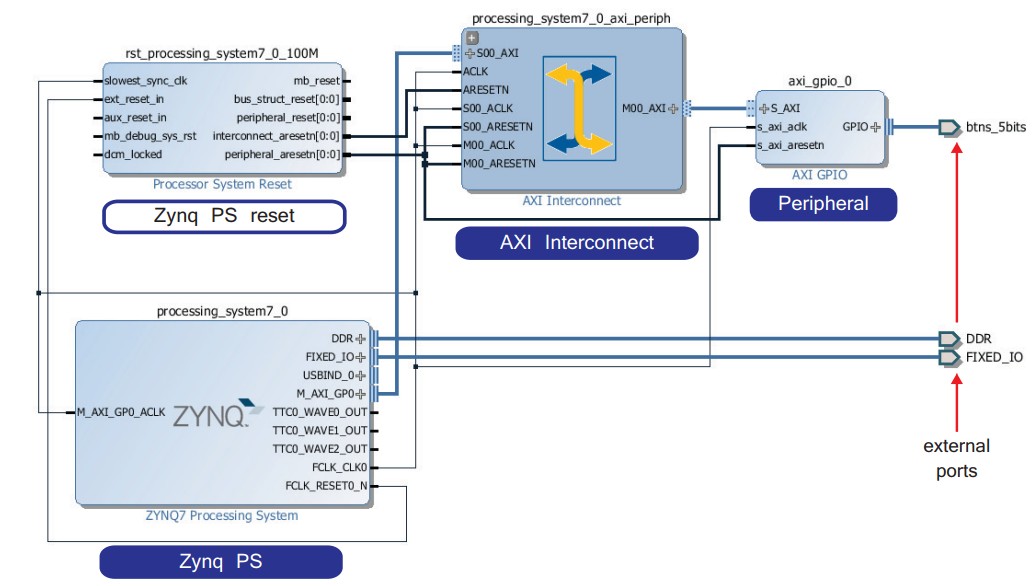

以下是在IP Integrator设计中的示例:

其中可以看到PS模块、PS复位模块、外设和AXI互联模块,在这些模块之间主要通过AXI接口连接

软件开发与测试

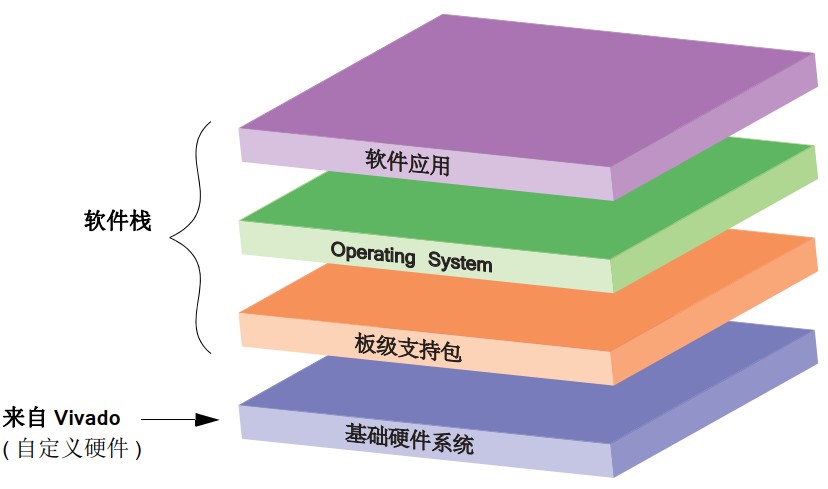

从vivado中导出到SDK的是为软件平台定制的硬件,称为基础硬件系统,对应在IP Integrator中的配置

软件系统可以被认为是建立在基础硬件系统上的一个栈:

在基础硬件系统上一层的是板级支持包(BSP),提供底层的驱动和函数供上一层(操作系统)使用和硬件通信,软件应用程序运行于操作系统之上,不过软件也可以直接和硬件通信,即裸机应用,且由于是双核架构,也可以部署两个不同的操作系统,每一个使用一个核心

- BSP会针对硬件系统进行调整,BSP是为基础硬件系统和操作系统之间的连接定制的,包括硬件参数,设备驱动以及底层操作系统函数,SDK提供了创建BSP以及开发测试上层软件的环境

- 在测试阶段,SDK包含Xilinx microprocessor debugger(XMD)和system debugger(TCF)工具,可以在硬件平台运行时测试软件的功能,通过使用比特流(.bit)文件烧写ZYNQ的PL端和在PS端运行软件(.elf文件)完成;GDB调试器(建立在XMD上)是一种更加高级的完成远程调试的方法;还可以使用vivado simulator在PC端上复现PL端

以IP为重点的系统级设计

- IP Integrator

- IP Packager:使IP被打包成标准包(基于IP-XACT标准)

Tool Command Language(TCL)脚本语言

阅读Xilinx的文档

在设计中如果有些不能确定的地方,Xilinx官方的文档往往可以解答我们的疑惑,下面就来谈谈如何使用这些文档

首先我们从哪里获得这些文档:

- DocNav

- Xilinx官网

其次如何阅读这些文档,应当选择一本贴合自己当前设计的文档,然后以这个文档内的一些别的补充文档的链接获取别的一些知识,从而构建起知识树

一些推荐的文档:

ug1137 zynqmpsoc swdev guide

ug1209 embedded design tutorial

ug1085 zynq trm (Technicial Reference)

ds891 overview data sheet

ug1228 embedded design methodology guide

ug1144 petalinux

ug1157 petalinux-tools

ug1169 qemu

ug1208 XSCT(xilinx sw command line tool) for tcl

ug1283 bootgen user guide

ug903:介绍了如何在vivado中使用约束文件

【ZYNQ学习】如何使用ZYNQ的更多相关文章

- ZYNQ学习之二-EMIO

---恢复内容开始--- 本次试验学习和掌握zynq的emio的使用,是通过PS控制PL端的GPIO. 1.创建硬件工程,主要就是添加EMIO就可以.当然了创建工程的时候还要注意DDR的设置,根据自己 ...

- MiZ702学习笔记13——ZYNQ通过AXI-Lite与PL交互

在<MiZ702学习笔记7——尝试自制带总线IP>,我曾提到了AXI4-Lite的简单用法,驱动了下流水灯,只涉及到了写总线.今天,我想利用之前的VGA模块,将AXI4-Lite的读写都应 ...

- 【原创】ZYNQ学习笔记(一) HelloWorld实现

拿过ZYNQ开发板,里面给了很多部件,果断从网上下载了手册,N多手册和原理图. 要比Spartan-6复杂多了,耐心地看了看,知道ZYNQ系列分为PS(系统)以及PL(逻辑)部分. 之前,自己一直在做 ...

- Zynq学习笔记(1)——Hellow World

Zynq是一款SOC芯片,之前只是用了PL(Programmable Logic)部分,而Zynq最突出的功能,就是内部的双核Cortex-A9,所以从现在开始我将学习ZYNQ的SOC学习(PS部分) ...

- zynq学习01 新建一个Helloworld工程

1,好早买了块FPGA板,zynq 7010 .终极目标是完成相机图像采集及处理.一个Window C++程序猿才开始学FPGA,一个小菜鸟,准备转行. 2,关于这块板,卖家的官方资料学起来没劲.推荐 ...

- ZYNQ学习之路1. Linux最小系统构建

https://blog.csdn.net/u010580016/article/details/80430138?utm_source=blogxgwz1 开发环境:window10, vivado ...

- zedboard zynq 学习 sobel 边缘检测 IP核 制作 根据 文档 Xapp890

官方文档http://www.xilinx.com/support/documentation/application_notes/xapp890-zynq-sobel-vivado-hls.pdf ...

- ZYNQ学习之——MIO

1.GPIO基础知识 Zynq7000 系列芯片有 54 个 MIO(multiuse I/O) ,它们分配在 GPIO 的 Bank0 和Bank1 隶属于 PS 部分, 这些 IO 与 PS 直接 ...

- Zynq学习笔记(1)

做硬件的第一个实例,一般当然是LED点灯啦~ 硬件:ZedBoard 软件:ISE 14.7 1.新建工程 2.选择平台 3.新建完成后,输入如下代码: `timescale 1ns / 1ps // ...

- 驱动学习5: zynq实现点亮led

驱动代码: #include <linux/module.h> #include <linux/kernel.h> #include <linux/fs.h> #i ...

随机推荐

- ifconfig查询的时候,只有lo网卡,没有ens33网卡

问题ifconfig查询的时候,只有lo网卡,但是ifconfig -a查询的时候却有ens33网卡ls /etc/syconfig/network-scripts/查找所有网卡配置信息文件的时候,没 ...

- leetcode刷题(三)

1.图论 找到小镇的法官 在一个小镇里,按从 1 到 N 标记了 N 个人.传言称,这些人中有一个是小镇上的秘密法官. 如果小镇的法官真的存在,那么: 小镇的法官不相信任何人.每个人(除了小镇法官外) ...

- DotNetCore2.1使用GitLab通过阿里云自动构建镜像上传阿里云仓库在Docker运行

操作步骤: 1.安装GitLab并添加项目(此处省略安装过程) 2.获取GitLab的Access Tokens 3.创建空的DotNetCore2.1 Api项目 4.项目添加Docker支持,文件 ...

- Vuforial 使用小计

1. 在使用扫图功能的时候, 上传图片审核处,要根据图片真实的宽度尺寸设置宽度. 2.做物体识别时,识别的物体最好是一个长方体或正方体,这样识别度高一些. 3.如果是其它物体识别要保证物体大一些,身体 ...

- Kubernetes 设置master相关

设置master调度命令 1.设置master一般情况下不接受pod调度 sudo kubectl taint nodes master node-role.kubernetes.io/master= ...

- flex_bison

flex_bison flex flex词法分析器,可以利用正则表达式来生成匹配相应字符串的C语言代码,其语法格式基本同Lex相同.单词的描述称为模式(Lexical Pattern),模式一般用正规 ...

- idea等工具网盘下载地址

1.idea2020 下载地址:https://caiyun.139.com/m/i?1E5C2SkIZbJH4 ,下载密码微信 搜索 "白菜拼吧" 回复 idea2020 获取 ...

- 使用tkinter开发的一款登录和注册图形化界面

目录 项目介绍 登录功能 登录界面展示 登录主要功能 登录部分源码 注册功能 注册界面展示 注册主要功能 注册部分源码 源码地址 项目介绍 使用tkinter开发的一款登录和注册图形化界面 使用tki ...

- vue3 门户网站搭建5-图标

奈何 element 自带的图标太少,不够用,故打算使用 vite-plugin-svg-icons 组件来封装 svg-icon . ps: ui 框架选用的 element-ui,为了能跟 vue ...

- 性能测试-top-实时显示系统中各个进程的资源占用状况, 也可以查看线程

1.top命令介绍 top命令是Linux系统中常用的性能分析工具,可以实时地查看系统的运行情况,比如内存.CPU.负载以及各个进程的资源占用情况 top界面主要分为两个部分,前5行展示的是系统的整体 ...