SRAM 测试总结

SoC随着工艺进步设计复杂度增加,embeded sram也越来越多。在40nm SoC产品Sram一般在20Mbits左右,当工艺发展到28nm时Sram就增加到100Mbits。如果考虑AI产品,Sram估计更多。如何更好的测试Sram就成为量产测试的重中之重。

Sram的结构

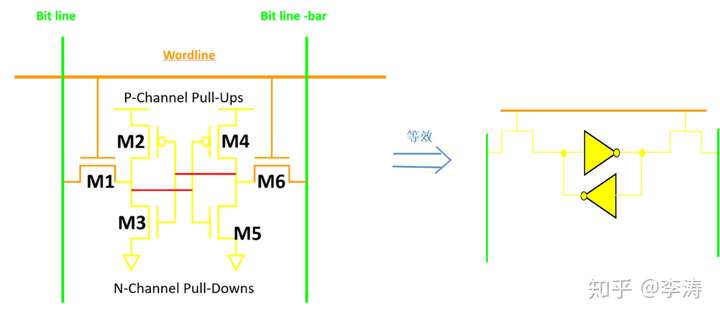

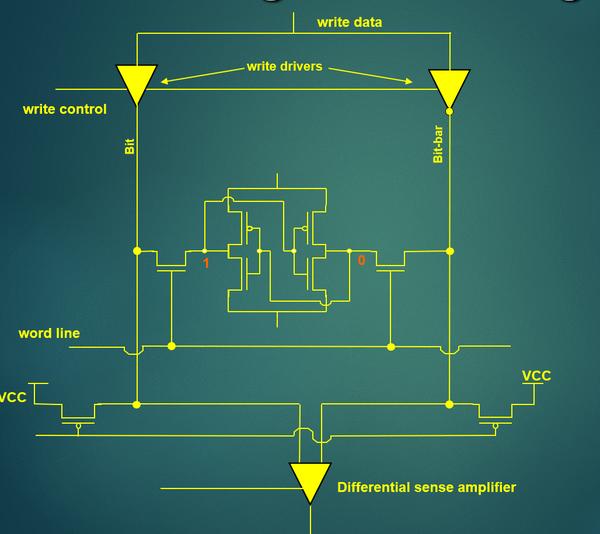

一个6T sram cell的经典结构如图所示:

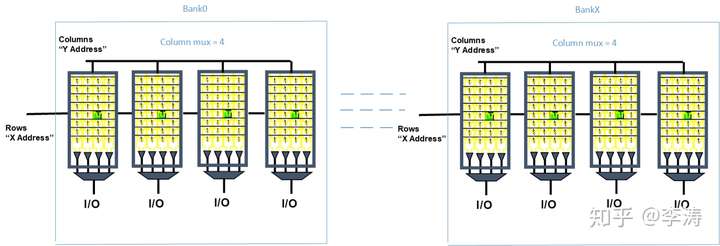

这些Sram cell集合成如下图的多个bank的memory block,每个bank有bank address使能;在一个bank内Row address选择一个完整的wordline,Column address选择某组IO bitlines。

举个例子说明如下:

一个memory block是4096x32 cm16,该memory size = 4096*32= 128k bits, row address is 8bits (4096/16 = 256 wordlines), column address is 4 bits(0~15), Wordline bits = 32*16 = 512 bits.

SRAM的性能

- memory compiler的选择

对于一个memory size大小确定的memory block,Column Mux越大,Row address位宽越小:

- memory读写的访问速度就高 (row译码选择快)

- memory的面积大(cell和cell的横向距离大于纵向距离,column mux增加很增加bits per wordline--横向,减少wordline数--纵向,横向尺寸增加远大于纵向)

- 因为一次选择的row地址对应的cell多,功耗也会增加

- 电流功耗

总电流功耗包括dynamic power和leakage power。不同的sram cell单元(比如HPC,HDC等等)功耗指标不同,体系结构设计需要在面积,速度和功耗之间寻找平衡。

-leakage current是永远存在的

Poweroff模式(cell+periphery off)< Retention模式(cell ON+periphery OFF) < Standby模式(cell+periphery on)

1Mbits memory的standby/Ret leakage电流在0.2mA左右,poweroff leakage电流在0.03mA左右。

-dynamic current:column mux,读写速度,读写辅助电路等都会影响动态电流

如果在常温状态下leakage current比较大,在高温或者大的dynamic current时必须注意thermal runaway的风险,因为温度升高leakage current会增加很快,总功耗的增加会进一步增加温度,形成正反馈。

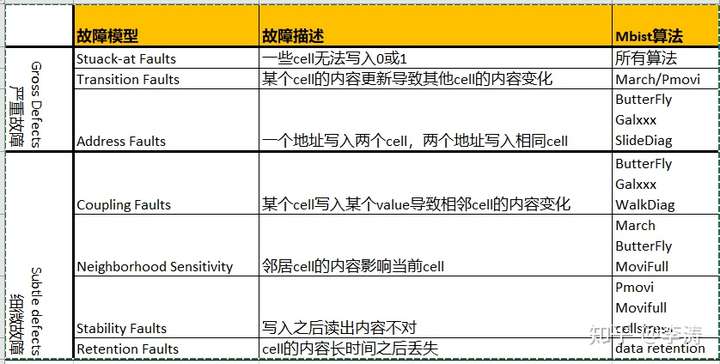

Sram的fault mode

可以将Sram的故障分类成以下几种,mbist的算法实质就是针对这些不同故障模型设计读写序列捕获可能的defects。

SRAM Read/Write Assist(RAWA)

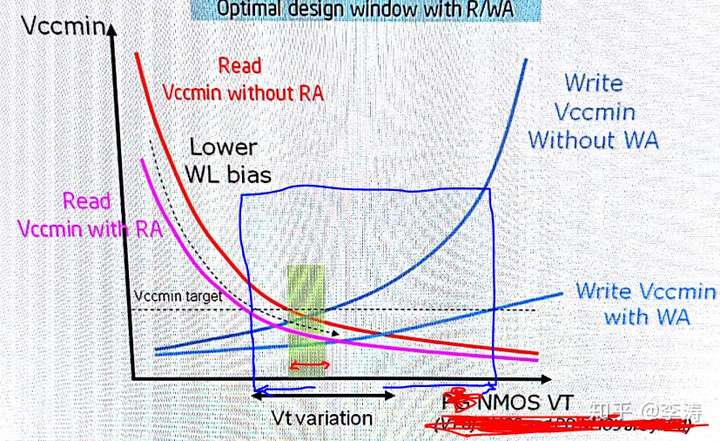

随着Sram的供电电压Vsram越来越低,Sram门单元参数的漂移越来约大,很难找到可以保证read和write都工作的Vsram电压了。

以下图为例,Vccmin的target是设死的,如果没有RAWA则NMOS的Vt必须保证在很小范围内,半导体工艺很难保证参数有这么小的范围;而如果有RAWA,则NMOS的Vt就可以有比较大的范围,减少了对工艺加工的要求。

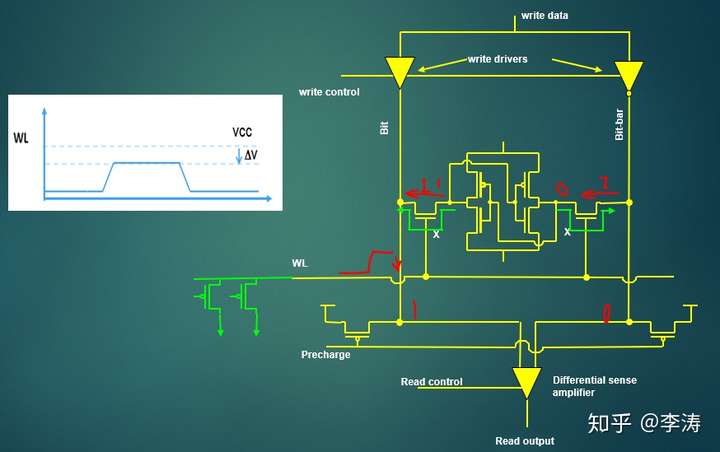

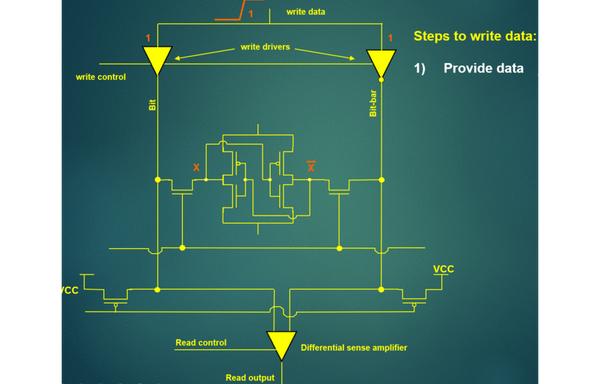

- Sram的读操作如下面gif所示,有Precharge->Select Wordline->Sense Amplifer strobe

其中select wordline的电压会影响pass gate的电流,wordline电压越高,pass gate的电流越大,cell的内容就越容易丢失。

- read assist 就是减少wordline的select电压,减少pass gate的电流减少对cell的disturb

- Sram write和WRA

Sram写入时降低Vsram的电压,可以帮助数据通过M2/M4写入cell中。

SRAM的Quality和Reliability

理论上如果SRAM支持redundancy repair + ECC,在测试的时候做到以下几点:

- 合理的算法覆盖故障模型 (比如PMOVI)

- 使用较低的low Vmin做repair(再低就无法repair)

- 在Vmin+Guardband电压下使用该SRAM,并且ECC on

基本可以保证SRAM没有yield loss和in field reliability的问题。

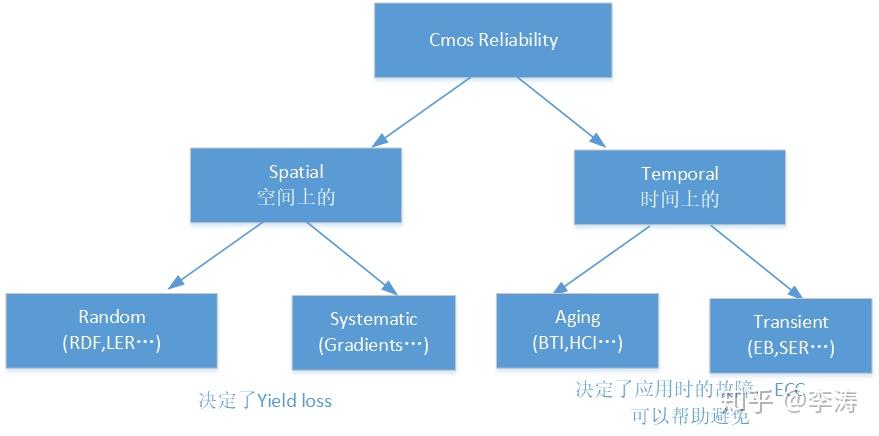

Cmos的reliability按照类型可以分为空间上和时间上的:

空间上的是process引起的yield loss,只能靠repair提高yield;

时间上的是由aging,Erratic bit,Soft Error rate等因素引起的使用故障,Ecc可以消除很多问题,或者提高使用电压可以帮助;

- Erratic bit导致Pass Vmin 波动很大,如果repeat测试很多遍,可以看到Vmin range在100mV左右。这个会导致Sram repair之后,需要一个比较大的Guardband保证Sram没有Erratic bit 问题;

- Aging会导致Vth随使用时间变大,5年以后一般会增大40mV,因此Vmin也会增加;

因此如果要保证DUT可以使用5年,在T0测试的时候就要用更低的Vscreen,保证足够的aging和EB的guardband。

可见SRAM的reliability是和operation voltage密切相关的,对于mobile应用关心power KPI,一般SRAM会工作在较低电压,SRAM reliability问题就更突出。需要ATE测试可以尽量在更低电压下repair memory,保证T0的pass Vmin比较低,和operation voltage相比有较大的guardband。

SRAM的repair

一般分为Word repair,row repair和column repair。Word repair使用寄存器存储defect cell的地址和数据,scan可以cover这些寄存器;row/column repair需要考虑BIST覆盖问题,在不同温度多次repair时redundancy cells的screen问题。

在量产测试中repair的电压选择也是一个balance的结果,repair voltage应该比target screen电压要低一些(考虑erratic bits的影响),保证把尽量多的weak cells可以替换掉,同时又不能导致太多DUT无法repair

Sram的Stress

为了消除早期失效DUT,SRAM一般需要在量产测试时做高电压的stress。这里有两个考量点:

- voltage和stress time:需要和subcon process确定,电压越高/测试温度高相应stress的时间就可以减少;

- stress pattern的选择:需要考虑如何保证stress pattern有效执行;另外使用什么mbist algorithm也是问题,一般建议使用write1->read1->write0->read0的pattern。优点是保证每个cell都有0<->1的翻转,同时cell在‘0’或者‘1’状态下有同样的stress时间。如果使用其他algorithm,有可能small sram有很长的static stress时间而big sram大多是toggling stress时间。

Sram的其他特性

SRAM的读写时间可以做成self-timing,当读写被时钟上升沿trigger以后,SRAM内有dummy bitline+dummy driver来驱动计时器得到读写的时间。得到读写时间后,用该时间访问实际sram cell保证读写时间ok。

SRAM 测试总结的更多相关文章

- STM32之SRAM调试

在学习STM32的时候,由于烧FLASH的所造成的时间会比较慢,而在SRAM中调试的时间会比FLASH快很多,再加上FLASH的时候会经常擦除芯片,会对芯片的寿命造成一定的影响, 其实我本人觉得在学习 ...

- SDRAM,DRAM,SRAM,DDR的概念

一:SDRAM SDRAM(Synchronous Dynamic Random Access Memory),同步动态随机存储器,同步是指 Memory工作需要同步时钟,内部的命令的发送与数据的传输 ...

- RAM,SRAM,DRAM,SDRAM,DDR RAM,ROM,PROM,EPROM,EEPROM,NAND FLASH,NOR FLASH的区别

RAM:由字面意思就可以理解,SDRAM SRAM DRAM(下面蓝色字体的这几种)都可以统称RAM,random access memory(随机存取存储器)的缩写,下面是51hei.com为大家整 ...

- [转]h5页面测试总结

转自http://www.blogjava.net/qileilove/archive/2014/07/24/416154.html?utm_source=tuicool H5页面测试总结 其实经过几 ...

- 异步SRAM控制器的Verilog建模

前言:sram顾名思义静态随机存储器,分为asram异步型和ssram同步型.这里驱动DE2上一块ISSI公司的512KB的asram. 设计思路:因为实际应用中单字节读写效率不高,所以本设计中仿照s ...

- SRAM的读写操作

自己写的SRAM的程序,主要在于实用性,适应工作的工程需要.使用芯片为: 芯片时序图为: 代码: /********************************Copyright********* ...

- 【iCore2双核心板】SRAM 读写实验(基于Verilog语言)

_____________________________________ 深入交流QQ群: A: 204255896(1000人超级群,可加入) B: 165201798(500人超级群,满员) C ...

- JMeter基于http请求的web接口性能测试总结

[本文出自天外归云的博客园] 基于http请求的web接口性能测试总结 压测的目的:对于Web接口压测的目的最终是要在对数据库造成压力的情况下观察压测服务器的cpu是否达到预警值.memory是否发生 ...

- ROM、RAM、DRAM、SRAM和FLASH区别

ROM和RAM指的都是半导体存储器,ROM是Read Only Memory的缩写,RAM是Random Access Memory的缩写. ROM在系统停止供电的时候仍然可以保持数据,而RAM通常都 ...

- 名词解释:DRAM, SRAM, SDRAM等

SRAM:静态RAM,不用刷新,速度可以非常快,像CPU内部的cache,都是静态RAM,缺点是一个内存单元需要的晶体管数量多,因而价格昂贵,容量不大. DRAM:动态RAM,需要刷新,容量大. SD ...

随机推荐

- css 多行文本展开收起

<template> <div class="content"> <div :class="[isOpen ? 'text' : 'text ...

- 复制文件到U盘提示“一个意外错误使您无法复制该文件”处理办法

运行cmd 运行 chkdsk H(U盘所在盘符):/f 即可

- Ansys-CHEMKIN-pro表面反应机制输入(Surface Kinetics Input)规则

chemkin表面反应机制文件(Ansys-CHEMKIN-pro表面反应机制输入) 1. 文件包含表面活性位(相).表面组分,固相组分.固相,热力学数据,反应机制: 2. 顺序:物质名称,活性位数据 ...

- binom_test

bt <- function(a, b, p = 0.5) {binom.test(a, b+a, 0.5, alternative= c("two.sided"), con ...

- python读书笔记-网页制作

socket()函数 Python 中,我们用 socket()函数来创建套接字,语法格式如下: Socket 对象(内建)方法 Python Internet 模块:

- Rename a Local and Remote Git Branch

Renaming Git Branch Follow the steps below to rename a Local and Remote Git Branch: 01 Start by swit ...

- 上位机-串口通信详解(以RS232为例))

1.什么是串口通信? 写这个的时候我在想应该怎么解释串口通信,因为串口通信很多朋友不了解的原因是涉及到硬件的知识,对于没有相关专业知识的朋友很难理解串口通信.所以我这里只做部分的解释,需要了解更多硬件 ...

- 使用react-vite-antd,修改antd主题,报错 [vite] Internal server error: Inline JavaScript is not enabled. Is it set in your options? It is hacky way to make this function will be compiled preferentially by less

一般报错 在官方文档中,没有关于vite中如何使用自定义主题的相关配置,经过查阅 1.安装less yarn add less (已经安装了就不必再安装) 2.首先将App.css改成App.les ...

- Linux 基础命令2

一.输出重定向命令 : > />> 1.ls > 1.txt 把命令返回的结果输出到文件中,会覆盖之前的数据,默认情况命令返回的结果显示在屏幕中: 2.Ls >1.txt ...

- .net core 使用 Nlog 集成 exceptionless 配置文件

nlog.config文件 安装nuget包: NLog.Web.AspNetCore Exceptionless.NLog 配置文件开始 <?xml version="1.0&quo ...