JK触发器与模12计数器

JK触发器

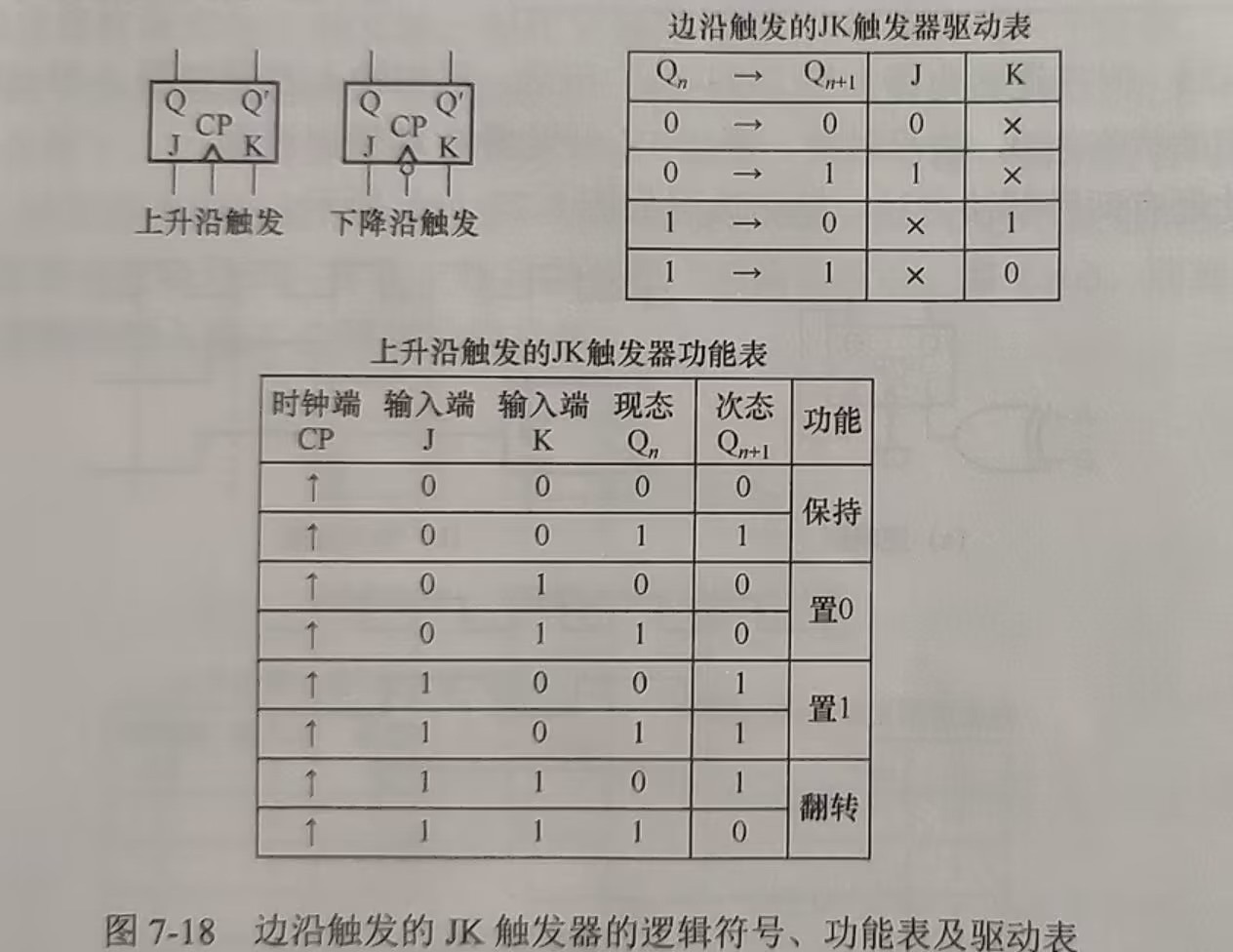

JK触发器具有保持,置0,置1和翻转四个功能。

则可得出次态方程:\(Q_{n+1} = JQ_n'+K'Q_n\)

Design

`timescale 1ns / 1ps

module jk(clk,Reset,Set,J,K,Q);

input clk;

input Reset;

input Set;

input J;

input K;

output Q;

reg q;

always@(posedge clk)

if(!Reset)

begin

q <= 1'b0;

end

else if(!Set)

begin

q <= 1'b1;

end

else

begin

case({J,K})

2'b00 : q <= q;

2'b01 : q <= 0;

2'b10 : q <= 1;

default : q <= ~q;

endcase

end

assign Q=q;

endmodule

Simulation

`timescale 1ns / 1ps

module JK_sim();

reg Reset, Set, clk;

wire Q;

reg J, K;

jk uu(clk, Reset, Set, J, K, Q);

initial

begin

Reset = 0;

Set = 0;

clk = 1;

J = 0;

K = 0;

#40 Reset = 1;

#40 Set = 1;

end

always #20{J, K} = {J, K} + 1;

always #10 clk = ~clk;

endmodule

波形图

模12计数器

需要使用4个JK触发器,卡诺图化简后得到触发器控制函数的最简与或式如下:

\(J_1 = K_1 = 1\)

\(J_2 = K_2 = Y_1^{n}\)

\(J_3 = (Y_4^n)'Y_2^nY_1^n\)

\(K_3 = Y_2^nY_1^n\)

\(J_4 = Y_3^nY_2^nY_1^n\)

\(K_4=Y_2^nY_1^n\)

Design

`timescale 1ns / 1ps

module count(Reset,Set,clk,Y);

input Reset;

input Set;

input clk;

output [3:0]Y;

wire j1,j2,j3,j4,k1,k2,k3,k4;

assign j1 = 1;

assign k1 = 1;

assign j2 = Y[0];

assign k2 = Y[0];

assign j3 = (~Y[3])&Y[1]&Y[0];

assign k3 = Y[0]&Y[1];

assign j4 = Y[0]&Y[1]&Y[2];

assign k4 = Y[0]&Y[1];

jk_0 u1 (clk,Reset,Set,j1,k1,Y[0]);

jk_0 u2 (clk,Reset,Set,j2,k2,Y[1]);

jk_0 u3 (clk,Reset,Set,j3,k3,Y[2]);

jk_0 u4 (clk,Reset,Set,j4,k4,Y[3]);

endmodule

Simulation

`timescale 1ns / 1ps

module sim_dev1();

reg Reset,Set,clk;

wire [3:0]Y;

initial

begin

Reset = 0;

Set = 0;

clk = 1;

#20 Reset = 1;

#20 Set = 1;

end

always#20 clk = ~clk;

CNT12 u(Reset,Set,clk,Y);

endmodule

波形图

vivado使用JK触发器IP核来实现计数器

新建JK触发器项目。

新建Design Sources。

将前面JK触发器的代码粘贴进去。

点击Tools,点击Create and package new IP。

Next,选择Package your current project,Next,复制一下IP核的位置。

退出当前项目,新建计数器项目。

点击Settings,再点开IP,点击Repository。

点击加号,粘贴刚刚复制的路径。

然后点击Select,OK。

现在点击PROJECT MANAGER 中的IP Catalog。

看到我们刚刚添加的IP核了。

- 双击这个IP核,弹窗点击OK,再OK,点击Generate生成。

- 现在实现计数器,粘贴我们刚刚的代码。记得JK触发器的名字要改为和刚刚生成的IP核的名字一样(一般默认是 {name}_0 )。

- 完成,可以试试模型仿真。

JK触发器与模12计数器的更多相关文章

- [FPGA]Verilog实现JK触发器组成的8421BCD码十进制计数器

目录 概述 电路分析 代码实现 参考文献 概述 本文以异步时序计数器为例,用Verilog实现以\(JK\)触发器组成的8421BCD码十进制异步计数器,并用ModelSim软件进行仿真验证. 电路分 ...

- SR触发器和JK触发器

SR触发器(电平触发器) 基本RS触发器的逻辑方程为:Q(n+1)=一S+RQ(n); 约束方程:R+S=1; 根据上述两个式子得到它的四种输入与输出的关系: 1.当R端有效(0),S端无效时(1), ...

- FPGA模N计数器的实现

module ModuloN_Cntr(Clock, Clear, Q, QBAR); , UPTO = ;//计数器位数以及模数 input Clock, Clear; :]Q, QBAR; :]C ...

- 从CMOS到触发器(二)

PS:可以转载,转载请标明出处:http://www.cnblogs.com/IClearner/ 前面说了CMOS器件,现在就接着来聊聊锁存器跟触发器吧,下面是这次博文要介绍的主要内容: ·双稳态器 ...

- FPGA学习记录_设计一个计数器

此处设计一个数器,使 学习板上 的 LED 状态每 500ms翻转一次. 学习板上晶振为50MHz,也就是说时钟周期为 20ns , 这样可以计算得出 500ms = 500_000_000ns/20 ...

- 触发器(基本的SR触发器、同步触发器、D触发器)

一.能够存储1位二值信号的基本单元电路统称为触发器(Filp-Flop) 触发器是构成时序逻辑电路的基本逻辑部件.它有两个稳定状态:“0”和“1”.在不同的输入情况下,它可以被置0状态或1状态,当输入 ...

- Powmod快速幂取模

快速幂取模算法详解 1.大数模幂运算的缺陷: 快速幂取模算法的引入是从大数的小数取模的朴素算法的局限性所提出的,在朴素的方法中我们计算一个数比如5^1003%31是非常消耗我们的计算资源的,在整个计算 ...

- 【iCore1S 双核心板_FPGA】例程八:触发器实验——触发器的使用

实验现象: 在本实验中,将工程中的D触发器.JK触发器实例化,对应其真值表,用signal对其进行 检验,利用SignaTap II观察分析波形. 核心代码: module D( input CLK, ...

- 锁存器 Latch v.s. 触发器 Flip-Flop

转载 http://guqian110.github.io/pages/2014/09/23/latch_versus_flip_flop.html 根据 Wiki: Flip-flop (elec ...

随机推荐

- apk编辑器测评

hi你好,我今天要介绍的就是apk编辑器 这里我用的是apk编辑器专业版 APK编辑器 关于 APK 编辑器智友汉化组论坛:bbs.zhiyoo.com修改应用程序名称美化 UI: 更改背景图片删除广 ...

- [HNOI2016]最小公倍数 (可回退并查集,回滚莫队)

题面 题目链接 题目描述 给定一张 N N N 个顶点 M M M 条边的无向图(顶点编号为 1 , 2 , - , n 1,2,\ldots,n 1,2,-,n),每条边上带有权值.所有权值都可以分 ...

- metasploit进行局域网远控

用metasploit进行局域网远程控制 Metasploit是一款开源的安全漏洞检测工具,可以帮助安全和IT专业人士识别安全性问题,验证漏洞的缓解措施,并管理专家驱动的安全性进行评估,提供真正的安全 ...

- Linux虚拟机快捷键大全

转发请注明原作者! 图形化命令框快捷键 Ctrl-Shift-t 创建标签页 Ctrl-Shift-w 关闭标签页 Ctrl-Shift-n 创建新窗口 Ctrl-Shift-q 关闭新窗口 Ctrl ...

- [Python]-pdb模块-单步调试

使用pdb模块辅助python调试. import pdb 断点模式 在需要调试的语句前设置断点,加入这行代码: pdb.set_trace() 程序运行到这就会进入断点调试模式. 输入 作用 n 运 ...

- 我的Go并发之旅、01 并发哲学与并发原语

注:本文所有函数名为中文名,并不符合代码规范,仅供读者理解参考. 上下文 上下文(Context)代表了程序(也可以是进程,操作系统,机器)运行时的环境和状态,联系程序整个生命周期与资源调用,是程序可 ...

- go-fastdfs和配套使用的web页面

go-fastdfs go-fastdfs是一个基于http协议的分布式文件系统,它基于大道至简的设计理念,一切从简设计,使得它的运维及扩展变得更加简单,它具有高性能.高可靠.无中心.免维护等优点. ...

- nginx进程所属用户问题讨论

结论 1,在非root账户下启动时,nignx的master和worker进程的用户都将是这个账户, 2,在root账户下启动时 nignx的master进程是用户是root,worker的用户在co ...

- logstash中关于Jdbc输入配置选项详解

Setting Input type Required clean_run boolean No columns_charset hash No connection_retry_attempts n ...

- 通过堡垒机上传文件报错ssh:没有权限的问题

背景描述 一台有公网IP的主机安装的有jumpserver,假设为A主机,另外几台没有公网ip的主机,假设其中一个为B主机. 操作 1.通过主机A的公网IP和端口等登录到jumpserver的管理员用 ...