Verilog中的阻塞与非阻塞

按说阻塞与非阻塞是Verilog中最基本的东西,也是老生常谈。但是最近看到很多程序里用到阻塞语句竟然不是很明白,说到底是从来没有自己仔细分析过。当然一般情况程序中也是推荐用非阻塞的。

一般来说大家都会用以下几个例子来说明阻塞与非阻塞:

大家可以参考http://www.cnblogs.com/crazybingo/archive/2012/03/20/2408980.html

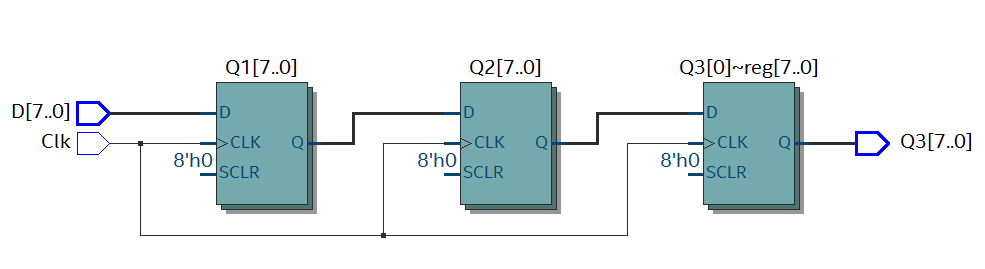

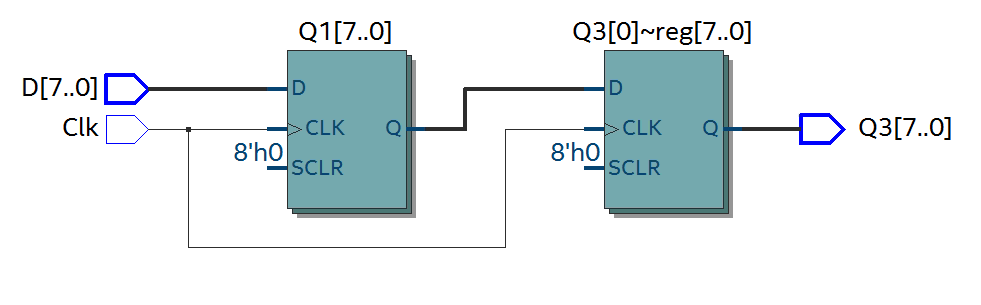

| HDL源代码 | 对应的RTL电路 |

module Shifter1( |

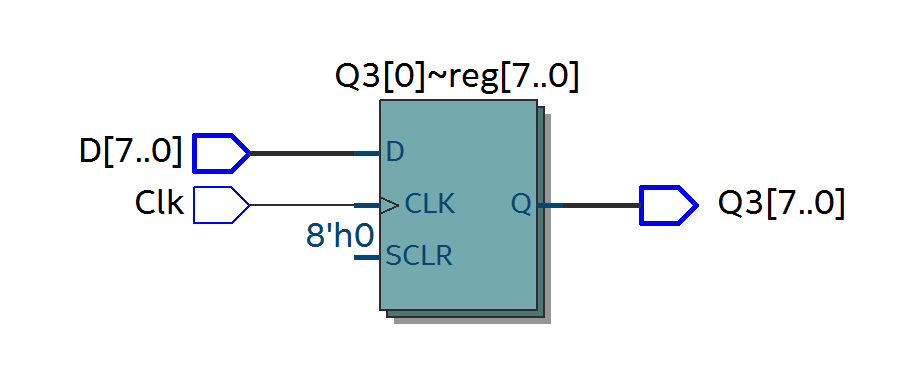

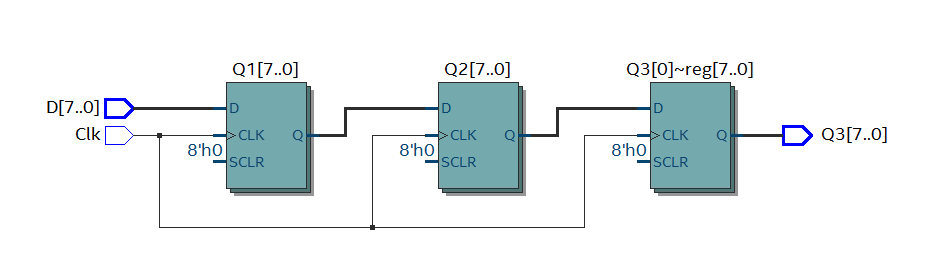

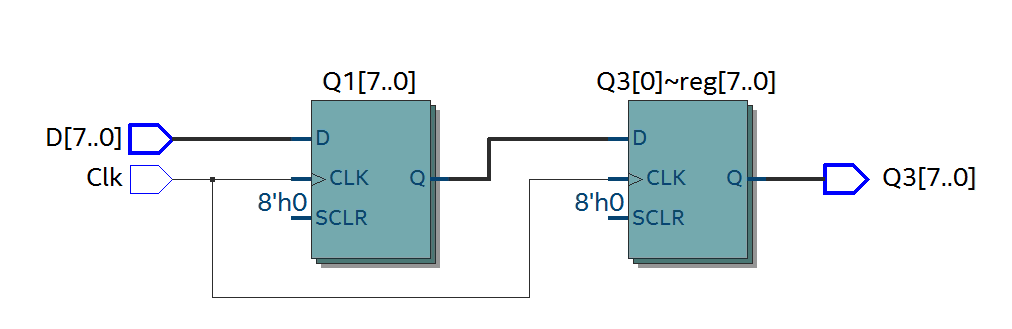

▲ 大家可以看到Q1、Q2被优化掉了 |

module Shifter2( |

|

module Shifter3( |

|

module Shifter4( |

|

module Shifter5( |

|

module Shifter6( |

|

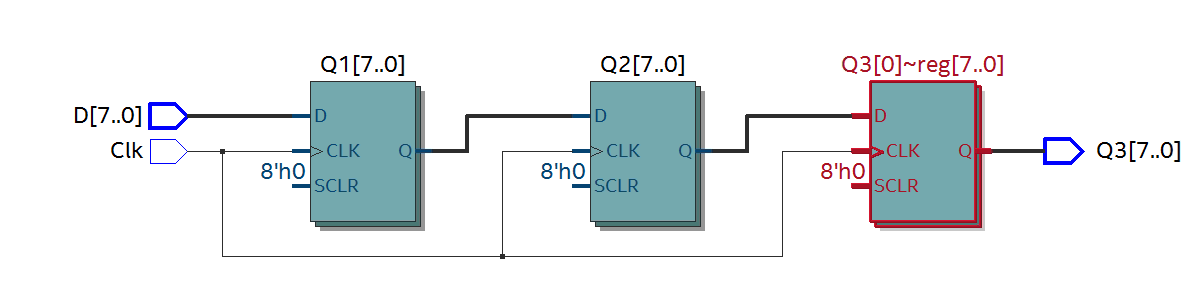

从上面的例子可以看出:

(1)阻塞语句定义的寄存器是可能被优化掉的

(2)阻塞语句定义的寄存器是否被优化是与语句顺序有关系的

参考文档中提到非阻塞语句执行的过程中先把每条语句当作一个事件放入事件队列中来执行的。它能很方便帮助理解非阻塞过程。

所谓非阻塞赋值,顾名思义,就是指当前语句的执行不会阻塞下一语句的执行。

always @(posedge Clk)

begin

Q1 <= D;

Q2 <= Q1;

Q3 <= Q2;

end

首先执行Q1 <= D,产生一个更新事件,将D的当前值赋给Q1,但是这个赋值过程并没有立刻执行,而是在事件队列中处于等待状态。

然后执行Q2 <= Q1,同样产生一个更新事件,将Q1的当前值(注意上一语句中将D值赋给Q1的过程并没有完成,Q1还是旧值)赋给Q2,这个赋值事件也将在事件队列中处于等待状态。

再执行Q3 <= Q2,产生一个更新事件,将Q2的当前值赋给Q3,这个赋值事件也将在事件队列中等待执行。

这时always语句块执行完成,开始对下一个Clk上升沿敏感。

那么什么时候才执行那3个在事件队列中等待的事件呢?只有当当前仿真时间内的所有活跃事件和非活跃事件都执行完成后,才开始执行这些非阻塞赋值的更新事件。这样就相当于将D、Q1和Q2的值同时赋给了Q1、Q2和Q3。

下面是参考中的例子及阻塞实现过程:

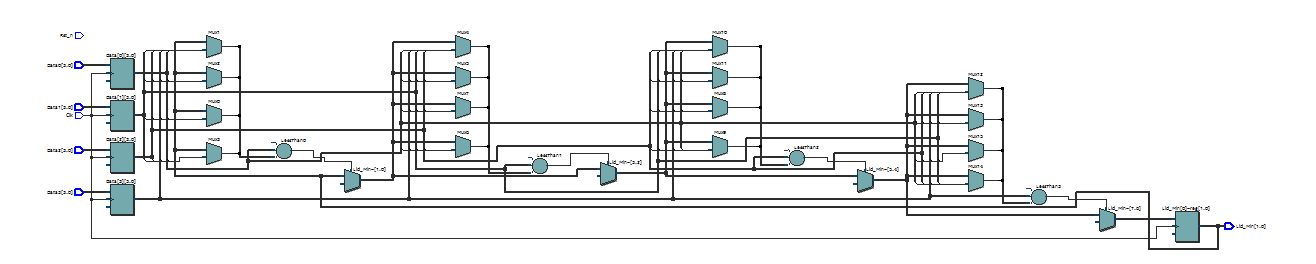

这里有一个数组:Data[0]、Data[1]、Data[2]和Data[3],它们都是4比特的数据。我们需要在它们当中找到一个最小的数据,同时将该数据的索引输出到LidMin中,这个算法有点类似于“冒泡排序”的过程,而且需要在一个时钟周期内完成。例如,如果这4个数据中 Data[2]最小,那么LidMin的值则为2。

module Bubble_Up(

Rst_n,

Clk,

Data0,

Data1,

Data2,

Data3,

Lid_Min

);

input Rst_n;

input Clk; input [:] Data0;

input [:] Data1;

input [:] Data2;

input [:] Data3;

reg [:] Data [:];

output [:] Lid_Min;

reg [:] Lid_Min; always @( posedge Clk )

begin

Data[] <= Data0;

Data[] <= Data1;

Data[] <= Data2;

Data[] <= Data3;

end

always @(posedge Clk )

begin if (Data[] <= Data[Lid_Min]) //"<="表示小于等于

begin

Lid_Min = 'd0; //"<="表示非阻塞赋值

end if (Data[] <= Data[Lid_Min])

begin

Lid_Min = 'd1;

end if (Data[] <= Data[Lid_Min])

begin

Lid_Min = 'd2;

end if (Data[] <= Data[Lid_Min])

begin

Lid_Min = 'd3;

end

end

endmodule

从实现的RTL视图上,我突然觉得阻塞一步到位的完成了很多组合逻辑。接下来我再说一些在程序上经常会遇到的例子。

reg current_state;

reg next_state;

reg inc_loops;

reg clr_loops;

reg set_valid;

reg [-:] loops;

reg [:] threshold;

reg [-:] dim_cnt_thresh_r;

reg [-:] cnt_thresh; always @ (posedge clk )

begin

current_state <= next_state;

end always @ (*)

begin

next_state = current_state;

clr_loops = 'b0;

inc_loops = 'b0;

set_valid = 'b0; case (current_state)

: begin

clr_loops = 'b1;

if (measure_valid) begin

next_state = 'b1;

end

end : begin

inc_loops = 'b1;

if (match | loops_max) begin

set_valid = 'b1;

clr_loops = 'b1;

next_state = 'b0;

end

end

endcase

end

上面一段程序,从RTL视图可以看到,除current_state为寄存器之外,其余全部综合为了组合逻辑,所以说,reg定义的数据也不全会综合成寄存器。但是贴出程序还是为了要体会阻塞的用法。

好像记得有这样的说法:在组合逻辑中用阻塞,在时序逻辑中用非阻塞。

如果把上面的程序修改成非阻塞赋值,如下,这样会不会存在问题呢?我个人认为有可能,可能要看综合器本身,如果case语句外的next_state <= current_state与case内的next_state <= 1'b0(或者1‘b1)是随机的,那状态可能会出错。不会一般都不会(因为我以前就有这样做过,没问题(>'~'<))

reg current_state;

reg next_state;

reg inc_loops;

reg clr_loops;

reg set_valid;

reg [-:] loops;

reg [:] threshold;

reg [-:] dim_cnt_thresh_r;

reg [-:] cnt_thresh; always @ (posedge clk )

begin

current_state <= next_state;

end always @ (*)

begin

next_state <= current_state;

clr_loops <= 'b0;

inc_loops <= 'b0;

set_valid <= 'b0; case (current_state)

: begin

clr_loops <= 'b1;

if (measure_valid) begin

next_state <= 'b1;

end

end : begin

inc_loops <= 'b1;

if (match | loops_max) begin

set_valid <= 'b1;

clr_loops <= 'b1;

next_state <= 'b0;

end

end

endcase

end

不过在这篇博客中,也给出了一种表达

|

|

module and_nonblocking

(

input a,

input b,

input c,

output reg y

); always@*

begin // y_entry = y

y <= a; // y_exit = a

y <= y & b; // y_exit = y_entry & b

y <= y & c; // y_exit = y_entry & c

end // y = y_exit endmodule

注意always块内的前2条语句将不会产生任何效果。上述always块等价与:

always@*

y <= y & c;

FPGA Verilog语言中阻塞赋值与非阻塞赋值个人看法

Verilog中的阻塞与非阻塞的更多相关文章

- Verilog之阻塞赋值非阻塞赋值

verilog设计进阶 时间:2014年5月6日星期二 主要收获: 1. 阻塞赋值与非阻塞赋值: 2. 代码测试: 3. 组合逻辑电路和时序逻辑电路. 阻塞赋值与非阻塞赋值: 1. 阻塞赋值" ...

- IO中同步、异步与阻塞、非阻塞的区别

一.同步与异步同步/异步, 它们是消息的通知机制 1. 概念解释A. 同步所谓同步,就是在发出一个功能调用时,在没有得到结果之前,该调用就不返回. 按照这个定义,其实绝大多数函数都是同步调用(例如si ...

- IO中同步、异步与阻塞、非阻塞的区别(转)

转自:http://blog.chinaunix.net/uid-26000296-id-3754118.html 一.同步与异步同步/异步, 它们是消息的通知机制 1. 概念解释A. 同步所谓同步, ...

- Linux设备驱动中的阻塞和非阻塞I/O

[基本概念] 1.阻塞 阻塞操作是指在执行设备操作时,托不能获得资源,则挂起进程直到满足操作所需的条件后再进行操作.被挂起的进程进入休眠状态(不占用cpu资源),从调度器的运行队列转移到等待队列,直到 ...

- socket网络编程中的同步,异步,阻塞式,非阻塞式,有何联系与区别?

一.举个打电话的例子: 阻塞 block 是指,你拨通某人的电话,但是此人不在,于是你拿着电话等他回来,其间不能再用电话.同步大概和阻塞差不多. 非阻塞 nonblock 是指,你拨通 ...

- 蜕变成蝶~Linux设备驱动中的阻塞和非阻塞I/O

今天意外收到一个消息,真是惊呆我了,博客轩给我发了信息,说是俺的博客文章有特色可以出本书,,这简直让我受宠若惊,俺只是个大三的技术宅,写的博客也是自己所学的一些见解和在网上看到我一些博文以及帖子里综合 ...

- node.js中对同步,异步,阻塞与非阻塞的理解

我们都知道javascript是单线程的,node.js是一个基于Chrome V8 引擎的 javascript 运行时环境,注意 node.js 不是一门语言,别搞错了. javascript为什 ...

- Linux设备驱动中的IO模型---阻塞和非阻塞IO【转】

在前面学习网络编程时,曾经学过I/O模型 Linux 系统应用编程——网络编程(I/O模型),下面学习一下I/O模型在设备驱动中的应用. 回顾一下在Unix/Linux下共有五种I/O模型,分别是: ...

- [转]Socket编程中,阻塞与非阻塞的区别

阻塞:一般的I/O操作可以在新建的流中运用.在服务器回应前它等待客户端发送一个空白的行.当会话结束时,服务器关闭流和客户端socket.如果在队列中没有请示将会出现什么情况呢?那个方法将会等待一个的到 ...

随机推荐

- c++ 中map 的find 函数用法

Map中,find函数用来定位数据出现位置,当含有该数据,即查找成功时,返回数据所在未知的迭代器, 如果查找失败,则返回end()函数所在的迭代器,因此用是否等于end来判断是否查找成功. 程序示例: ...

- python+selenium环境安装

目前 selenium 版本已经升级到 3.7了,网上的大部分教程是基于 2.x写的,所 以在学习前先要弄清楚版本号,这点非常重要.本系列依然以 selenium2 为基础, 目前 selenium3 ...

- 有关Oracle统计信息的知识点[z]

https://www.cnblogs.com/sunmengbbm/p/5775211.html 一.什么是统计信息 统计信息主要是描述数据库中表,索引的大小,规模,数据分布状况等的一类信息.例如, ...

- IDEA安装小配置

1. view-->toolbar+toolbuttons 2. 根据大小写IDEA能准确提示 配置自动导入包 定义代码模板 提示忽略大小写 配置虚拟机内存,修改idea64.exe.vmopt ...

- 基础数据类型补充,及capy daty7

1,基础数据类型,总结补充. int:bit_lenth() str: captilze() 首字母大写,其余小写. upper() 全大写. lower() 全小写. find() 通过元素找索引, ...

- js generator

generator(生成器)是ES6标准引入的新的数据类型.一个generator看上去像一个函数,但可以返回多次. generator跟函数很像,定义如下: function* foo(x) { y ...

- 1N - 计算球体积

根据输入的半径值,计算球的体积. Input 输入数据有多组,每组占一行,每行包括一个实数,表示球的半径. Output 输出对应的球的体积,对于每组输入数据,输出一行,计算结果保留三位小数. Sam ...

- 探索未知种族之osg类生物---器官初始化四

上一节我们对完成了对osg生物内部非常重要器官graphicsContext的初始化工作.这样就可保证我们场景中至少有一个graphicContext存在,不至于刚出生就面临夭折.我们根据上一节中os ...

- [Robot Framework] 通过RemoteWhiteLibrary启动程序并登录初尝试

启动remote whitelibrary之后,在robot framework中配置好library,就可以调用whitelibrary的关键字了 启动APP White.LAUNCHAPP ...

- 企业官网原型制作分享-Starbucks

星巴克是全球著名的咖啡连锁店,星巴克的产品不单是咖啡,咖啡只是一种载体.而正是通过咖啡这种载体,星巴克把一种独特的格调传送给顾客.咖啡的消费很大程度上是一种感性的文化层次上的消费,文化的沟通需要的就是 ...