FPGA低级建模---按键去抖动

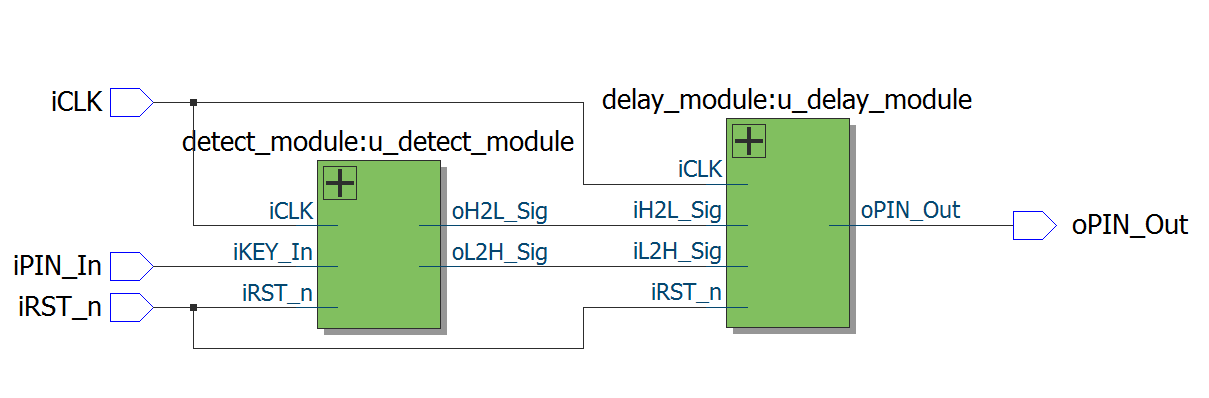

FPGA低级建模,原则上一个模块一个功能,如按键去抖动建模中,有两个模块。

1、detect_module 这个是按键检测模块,主要检测按键的高低电平变化,现在按键是按下还是释放。

2、delay_module 这个是滤波去抖模块,主要是防止按键或外界的抖动干扰。

综合后如下RTL图:

3、以下是建模的Verilog代码:

顶层模块:debounce_module

module debounce_module(

input iCLK,

input iRST_n,

input iPIN_In,

output oPIN_Out

);

wire H2L_Sig_W;

wire L2H_Sig_W;

delay_module u_delay_module(

.iCLK( iCLK ),

.iRST_n( iRST_n ),

.iH2L_Sig( H2L_Sig_W ),

.iL2H_Sig( L2H_Sig_W ),

.oPIN_Out( oPIN_Out )

);

detect_module u_detect_module(

.iCLK( iCLK ),

.iRST_n( iRST_n ),

.iKEY_In( iPIN_In ),

.oH2L_Sig( H2L_Sig_W ),

.oL2H_Sig( L2H_Sig_W )

);

endmodule

延时模块:delay_module

module delay_module(

input iCLK,

input iRST_n,

input iH2L_Sig,

input iL2H_Sig,

output oPIN_Out

);

/************************************************************************/

//50M系统晶振 50M*0.001 -1 = 49_999

parameter T1MS = 16'd49999;

/************************************************************************/

reg [15:0] Count1;

reg isEn;

reg isCount; //是否计数

reg [3:0] Count_MS;

reg rPin_Out;

reg [1:0] i;

//1ms 计数

always @(posedge iCLK or negedge iRST_n)

begin

if( !iRST_n )

Count1 <= 16'd0;

else if( isCount && (Count1 == T1MS ))

Count1 <= 16'd0;

else if( isCount )

Count1 <= Count1 + 1'b1;

else if( !isCount )

Count1 <= 16'd0;

end

//16ms 计数

always @( posedge iCLK or negedge iRST_n)

begin

if( !iRST_n )

Count_MS <= 4'd0;

else if( isCount && ( Count1 == T1MS ))

Count_MS <= Count_MS + 1'b1;

else if( !isCount )

Count_MS <= 4'd0;

end

//

always @( posedge iCLK or negedge iRST_n)

begin

if( !iRST_n ) begin

isCount <= 1'b0;

rPin_Out <= 1'b0;

i <= 2'd0;

end

else

case( i )

2'd0:

begin

if( iH2L_Sig ) i <= 2'd1;

else if( iL2H_Sig ) i <= 2'd2;

end

2'd1:

begin

if( Count1 == T1MS ) begin

isCount <=1'b0;

rPin_Out <= 1'b1;

i <= 2'd0;

end

else

isCount <= 1'b1;

end

2'd2:

begin

if( Count1 == T1MS ) begin

isCount <= 1'b0;

rPin_Out <= 1'b0;

i <= 2'd0;

end

else

isCount <= 1'b1;

end

endcase

end

assign oPIN_Out = rPin_Out;

endmodule

按键检测模块: detect_module

module detect_module(

input iCLK,

input iRST_n,

input iKEY_In,

output oH2L_Sig,

output oL2H_Sig

);

/************************************************************************/

//50M系统晶振 50M*0.0001 -1 = 4_999

parameter T100US = 11'd4999;

/************************************************************************/

reg [10:0] Count1;

reg iSEn;

//100us 计数

always @(posedge iCLK or negedge iRST_n)

begin

if( !iRST_n ) begin

Count1 <= 11'h0;

iSEn <= 1'b0;

end

else begin

if( Count1 == T100US )

iSEn <= 1'b1;

else

Count1 <= Count1 + 1'b1;

end

end

reg H2L_F1;

reg H2L_F2;

reg L2H_F1;

reg L2H_F2;

//判断是否有按键按下或释放

always @( posedge iCLK or negedge iRST_n)

begin

if( !iRST_n ) begin

H2L_F1 <= 1'b1;

H2L_F2 <= 1'b1;

L2H_F1 <= 1'b0;

L2H_F2 <= 1'b0;

end

else begin

H2L_F1 <= iKEY_In;

H2L_F2 <= H2L_F1;

L2H_F1 <= iKEY_In;

L2H_F2 <= L2H_F1;

end

end

assign oH2L_Sig = iSEn? ( H2L_F2 & !H2L_F1 ):1'b0;

assign oL2H_Sig = iSEn? ( !L2H_F2 & L2H_F1 ):1'b0;

endmodule

FPGA低级建模---按键去抖动的更多相关文章

- FPGA按键去抖verilog代码

按键去抖的原因及其分类就不罗嗦了. 在这里解释一段代码,代码是网上找的,看了半天没懂,无奈查了半天想了半天,终于明白了... module sw_debounce(clk,rst_n,sw1,sw2, ...

- 【第一季】CH08_FPGA_Button 按钮去抖动实验

[第一季]CH08_FPGA_Button 按钮去抖动实验 按键的消抖,是指按键在闭合或松开的瞬间伴随着一连串的抖动,这样的抖动将直接影响设计系统的稳定性,降低响应灵敏度.因此,必须对抖动进行处理,即 ...

- verilog 建模笔记--低级建模

来源 <verilog HDL那些事--建模篇> 1.并行建模的思想. 2.每个模块最好只有一个功能.(便于修改和扩展,特别在大的项目中) 典型的 HDL 教科书中,才不会要读者了解“模 ...

- week05 06绑定滚动条 去抖动

像这种小代码 为了满足某种需求 可以直接上网搜 这些都是JS代码和react无关 我们下拉 就会触发事件从而调用loading more news 那个函数 react要求我们加个key key就是唯 ...

- Linux驱动之定时器在按键去抖中的应用

机械按键在按下的过程中会出现抖动的情况,如下图,这样就会导致本来按下一次按键的过程会出现多次中断,导致判断出错.在按键驱动程序中我们可以这么做: 在按键驱动程序中我们可以这么做来取消按键抖动的影响:当 ...

- FPGA按一下按键,对应端口输出单个脉冲

对于FPGA的verilog语言,,,规定一个变量不能在多个always中被赋值.但是可以在多个alway块中做判断--结合状态机思想 module state(key,led,clk); input ...

- 深入理解JS函数节流和去抖动

一.什么是节流和去抖? 1.节流 节流就是拧紧水龙头让水少流一点,但是不是不让水流了.想象一下在现实生活中有时候我们需要接一桶水,接水的同时不想一直站在那等着,可能要离开一会去干一点别的事请,让水差不 ...

- fpga Verilog hdl 按键消抖 部分程序讲解

module debounce(clk_in,rst_in,key_in,key_pulse,key_state); input clk_in;//system clock input rst_in; ...

- 【黑金ZYNQ7000系列原创视频教程】06.ZYNQ来自FPGA的中断——按键中断实验

黑金论坛地址: http://www.heijin.org/forum.php?mod=viewthread&tid=36640&extra=page%3D1 爱奇艺地址: http: ...

随机推荐

- setInterval和clearInterval

<!DOCTYPE html> <html> <head lang="en"> <meta charset="UTF-8&quo ...

- 用JavaScript输出表格

<!DOCTYPE HTML PUBLIC "-//W3C//DTD HTML 4.01 Transitional//EN" "http://www.w3.org/ ...

- Eclipse/IDEA使用小技巧

使用IDEA,先将keymap改为eclipse形式 1.搜索技巧: f4:列举所有类树状结构 Ctrl+F:搜索特定词 Ctrl+T:列举所有子类 Ctrl+O:快速检索想要的方法 Ctrl+Shi ...

- Swing图形用户界面

package test; import java.awt.event.ActionEvent;import java.awt.event.ActionListener; import javax.s ...

- JUnit报错需导入两个jar包

<dependency> <groupId>org.hamcrest</groupId> <artifactId>hamcrest-core</a ...

- Java学习

第一个java程序: 用记事本创建一个文件名为HelloWorld.java文件,我的目录为D:\My Documents\Java-workspace\Test\HelloWorld.java. 打 ...

- @SuppressWarnings("deprecation")

在Java编译过程中会出现很多警告,有很多是安全的,但是每次编译有很多警告影响我们对error的过滤和修改,我们可以在代码中加上 @SuppressWarnings("XXXX") ...

- imooc-java-作业练习-20150918

小伙伴们,请根据所学知识,编写一个 JAVA 程序,实现输出考试成绩的前三名 要求: 1. 考试成绩已保存在数组 scores 中,数组元素依次为 89 , -23 , 64 , 91 , 119 , ...

- GROUP与HAVING的使用

SELECT pub_name, state,SUM(state) AS 总数 FROM publishers GROUP BY pub_name, state HAVING SUM(state)&g ...

- 简述jsp之EL表达式和jstl及其使用

Jsp的指令之include指令include指令:代表的是页面的包含. 作用:可以把一些jsp的页面包含在一起,对外展示. 页面的布局,现在已经不用了,现在都用css+div进行布局.include ...