基于FPGA的DDS设计(二)

在DDS设计中,如果相位累加器每个时钟周期累加1,就会输出频率为195.313KHz的波形。如果每个时钟周期累加2,就会输出频率为2*195.313KHz的波形·······,如果每两个时钟周期累加1,就会输出195.313/2KHz的波形······,如果按照这样来设计话,不太方便并且输出波形的频率是不连续的,只能输出一些特殊的频率。

首先我们可以一起考虑一个问题,如果我们想要得到一个累加数字0~9,但是想要每次累加的数字有可能是整数也有可能是小数,那么此时整个计算又不让出现小数,应该怎么做呢?我们可以做一个三位数,然后把百位当作我们的输出,然后每次累加的数字自己可以随意调整,也就是相当于之前可以累加小数,小数最小精度为两位小数。000+011=011,123+001=124。如果按照此中方式,让数字一直不断的累加,数字会从最小到最大,不断循环。但是最高位依然是0~9的变化,只不过0~9变化的周期是受到每次累加的值的影响。如果每次累加001,那么百位0~9的循环就需要1000个累加(不要仅仅想0~900,要不断循环),如果每次累加010,那么百位0~9的循环就需要100个累加。

如果考虑明白上述的问题,那么在DDS中,我们做了一个相位累加器,但是累加器只是负责ROM地址的输出也就是8位的。如果按照上述思想我们可以设计一个位宽为32位的计数器,把计数器的高八位当作ROM的地址。让计数器每个时钟周期累加1,地址从0增长到255,也就是8‘b00000000~8’b11111111,需要整个32位从全0到全1,一共需要2的32次幂个时钟周期,而这个也就是输出整个波形用的时间----波形周期。我们可以算出周期:2的32次幂*20ns,频率为0.01164153218Hz(这个数字太长了,用f0代替)。每次加1,频率为f0,如果每次加2,频率为2倍的f0。那么我们可以任意整数倍的f0,如果f0足够小(此时f0已经足够小),我们认为可以得到任意频率。如果f0的频率不够小,可以通过增加计数器的位宽来实现。

建议读者不要每次加1去仿真,仿真时间太长,并且有可能导致整个仿真器卡主。笔者在此仿真每次累加100K。

module addr_ctrl (

input wire clk_50m,

input wire rst_n,

output wire [:] addr

);

reg [:] cnt;

assign addr = cnt[:];

always @ (posedge clk_50m, negedge rst_n) begin

if (rst_n == )

cnt <= ;

else

cnt <= cnt + 100_000;

end

endmodule

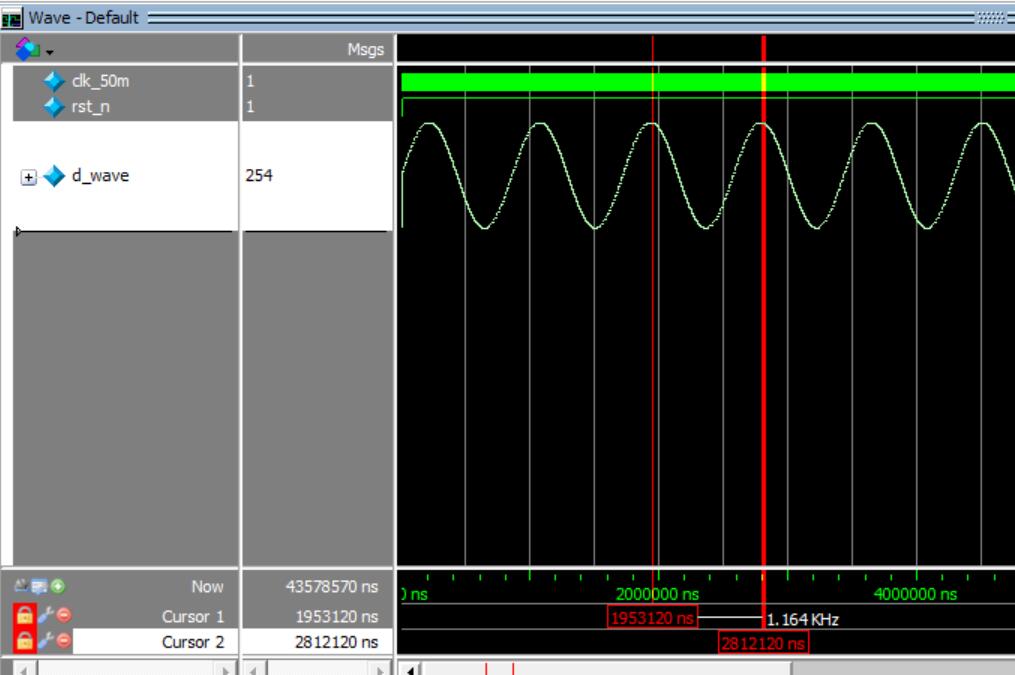

仿真结果如图8。

图8

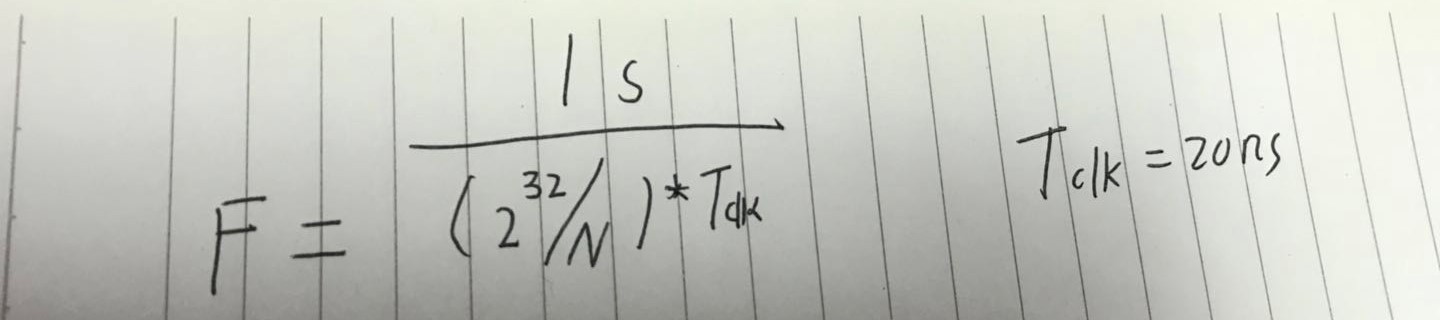

每次累加100K,仿真测试频率为1.164KHz。每次累加1,得出的频率为0.01164153218Hz。正好扩大了100K倍。现在我们只要知道做每次累加多少,就能够通过算基础这个频率的多少倍就能算出来频率,但是这么算是会有误差,因为上述得到的频率就是一个近似值。我们可以按照公式去计算频率,假如每次增加N,那么输出波形的周期应该是2的32次幂除以N乘以时钟周期(20ns),用1s除以周期就可以得到频率(如图9)。

图9

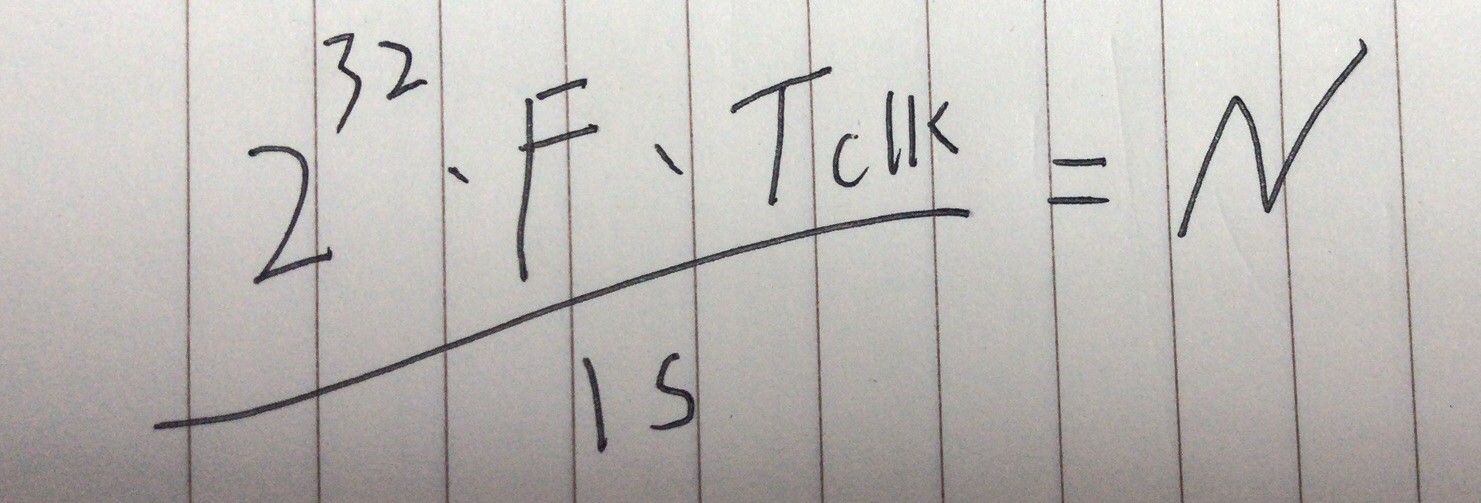

通过上面的方法,我们可以轻易知道,累加N所对应的频率。但是在实际应用中,往往是想要某一个频率的波形,而不是有了波形算波形的频率是多少。根据外部要求频率,算出来每次累加N的具体数值,这就是频率控制器。其实也是比较简单的,我们把上述公式转换以下就可以了(如图10)。

图10

把图10当中的公式在FPGA实现,输入F得到N就是频率控制器。在计算中会有可能存在一些误差,因为有可能计算的数值为12345.24,但是在累加时,会按照12345来进行累加,.24会被忽略,往往会带来一个误差,但是此误差一般都是可以接受的。

好了DDS的设计到此结束了,但是如果想要真正输出一个模拟的波形还要驱动一个DAC器件,来达到真正的模拟波形的输出。

笔者水平有限,如果设计中,有什么不妥的地方,恳请大佬们指出来。

欢迎加好友探讨QQ:746833924,QQ群:173560979。

基于FPGA的DDS设计(二)的更多相关文章

- 基于FPGA的DDS设计(一)

最近在学习基于FPGA的DDS设计,借此机会把学习过程记录下来,当作自己的学习笔记也希望能够帮助到学习DDS的小伙伴. DDS(Direct Digital Synthesizer)直接数字合成器,这 ...

- 38.基于FPGA的FIR设计二

利用fdatool工具生成的滤波器系数与用代码生成的系数不一致,在网上查询得知,fdatool生成的滤波器系数是有符号小数,而且是浮点型,而代码生成的滤波器系数是定点型有符号数,故不一样. 浮点型数据 ...

- 基于FPGA的DDS任意波形发生器设计

一.简介 DDS技术最初是作为频率合成技术提出的,由于其易于控制,相位连续,输出频率稳定度高,分辨率高, 频率转换速度快等优点,现在被广泛应用于任意波形发生器(AWG).基于DDS技术的任 ...

- 基于FPGA(DDS)的正弦波发生器

记录背景:昨晚快下班时,与同事rk聊起怎么用FPGA实现正弦波的输出.我第一反应是利用高频的PWM波去滤波,但感觉这样的波形精度肯定很差:后来想起之前由看过怎么用FPGA产生正弦波的技术,但怎么都想不 ...

- [原创]FPGA JTAG工具设计(二)

经过前期打样 基于FT2232H的JTAG &UART板级已经初步形成 在Viado环境和ISE(13.2+)环境可以使用 速度支持10MHz/15MHz/30MHz 在ISE iMpact下 ...

- 优化基于FPGA的深度卷积神经网络的加速器设计

英文论文链接:http://cadlab.cs.ucla.edu/~cong/slides/fpga2015_chen.pdf 翻译:卜居 转载请注明出处:http://blog.csdn.net/k ...

- 自己动手写CPU(基于FPGA与Verilog)

大三上学期开展了数字系统设计的课程,下学期便要求自己写一个单周期CPU和一个多周期CPU,既然要学,就记录一下学习的过程. CPU--中央处理器,顾名思义,是计算机中最重要的一部分,功能就是周而复始地 ...

- 基于ZedBoard的Webcam设计(一):USB摄像头(V4L2接口)的图片采集【转】

转自:http://www.cnblogs.com/surpassal/archive/2012/12/19/zed_webcam_lab1.html 一直想把USB摄像头接到Zedboard上,搭建 ...

- 基于FPGA的VGA显示设计(二)

上一篇:基于FPGA的VGA显示设计(一) 参照 CrazyBingo 的 基于FPGA的VGA可移植模块终极设计代码 的工程代码风格,模块化处理了上一篇的代码,并增加了一点其它图形. 顶层 ...

随机推荐

- gitlab自动备份恢复与卸载

一.gitlab数据备份gitlab-rake gitlab:backup:create命令会在/var/opt/gitlab/backups目录下创建一个名称类似为1393513186_gitlab ...

- 骑士周游问题跳马问题C#实现(附带WPF工程代码)

骑士周游问题,也叫跳马问题. 问题描述: 将马随机放在国际象棋的8×8棋盘的某个方格中,马按走棋规则进行移动.要求每个方格只进入一次,走遍棋盘上全部64个方格. 代码要求: 1,可以任意选定马在棋盘上 ...

- nlog 2.0 强制转换使用 4.0 版本

今天下午研发代码,发现调用其他小组研发的代码,发现其中有使用nlog功能,但nlog版本是2.0 ,而我的项目使用4.0 版本 导致部分功能不能使用,故在web配置文件中加入以下代码即可 <de ...

- MySQL 触发器-更新字段时,status列会加一

需求:当更新列中的字段时,列中的status字段,就会+1 表结构 CREATE TABLE `test_1` ( `id` int(11) DEFAULT NULL, `name` varchar( ...

- 对json的理解?

回答一: a.JSON对象:以 ”{“ 开始,以 ”}” 结束,里面则是一系列的键(key)值(value)对,键和值用 ”:” 分开,每对键值对之间用 ”,” 分开.参考以下语法: {key1:va ...

- POJ 3261 Milk Patterns 【后缀数组 最长可重叠子串】

题目题目:http://poj.org/problem?id=3261 Milk Patterns Time Limit: 5000MS Memory Limit: 65536K Total Subm ...

- MyBatis(1)-简单入门

简介 什么是 MyBatis ? MyBatis 是一款优秀的持久层框架,它支持定制化 SQL.存储过程以及高级映射.MyBatis 避免了几乎所有的 JDBC 代码和手动设置参数以及获取结果集.My ...

- SpringBoot实战(十三)之缓存

什么是缓存? 引用下百度百科的解释: 缓存就是数据交换的缓冲区(又称作Cache),当某一硬件要读取数据时,会首先从缓存中查找需要的数据,找到了则直接执行,找不到的话则从内存中查找.由于缓存的运行速度 ...

- 【SP2713 GSS4 - Can you answer these queries IV】 题解

题目链接:https://www.luogu.org/problemnew/show/SP2713 真暴力啊. 开方你开就是了,开上6次就都没了. #include <cmath> #in ...

- nRF5 SDK for Mesh(三) Installing the mesh toolchain 安装编译工具链

Installing the mesh toolchain To build the example applications, a toolchain based on either CMake o ...