使用logisim搭建单周期CPU与添加指令

使用logisim搭建单周期CPU与添加指令

搭建

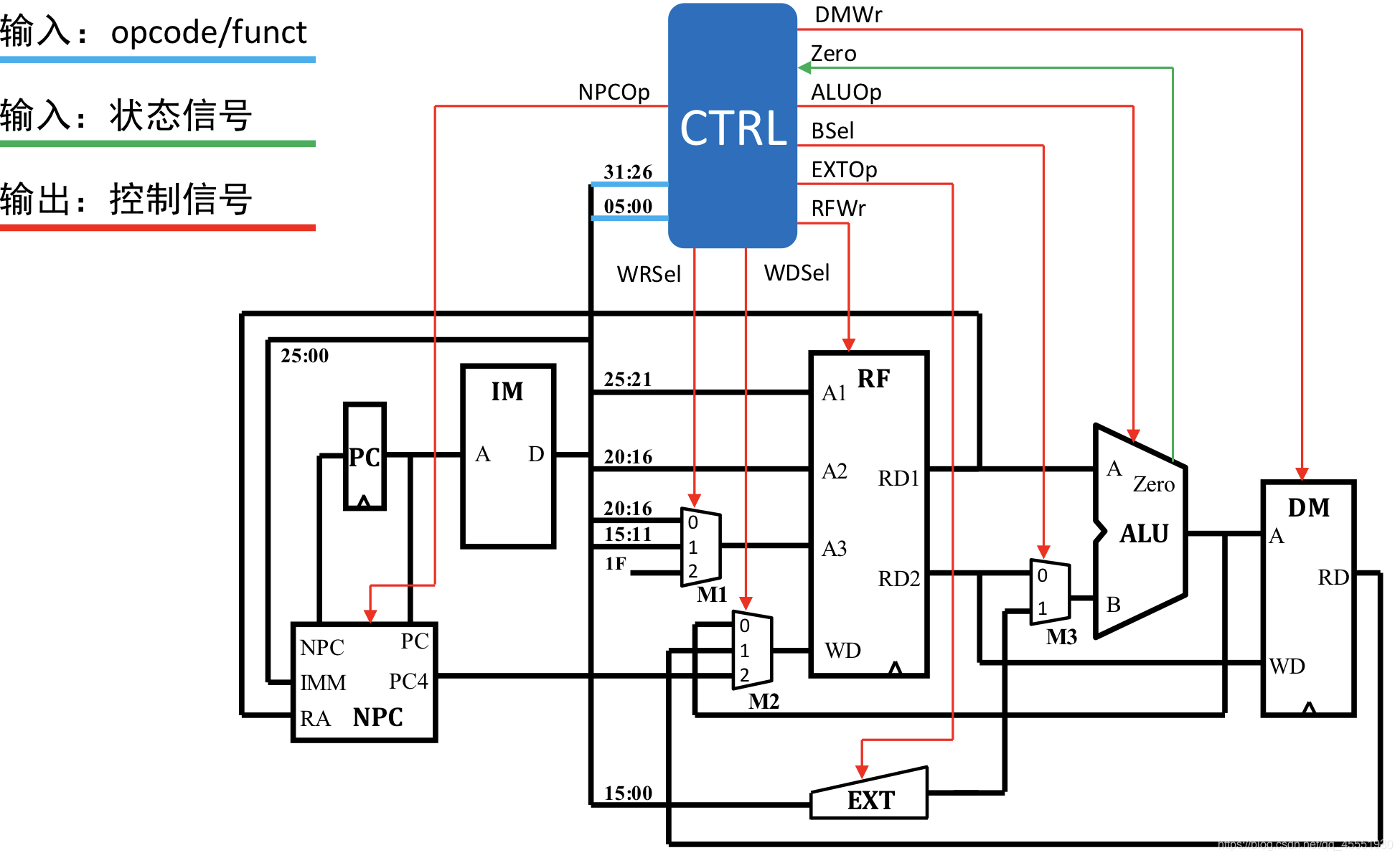

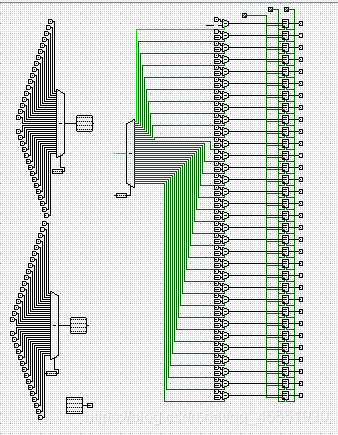

总设计

借用高老板的图,我们只需要分别做出PC、NPC、IM、RF、EXT、ALU、DM、Controller模块即可,再按图连线,最后进行控制信号的处理,一个CPU就差不多搭完了。目前支持的指令集为{addu、subu、ori、lw、sw、beq、jal、jr、nop、lui、sb、lb、sh、lh}

下面分模块逐个分析

PC

本质上就是一个32位的寄存器,这里采用的是异步复位,所以直接把reset信号连在clear口。

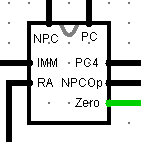

NPC

由于我的CPU支持beq、jal、jr,所以NPCOp有2位,如下表所示

| NPCOp | 功能 |

|---|---|

| 00 | 计算顺序地址(PC+4) |

| 01 | 计算beq地址 |

| 10 | 计算jal地址 |

| 11 | 计算jr地址 |

其中PC4是用来把PC+4输出至RF以完成jal指令

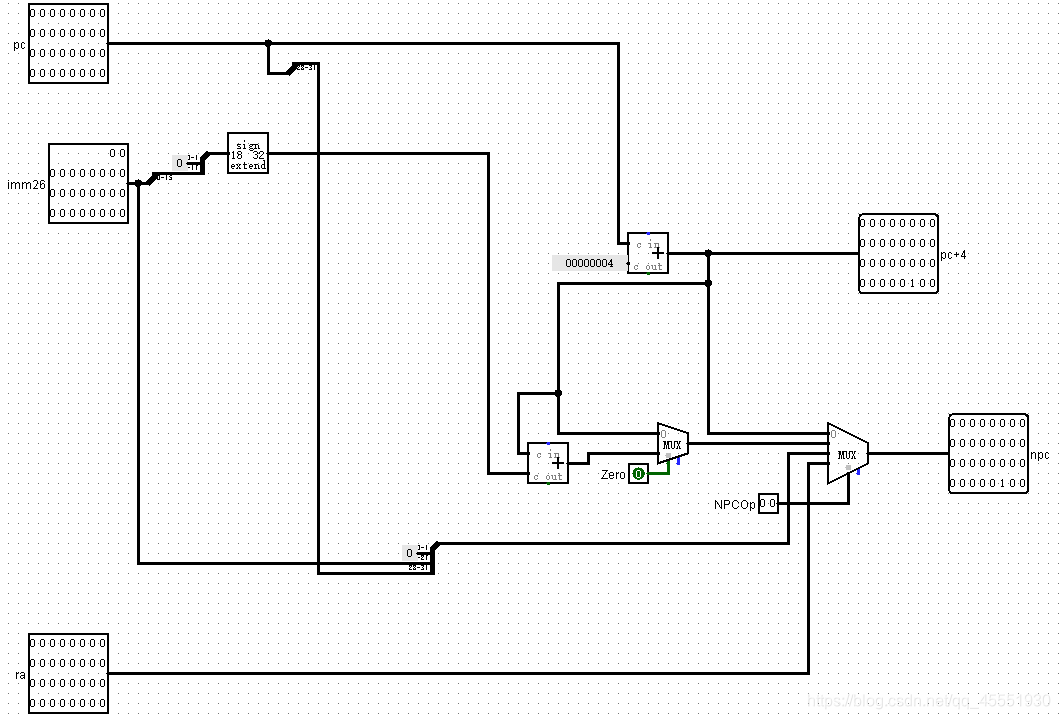

IM

这个就更简单了,直接一个ROM搞定,注意把PC的2~6位引出作为IM的地址。

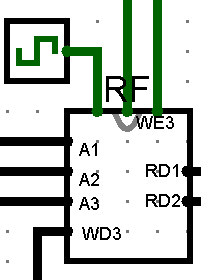

RF

这个比较耗时间,听说用vscode打开.circ文件就可以写代码去搭建这玩意,打开后发现3k行代码,直接反手关掉vscode继续手动连线。连完应该差不多这个样子。

外部看起来是这样子的,RD1输出A1对应寄存器的值,RD2输出A2对应寄存器的值,当写使能信号WE3有效时,将在时钟上升沿把WD3写入A3对应的寄存器。

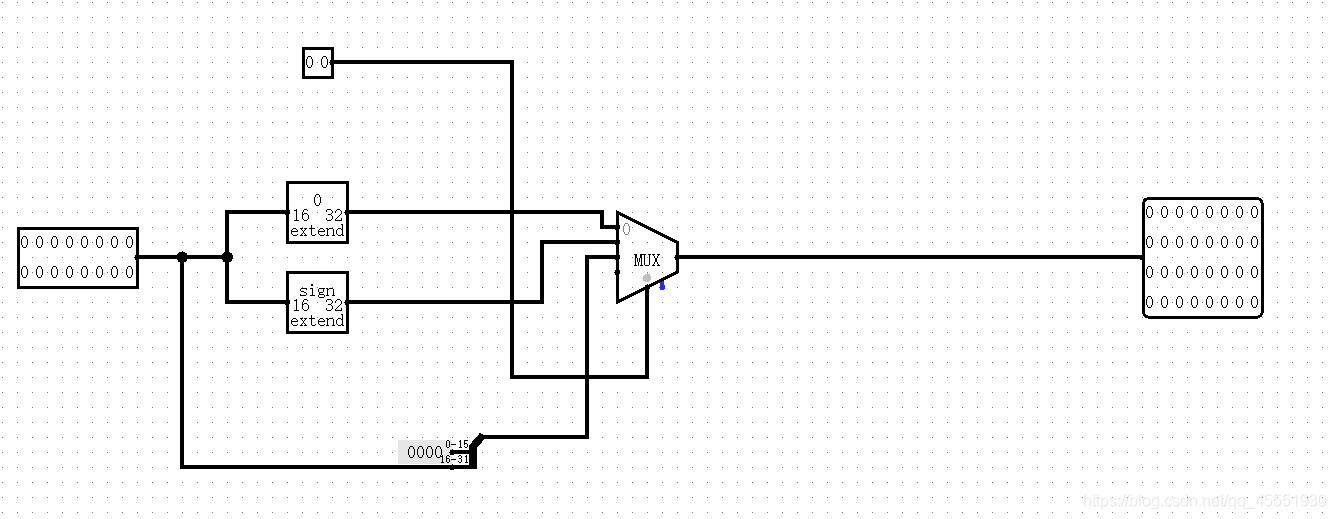

EXT

将imm16扩展后输出。由于我的lui是使用的EXT加载到高位(好像说其实应该用ALU实现?),因此我的EXT有3个功能分别是无符号扩展、符号扩展、左移16位。

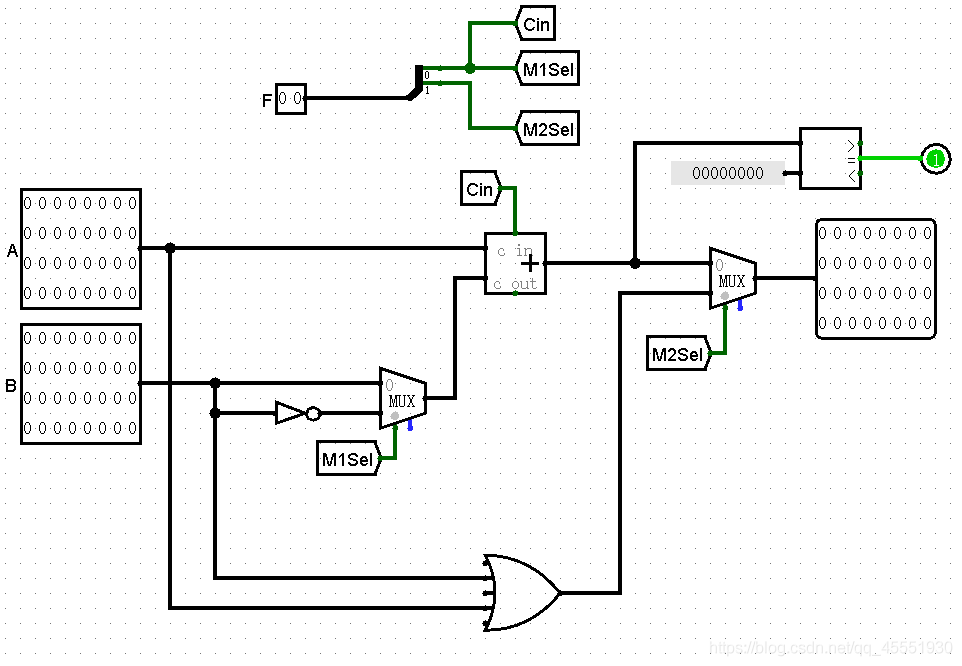

ALU

根据ALUOp进行不同的运算即可,这里加法和减法用的一个加法器(A-B=A+~B+1),但是好像这样不太好扩展(?)

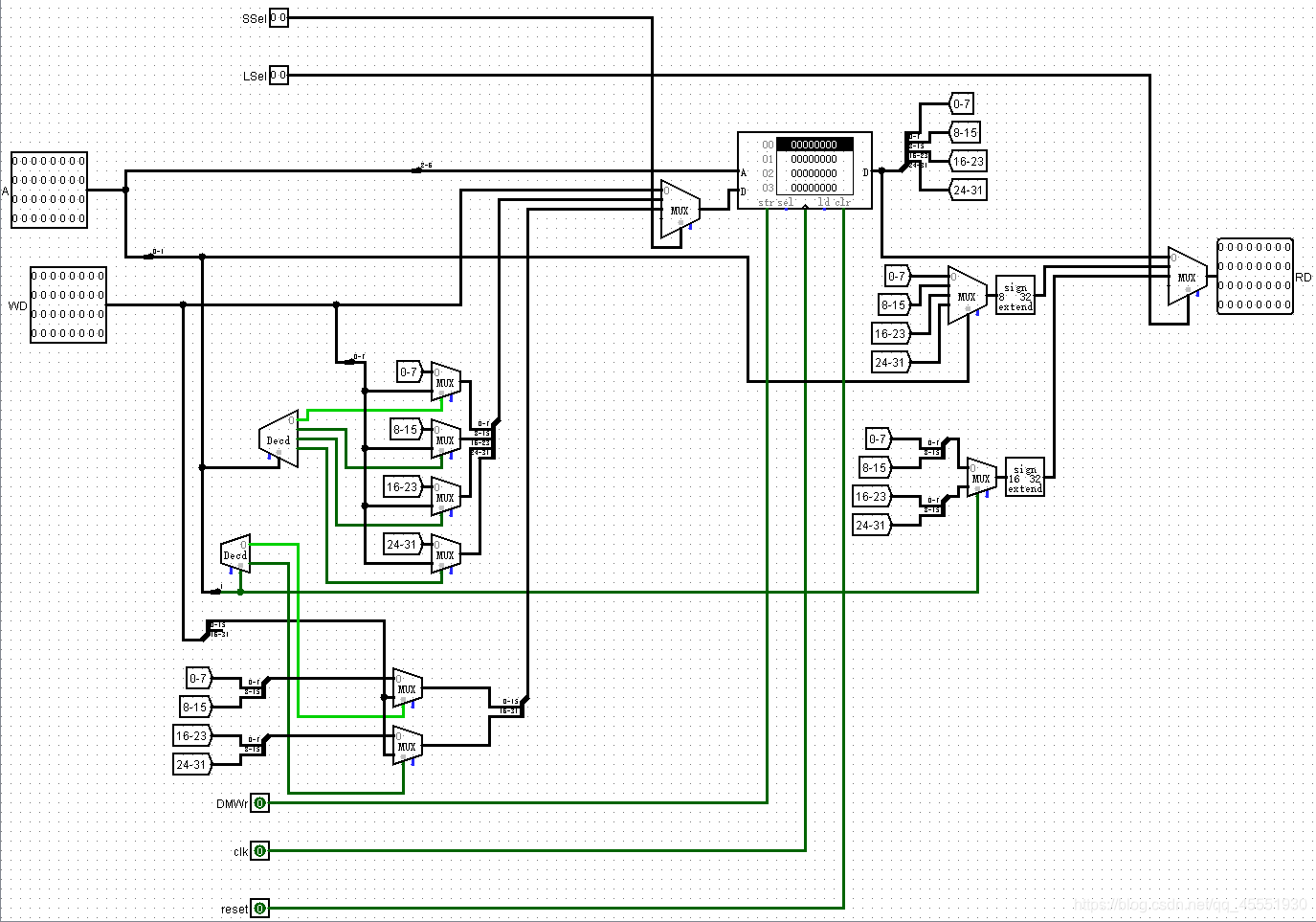

DM

本来是一个非常简单的RAM,但是由于做了lb、sb、lh、sh,就得对DM前后加上组合逻辑以保证不改变其他位的数据。这里用两个控制信号,SSel控制store时的位宽,LSel控制Load时的位宽。(其实用一个控制信号就可以,当时做的时候傻了一下用了两个)

使用一个译码器,选择被替换的那一段,如sb时,A的01位为01,那么就会将DM中的对应地址的32位数据中的815位替换成WD的低8位,再存入DM,这样就保证了仅读入一个字节而对其他位不改变,即实现了sb。

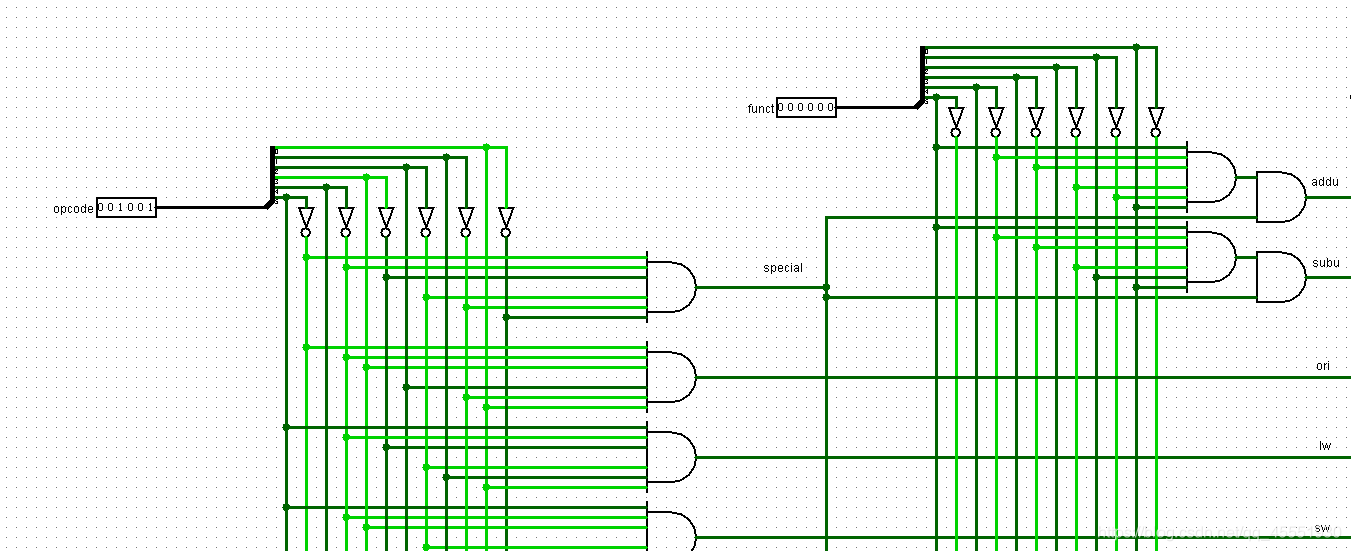

Controller

使用了最简朴的方法,搭建时可以先用小手把opcode和funct点成要添加的指令,然后再连接出该指令。如果opcode是000000,那么再与funct得出的信号并起来,即得到该指令,如图中的addu和subu。

得到指令后,再根据列的真值表,把在真值表中是1的连上

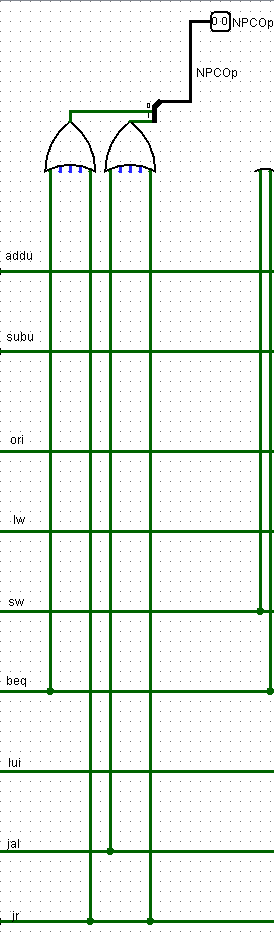

如对于NPCOp[1:0],只有beq时为01,只有jal时为10,只有jr时为11,也就是NPCOp[0]仅在beq和jr时取1,NPCOp[1]仅在jal和jr时取1,所以把他们连接起来即可,如下图。

对于每一个控制信号都如此连接,即可完成CPU的搭建。

添加指令

注意事项

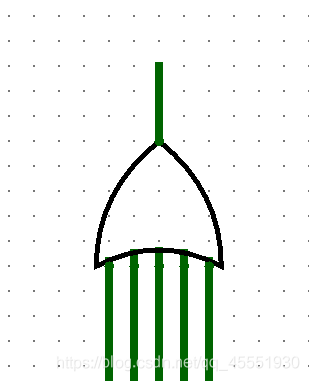

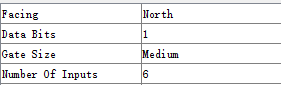

- 在改变与门或者或门的输入数据个数时,建议从奇数个到奇数个,否则可能出现这样的情况:如我有一个5input的或门,如下

现在要添加第6个input,如果直接改成6input,那么如图所示

发现中间的空掉了

而如果遵循奇数个改奇数个的原则就不会出错,如将number of input改成7就如下图所示,中间的连上了。

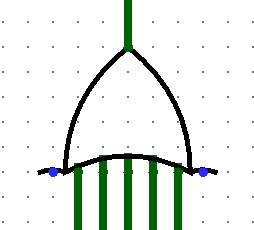

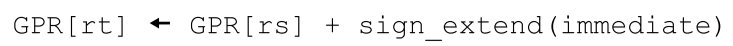

eg:添加addiu

首先分析数据通路

判断是否需要增加新的通路以实现该指令,可以看出其需要的功能我的CPU都有了,因此直接修改控制信号即可

确定控制信号

对于NPCOp,这不是一个跳转指令,因此NPCOp取00

对于RFWr,要回写到R[rt],因此RFWr为1

对于EXTOp,要进行符号扩展,所以取01

对于ALUOp,加法,所以取00

对于DMWr,不用写入DM,所以取0

对于WRSel,由于写入的是R[rt],所以取01

对于WDSel,由于写入的数据来自ALU的计算结果,所以取00

对于BSel,由于参与ALU计算的第二个数来自EXT,所以取1

对于SSel和LSel,由于不涉及半字或字节,都取00

添加指令信号

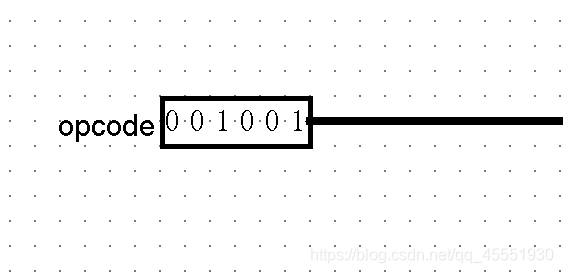

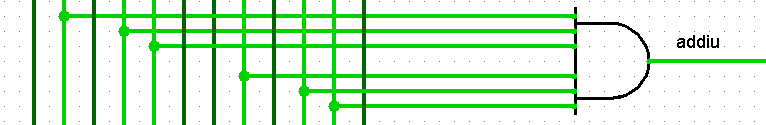

首先将opcode点成该指令

然后再连接出addiu

这时候由于opcode即addiu指令,应该只有addiu是亮的。

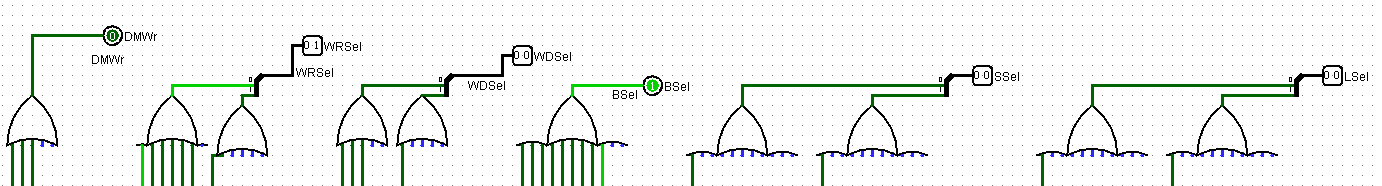

修改控制信号

得到addiu信号后,仅需要在addiu控制信号为1的对应位置连线即可,如addiu只有RFWr、EXTOp[0]、WRSel[0]、BSel为1,所以只需要将他们的或门添加一根线与addiu信号连接。连接完成后,应检查一遍此时的控制信号是否与之前分析的一样。

可以看到与之前分析的完全一样,至此addiu的添加完成。

使用logisim搭建单周期CPU与添加指令的更多相关文章

- 使用Verilog搭建一个单周期CPU

使用Verilog搭建一个单周期CPU 搭建篇 总体结构 其实跟使用logisim搭建CPU基本一致,甚至更简单,因为完全可以照着logisim的电路图来写,各个模块和模块间的连接在logisim中非 ...

- P4-verilog实现mips单周期CPU

最近对学习的掌控可能出现了问题,左支右绌,p2挂了,p2.p3.p4.p5每周在计组花的连续时间少了很多,学习到的东西也少了很多,流水线都还没真正开始写,和别人比落后了一大截,随笔自然就荒废了,我得尽 ...

- Vivado实战—单周期CPU指令分析

引言 不知道你是否和我有过同样的感受,<计算机组成原理>这门学科学起来如此的艰难:一节课下来,教室黑板上留下了满满的 "足迹",看上去也挺简单的,不就是 0 和 1 ...

- 单周期CPU设计的理论基础

写在前面:本博客内容为本人老师原创,严禁任何形式的转载!本博客只允许放在博客园(.cnblogs.com),如果您在其他网站看到这篇博文,请通过下面这个唯一的合法链接转到原文! 本博客全网唯一合法UR ...

- 单周期CPU设计

终于有点时间了,恰好多周期的设计也已经完成,其实只想写写多周期的,无奈单周期补上才好,哈哈哈~ —————+—————黄金分割线—————+————— 首先要理解什么叫单周期CPU(与后面多周期CPU ...

- 单周期cpu设计代码解读

目录 写在前面 单周期cpu设计代码讲解 概念回顾 Verilog代码讲解 写在前面 欢迎转载,转载请说明出处. 单周期cpu设计代码讲解 概念回顾 一.电子计算机的部件 分为:中央处理器(cpu). ...

- 为什么现在使用多周期CPU,而单周期CPU被弃用?

最初设计的CPU结构简单,内部不复杂.之所以制造它是为了让机器自动跑程序,算数. 早期CPU都是单周期的,人们没考虑那么多,性能啥的.就让CPU每个时钟周期跑一个指令,这些时钟周期等长.这样下来,有的 ...

- 单周期CPU

一个时钟周期执行一条指令的过程理解(单周期CPU): https://blog.csdn.net/a201577F0546/article/details/84726912 单周期CPU指的是一条指令 ...

- Verilog单周期CPU(未完待续)

单周期CPU:指令周期=CPU周期 Top模块作为数据通路 运算器中有ALU,通路寄存器(R1.R2.R3.R4),数据缓冲寄存器(鉴于书上的运算器只有R0)........... 此为ALU和通用寄 ...

随机推荐

- 常用的实现Javaweb页面跳转的方式

我们有两大种方式来实现页面跳转:1.JS(javascript):2.jsp跳转 先说jsp(金j三s胖p):1.转发:request.getRequestDispatcher("1.jsp ...

- Java 8新特性解读

(四)Java 8 相关知识 关于 Java 8 中新知识点,面试官会让你说说 Java 8 你了解多少,下面分享一我收集的 Java 8 新增的知识点的内容,前排申明引用自:Java8新特性及使用 ...

- mysql 索引的原理(超细)

一 介绍 为何要有索引? 一般的应用系统,读写比例在10:1左右,而且插入操作和一般的更新操作很少出现性能问题,在生产环境中,我们遇到最多的,也是最容易出问题的,还是一些复杂的查询操作,因此对查询语句 ...

- jdk1.8特性2

public class User { private Long id; private String userName; private String roleName; private Strin ...

- dcoker 搭建单节点redis

1.安装docker 1.检查内核版本,必须是3.10及以上 [root@localhost ~]# uname -r 2.安装docker [root@localhost ~]# yum insta ...

- 深入探究ASP.NET Core Startup初始化

前言 Startup类相信大家都比较熟悉,在我们使用ASP.NET Core开发过程中经常用到的类,我们通常使用它进行IOC服务注册,配置中间件信息等.虽然它不是必须的,但是将这些操作统一在Start ...

- 安装Mysql,开发权限,以及复制数据库

官网下载 https://downloads.mysql.com/archives/community/ 解压后安装,管理员身份打开cmd,转到mysql的bin目录,mysqld --ins ...

- SQL SERVER级联查询及数据结构《存储过程-递归树形查询》

--创建表,插入数据 create table tb(id varchar(3) , pid varchar(3) , name varchar(10))insert into tb values(' ...

- 【SpringBoot】02.编写HelloWorld

1.编写一个返回HelloWorld的Controller @Controller public class HelloWorld { @ResponseBody @RequestMapping(&q ...

- leetcode105: jump-game-ii

题目描述 给出一个非负整数数组,你最初在数组第一个元素的位置 数组中的元素代表你在这个位置可以跳跃的最大长度 你的目标是用最少的跳跃次数来到达数组的最后一个元素的位置 例如 给出数组 A =[2,3, ...