SV Interface and Program 2

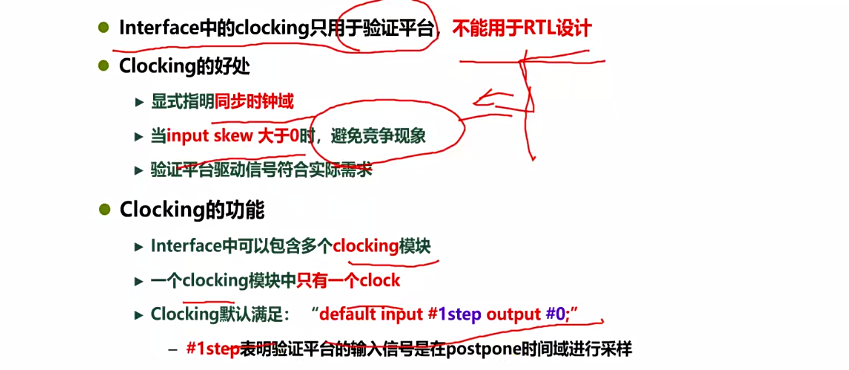

Clocking:激励的时序

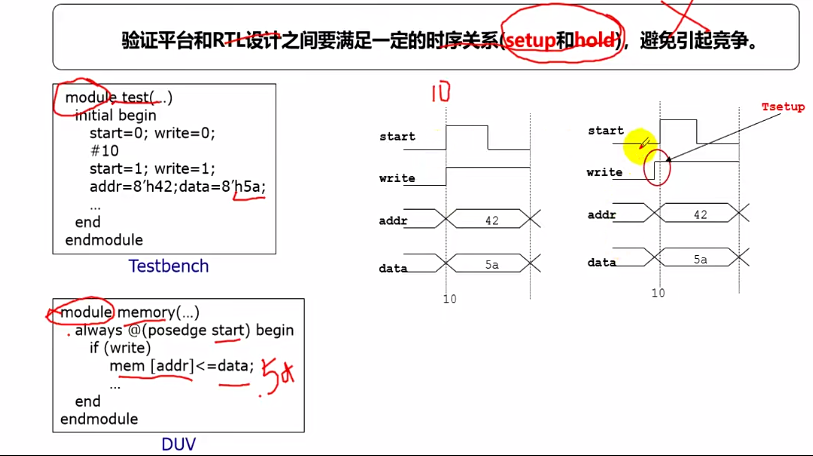

- memory检测start信号,当start上升沿的时候,如果write信号拉高之后,将data存储到mem中

- start\write\addr\data - 四个信号是同时在start上升沿进行,在采样的时候,testcase和Dut都是module,write采样的时候,有时候会采样到上升沿之前的值或者上升沿之后的值,需要规避这种情况

- 信号在时钟的驱动下发生跳变,会有delta-delay产生,并且delta-delay是不确定的,所以会造成采样的不确定性,使用clocking模块进行控制

- 需要给write信号稳定之后进行采样

- 所以设置clocking模块进行控制

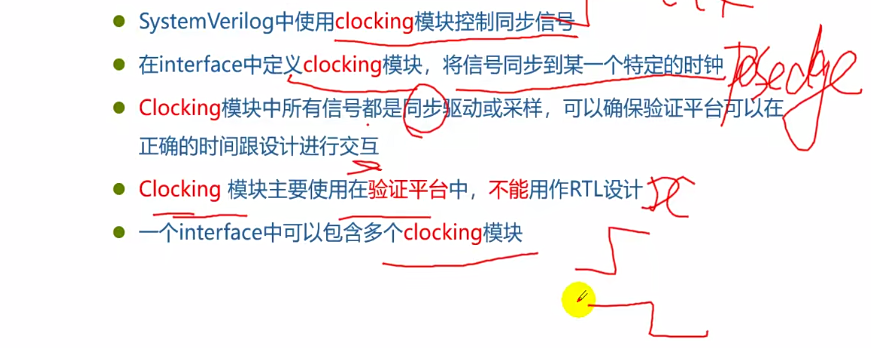

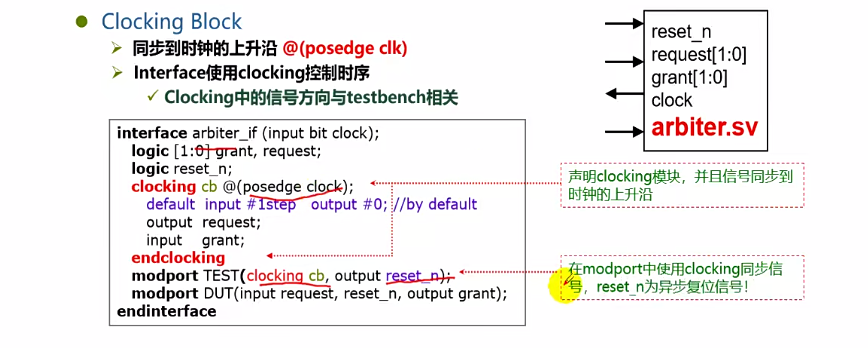

- 在clocking block定义在interface中,是不可综合的

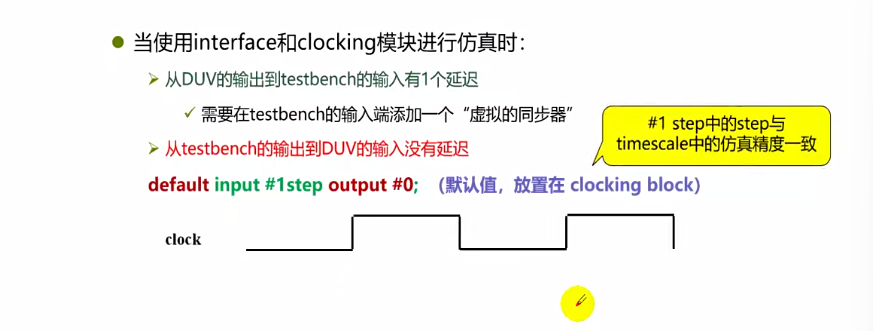

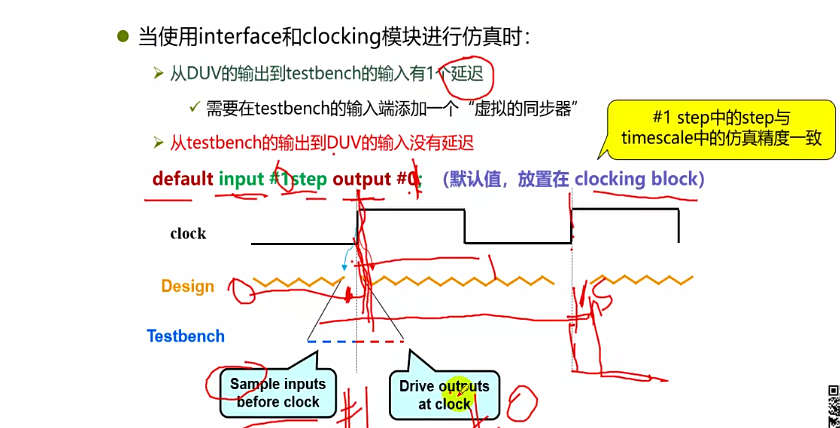

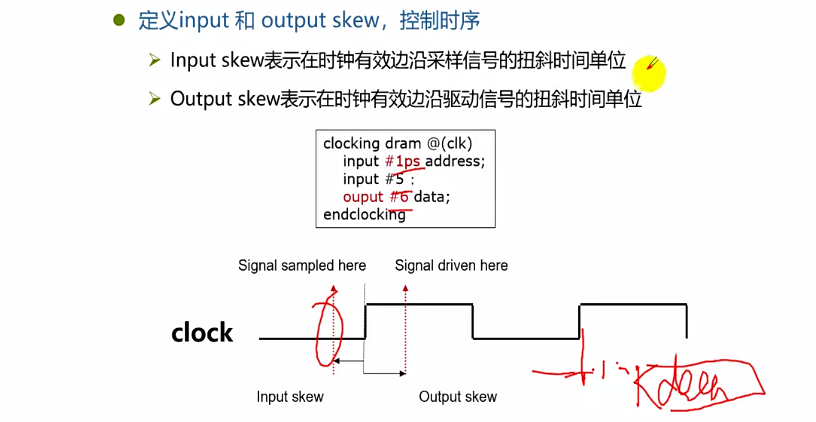

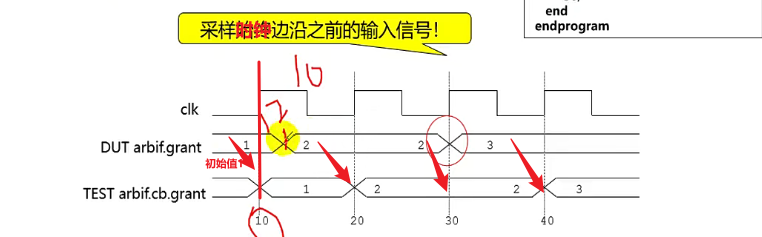

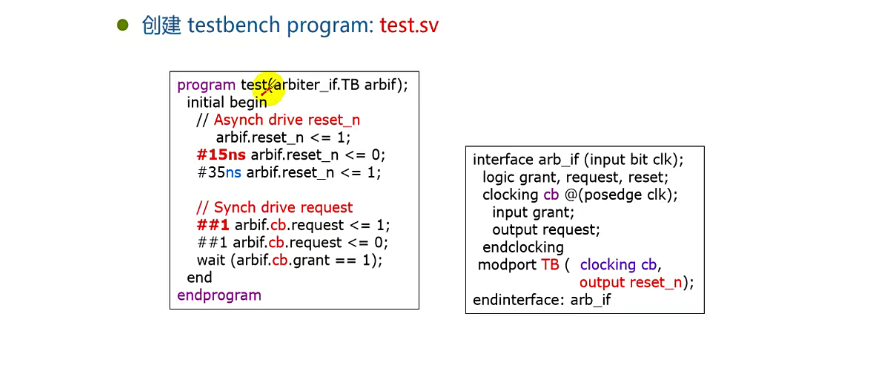

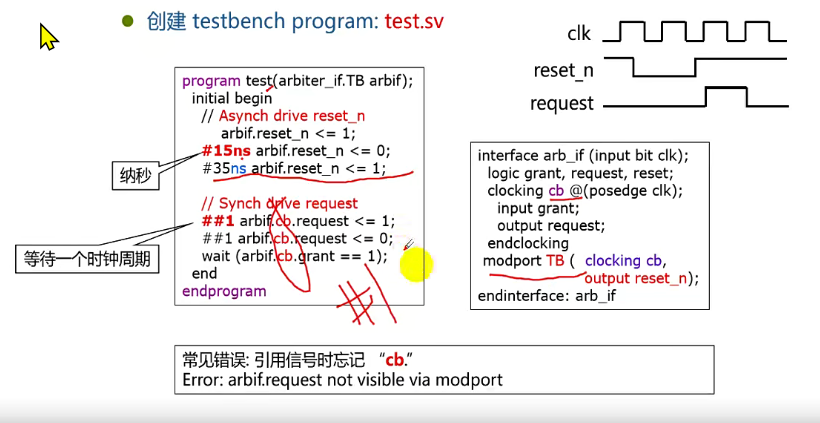

- 对于testbench,input(DUT输入)要延迟进行采样,就是在时钟上升沿之前1个时间单位采样

- output(输入给DUT) - 没有延时时间

- input向时钟上升沿之前多少时间单位进行采样,output向时钟上升沿之后多少个时间输出

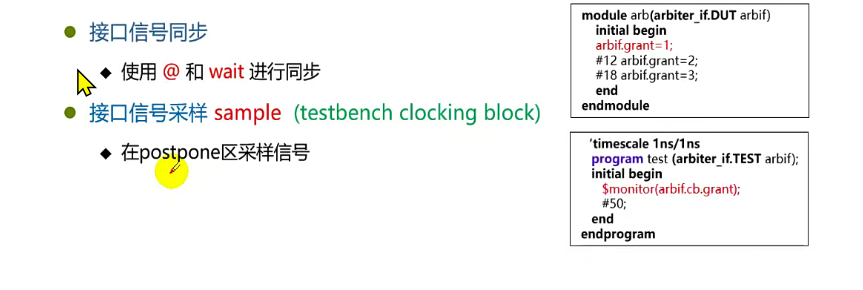

// 同步到时钟上升沿

clocking cb @(posedge)

default input #1step output #0;

output request;

input grant;

endclocking

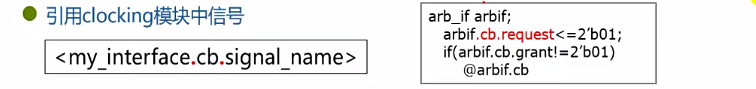

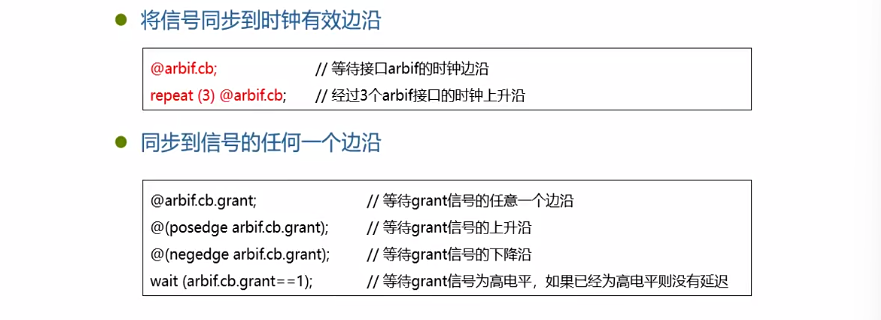

//将信号同步到时钟有效沿

@arbif.cb; // 等待接口arbif的时钟边沿

@(posedge arbif.clk) //等待接口arbif的时钟边沿

repeat(3) @arbif.cb; // 经过3个arbif接口的时钟上升沿

// 等待n个时钟周期 ##n - 阻塞语句

##2 arbif.cb.request <= 0; // 经过两个时钟周期之后进行赋值

- 同步信号,驱动输出信号使用非阻塞赋值,采样输入信号使用输入信号

- 非同步信号,阻塞赋值

forever begin

if(request == 1)

grant <= 1; // forever中没有时间推进语句,会造成死循环

end

总结

- Clocking模块中信号的方向与testbench相关

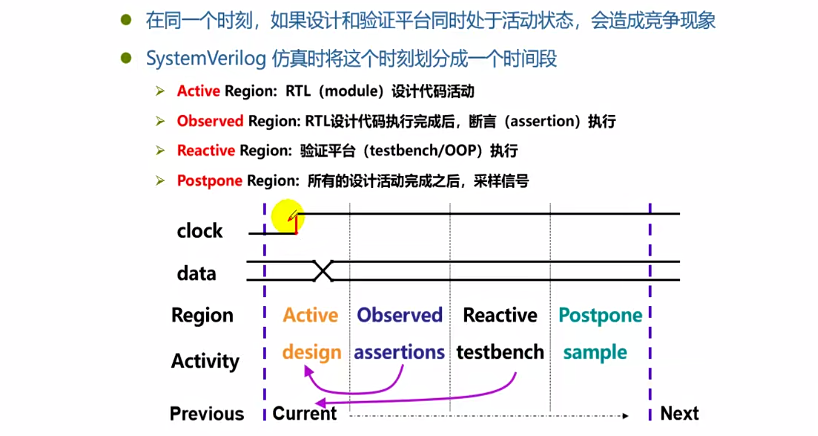

仿真时间域

- 不同代码的执行是有先后顺序的

- active region - 执行设计代码

- observed region - 执行断言

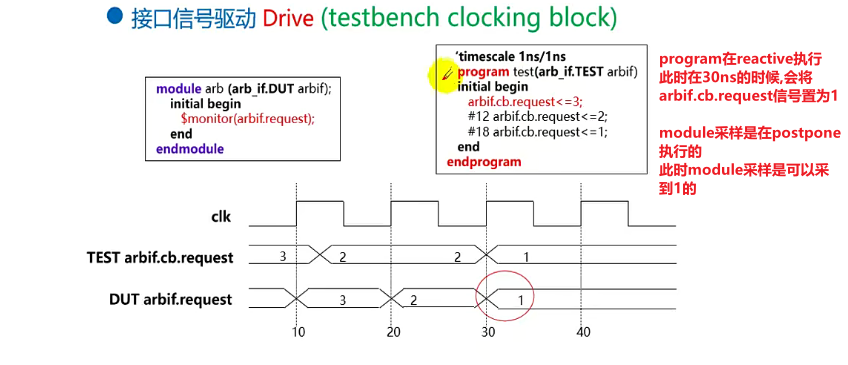

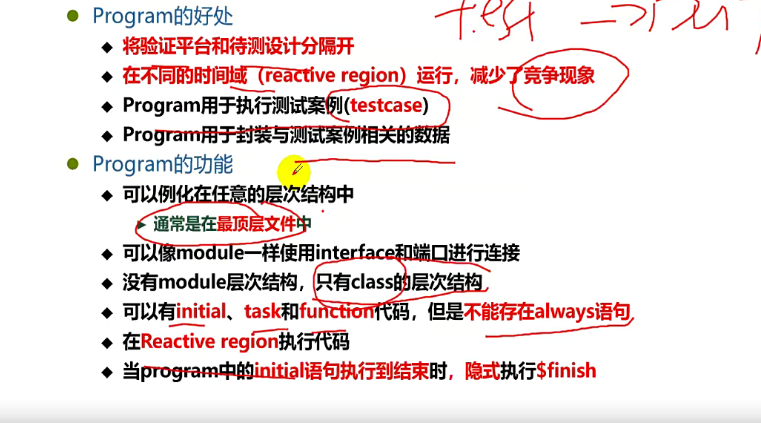

- Reactive region - testbench/oop,验证平台和dut都是module,仿真工具如何区分,testbench会用program进行定义,program可以认为是testbench

- Postpone region - sample

- program - 会在reactive region进行执行

- module - 会在active region进行执行

- 采样的时候采样到的是时钟之前的信号

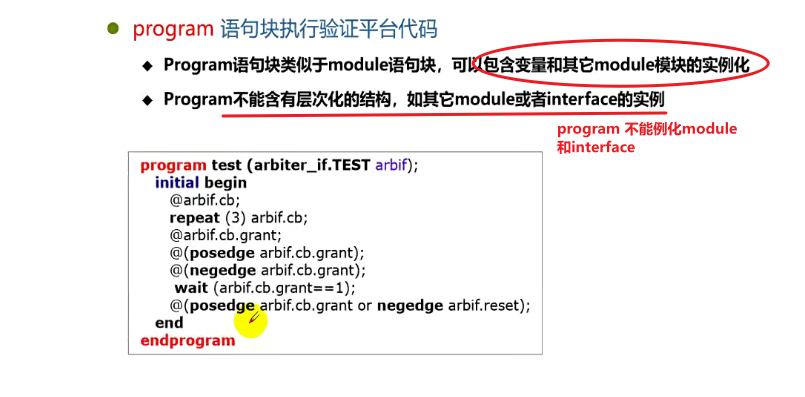

Program block

- program语句只能用于testbench,不能用于design

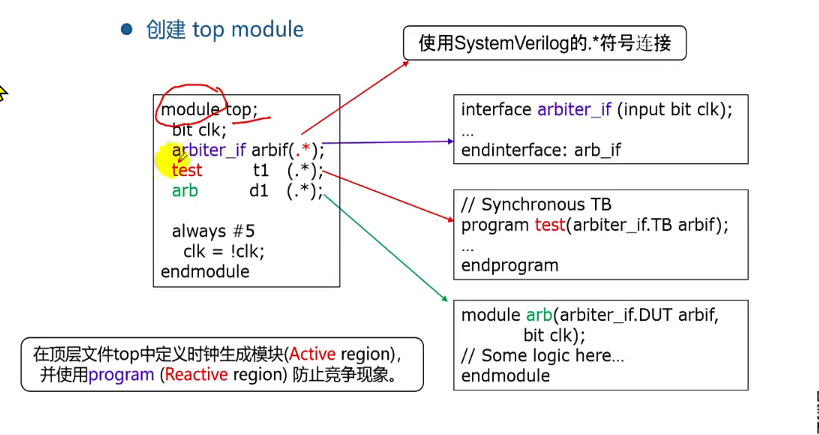

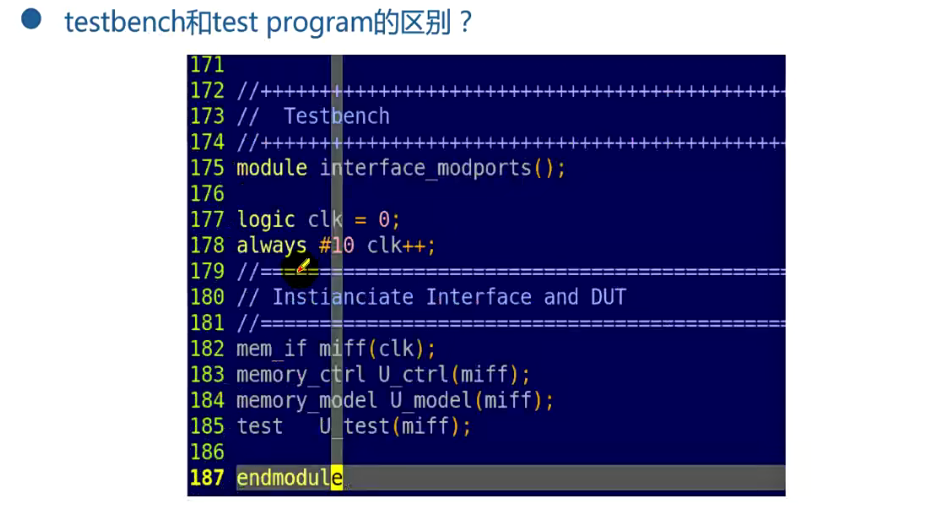

验证平台顶层文件-top文件

- tb_top必须是module

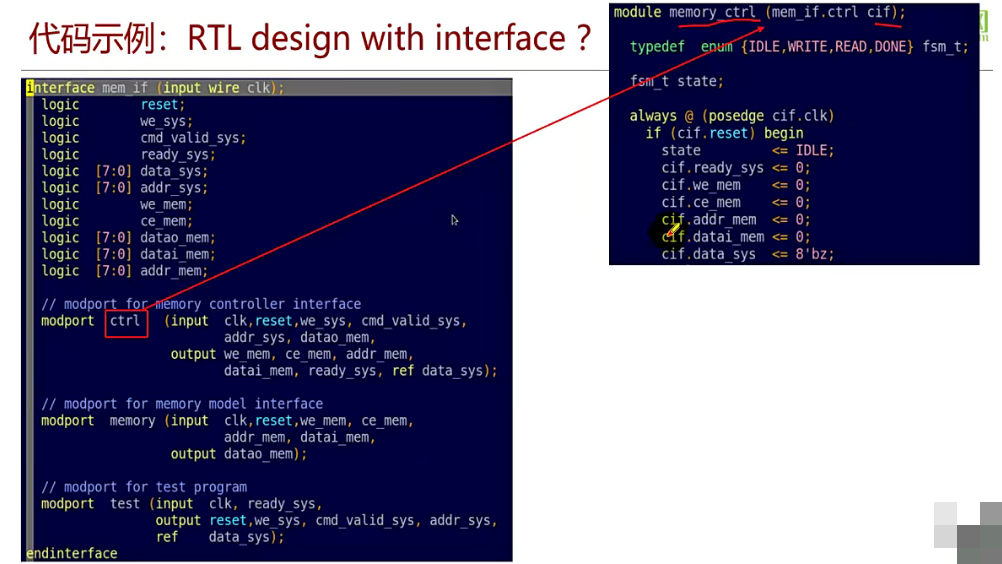

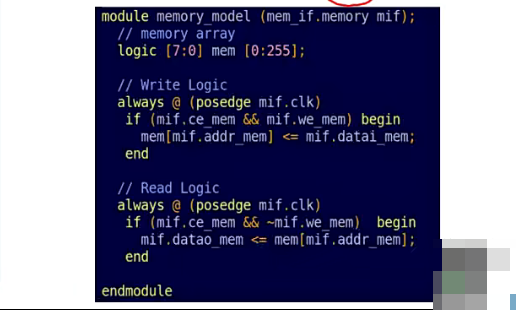

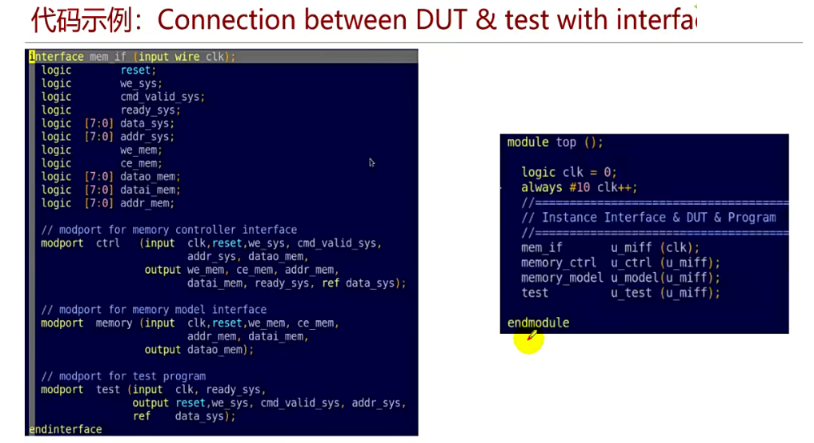

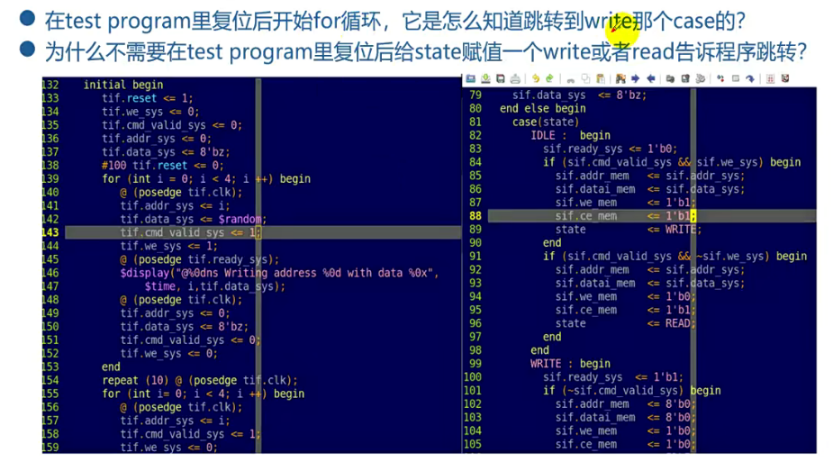

代码示例

SV Interface and Program 2的更多相关文章

- SV中的Interface和Program

Interface:SV中新定义的接口方式,用来简化接口连接,使用时注意在module或program之外定义interface,然后通过'include来添加进工程. interface arb_ ...

- program与module

program,各方面与module都类似,其中声明的变量在program中都可见, 生命周期也是static类型的, program的结束,也是需要等待其中的所有initial块都执行结束. 与mo ...

- sv命令空间 packge

SV中的module,interface,program,checker,都提供declaration空间,内部定义都local当前的那个scope,相互之间的building block不影响,不识 ...

- Tun/Tap interface tutorial

Foreword: please note that the code available here is only for demonstration purposes. If you want t ...

- C# explicit interface implementation(显式接口实现)

C# explicit interface implementation 某个类要实现两个包含相同方法名的接口, 应该如何实现这两个方法? namespace ExplicitInterfaceImp ...

- 如何搭建SoC项目的基本Testbench【zz】

原文地址:http://bbs.eetop.cn/thread-442797-1-8.html 写这个文档的目的是让大家对搭建SoC项目的Testbench有一个比较清晰的认识,可以根据这个文档来一步 ...

- Systemverilog for design 笔记(六)

转载请标明出处 第一章 有限状态机建模(FSM,finite state machine) 1.1. 使用枚举类型建立状态机模型 l 三过程块建模风格:三个过程块分别实现: a.状态转换(al ...

- Systemverilog for design 笔记(一)

转载请标明出处 一. System Verilog 声明的位置 1. 包(packages) Verilog要求局部声明: variables, nets, tasks and f ...

- A web crawler design for data mining

Abstract The content of the web has increasingly become a focus for academic research. Computer prog ...

- C语言代写

MTRX1702 - C ProgrammingAssignment 2This assignment requires you to design and build a program that ...

随机推荐

- Cesium被接入数字孪生系统后会发生怎样的改变?

众所周知,Cesium凭借其开源免费的特点一直垄断着整个三维GIS的生态系统,但是随着数字孪生技术的发展以及各项新需求的不断涌现,Cesium与数字孪生系统相结合的潜力也逐渐凸显. 一般而言,Cesi ...

- Java多线程学习(Day02)

目录 线程简介 线程实现(重点) 线程状态 线程同步(重点) 线程通信问题 线程实现: 方式一:继承Thread类 /** * TODO * @author 清莲孤舟 * @CreateDate 20 ...

- java注释、变量、数据类型和运算符

注释 单行注释:// 多行注释:/*开头,*/结尾 JavaDoc注释:/**开头,*/结尾 快捷键:ctrl + ? 变量 第一步:声明变量.即根据数据类型在内存分配空间. 第二步:赋值.即将数据的 ...

- Windows手工入侵排查思路

文章来源公众号:Bypass Windows系统被入侵后,通常会导致系统资源占用过高.异常端口和进程.可疑的账号或文件等,给业务系统带来不稳定等诸多问题.一些病毒木马会随着计算机启动而启动并获取一定的 ...

- 使用 vve-i18n-cli 来一键式自动化实现国际化

[Github:vue-viewer-editor/vve-i18n-cli] 这是我同事开发的国际化自动处理脚本,我进行过一次扩展,让其也支持我们一个 jQuery 老项目的国际化日常维护 至此,我 ...

- Python用辗转相除法计算两数的最大公约数和最小公倍数

计算最大公约数运用辗转相除法就行了 计算最小公倍数需要运用公式:最小公倍数=数字1*数字2/最大公约数 有关辗转相除法的知识请查看:辗转相除法 以下为代码: #计算最大公约数 def gys (x,y ...

- 26、Flutter中命名路由

Flutter 中的命名路由 main.dart中配置路由 void main() { runApp(MaterialApp( theme: ThemeData( appBarTheme: const ...

- hiveSQL常见专题

SQL强化 SQL执行顺序 --举例: select a.sex, b.city, count(1) as cnt, sum(salary) as sum1 from table1 a join ta ...

- Llama2-Chinese项目:7-外延能力LangChain集成

本文介绍了Llama2模型集成LangChain框架的具体实现,这样可更方便地基于Llama2开发文档检索.问答机器人和智能体应用等. 1.调用Llama2类 针对LangChain[1]框架 ...

- 初窥门径代码起手,Go lang1.18入门精炼教程,由白丁入鸿儒,首次运行golang程序EP01

前文再续,书接上回,前一篇:兔起鹘落全端涵盖,Go lang1.18入门精炼教程,由白丁入鸿儒,全平台(Sublime 4)Go lang开发环境搭建EP00,我们搭建起了Go lang1.18的开发 ...