VHDL之package

Pacakge

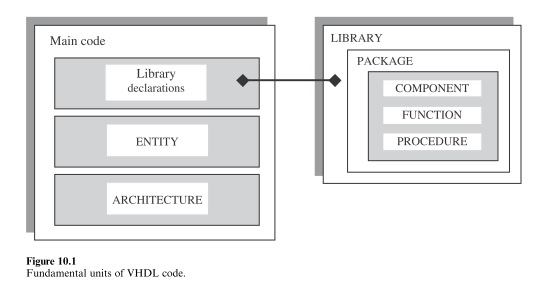

Frequently used pieces of VHDL code are usually written in the form of COMPONENTS, FUNCTIONS, or PROCEDURES. Such codes are then placed inside a PACKAGE and compiled into the destination LIBRARY.

1 Syntax

Besides COMPONENTS, FUNCTIONS, and PROCEDURES, it can also contain TYPE and CONSTANT definitions, among others. Its syntax is presented below.

PACKAGE package_name IS

(declarations)

END package_name; [PACKAGE BODY package_name IS

(FUNCTION and PROCEDURE descriptions)

END package_name;]

2 Simple Package

It shows a PACKAGE called my_package. It contains only TYPE and CONSTANT declarations, so a PACKAGE BODY is not necessary.

------------------------------------------------

LIBRARY ieee;

USE ieee.std_logic_1164.all;

------------------------------------------------

PACKAGE my_package IS

TYPE state IS (st1, st2, st3, st4);

TYPE color IS (red, green, blue);

CONSTANT vec: STD_LOGIC_VECTOR( DOWNTO ) := "";

END my_package;

------------------------------------------------

The PACKAGE above can now be compiled, becoming then part of our work LIBRARY (or any other). To make use of it in a VHDL code, we have to add a new USE clause to the main code (USE work.my_package.all), as shown below.

------------------------------------

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE work.my_package.all;

------------------------------------

ENTITY...

...

ARCHITECTURE...

...

------------------------------------

3 Package in ASIC

In ASIC design, use ieee.std_logic_1164, and ieee.numeric_std, NEVER use ieee.std_logic_arith

numeric_std defines numeric types and arithmetic functions for use with synthesis tools.

- two numeric types are defined: UNSIGNED, SIGNED (represents a SIGNED number in vector form)

- base element type is type STD_LOGIC. The leftmost bit is treated as the most significant bit.

- signed vectors are represented in two's complement form.

- contains overloaded arithmetic operators on the SIGNED and UNSIGNED types.

- contains useful type conversions functions.

VHDL之package的更多相关文章

- 第二章:systemverilog声明的位置

1.package 定义及从package中导入定义(***) verilog中,对于变量.线网.task.function的声明必须在module和endmodule之间.如果task被多个modu ...

- VHDL学习札记:library and Package

参考:http://www.cnblogs.com/garylee/archive/2012/11/16/2773596.htmlhttp:// http://forums.xilinx.com ...

- 让WPS支持VHDL的关键词加粗

WPS的VBA在这里下载:http://bbs.wps.cn/forum.php?mod=viewthread&tid=22347925 语法高亮是参考Word的,这篇文章:http://bl ...

- VHDL学习之TEXTIO在仿真中的应用

TEXTIO 在VHDL 仿真与磁盘文件之间架起了桥梁,使用文本文件扩展VHDL 的仿真功能.本文介绍TEXTIO 程序包,以一个加法器实例说明TEXTIO 的使用方法,最后使用ModelSim 对设 ...

- VHDL基础2

Signals & Variables VHDL 提供了 signal 和 variable 两种对象来处理非静态数据:提供了 constant 和 generic 来处理静态数据. cons ...

- VHDL基础1

Description Structure 一个可综合的VHDL描述中一般由3部分组成:LIBRARY declarations.ENTITY.ARCHITECTURE Library(库)用来设计重 ...

- 基于VHDL利用PS2键盘控制的电子密码锁设计

基于VHDL利用PS2键盘控制的密码锁设计 附件:下载地址 中文摘要 摘 要:现代社会,人们的安全意识正在不断提升.按键密码锁由于其具有方便性.低成本等特征,还是大有用武之地的.但是通常的按键密码锁开 ...

- 毕业设计预习:VHDL入门知识学习(一) VHDL程序基本结构

VHDL入门知识学习(一) VHDL程序基本结构 简介 VHDL程序基本结构 简介 概念: HDL-Hardware Description Language-硬件描述语言-描述硬件电路的功能.信号连 ...

- VHDL入门学习-程序组成

1. VHDL程序的组成 一个完整的VHDL程序是以下五部分组成的: 2. 库(LIBRARY):比较好理解,调用系统已有的库,WORK库就是用户当前编辑文件所在的文件夹, IEEE库:由IEEE(美 ...

随机推荐

- 【剑指Offer】10、矩形覆盖

题目描述: 我们可以用2 X 1的小矩形横着或者竖着去覆盖更大的矩形.请问用n个2 X 1的小矩形无重叠地覆盖一个2 X n的大矩形,总共有多少种方法? 解题思路: 我们可以以2 X ...

- Linux—Ubuntu14.0.5安装gitlab

1.下载gitlab-ce,到该连接选择版本 https://mirror.tuna.tsinghua.edu.cn/gitlab-ce/ubuntu/pool/trusty/main/g/git ...

- NFS实时备份

方法一(inotify+rsync): 1.安装inotify-tools(客户端)[监听工具],实现数据属实备份检查目录是否有如下文档,没有表示操作系统不支持 ls -l /proc/sys/fs/ ...

- mongodb集群搭建(分片+副本)

原文地址:https://www.cnblogs.com/ityouknow/p/7344005.html 相关概念 先来看一张图: 从图中可以看到有四个组件:mongos.config server ...

- 学习EXTJS6(2)“Hello Usegear”

由于零基础,extjs6的资料不够多,所以直接动手困难不少.<Extjs Web应用程序开发指南>机械出版社虽然有点老,但是用于学习一步一步动手实践还是相当不错的.用的是extjs4.0. ...

- 1013MySQL监控利器-Innotop

转自 http://www.cnblogs.com/ivictor/p/5101506.html 安装过程中 可以使用 YUM INSTALL INNOTOP进行直接安装 Innotop是一款十分强大 ...

- 洛谷 P1649 [USACO07OCT]障碍路线Obstacle Course

P1649 [USACO07OCT]障碍路线Obstacle Course 题目描述 Consider an N x N (1 <= N <= 100) square field comp ...

- 收到微软寄来的MVP包裹

经过一年多的艰苦努力,最终在7月份获得了微软SharePoint的MVP. 今天收到了微软从美国寄来的包裹. 内部图: 奖牌: 回忆过去一年.白天和客户撕逼,晚上回家写博客,或者翻译英文文章,去论坛回 ...

- TensorFlow 入门之手写识别(MNIST) softmax算法 二

TensorFlow 入门之手写识别(MNIST) softmax算法 二 MNIST Fly softmax回归 softmax回归算法 TensorFlow实现softmax softmax回归算 ...

- PHP扩展开发--实验成功

原文:http://kimi.it/496.html http://blog.csdn.net/u011957758/article/details/72234075 ---------------- ...