zigzag走线原理及应用

电路板上弯弯扭扭的走线有什么用

往期文章:

前面几篇文章有部分读者反馈太深奥,不好懂,要求来一点轻松易懂的。这不,它来了!本期文章我们来分享近期工作中的一个小故事。

一段奇怪的走线

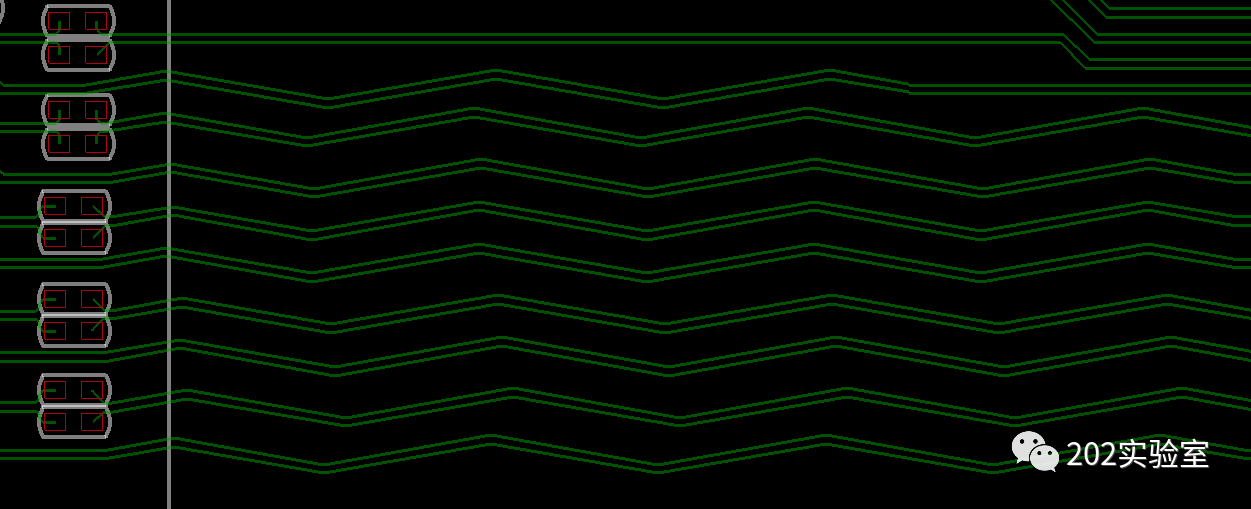

这一天,工程师小明像往常一样的在日常撸(摸)板(鱼)。这时,同事小红拿着一个看似奇怪的走线来问小明,小明看了看走线,大概是下面这个样子:

小红问道:这个弯弯扭扭的走线有什么作用呀?我们的layout规范不是要求尽量走直线,少拐弯吗?

小明看着这个走线,的确有点奇怪,再看了看信号的作用,这是一组PCIe Gen3的高速信号,是差分对的走线形式。那这个走线有什么用呢,是绕线做等长?小明还是有点经验的,看了看觉得不太像,一般等长没这种绕法呀!是为了好看或者为了显得高深?这好像也不好看呀,一时间仿佛陷入了知识盲区。再看看小红迷茫的眼神,两人相顾无言,唯有眼迷茫。

小明有个特点,就是容不得疑点存活。于是小明立马进入了百度、Google、文献检索的过程。不过,就一张图,该怎么描述,怎么检索呢?再加上某度铺天盖地的广告和结果中一模一样铺天盖地的软文,鲜有收获。

功夫不负有心人。终于,小明检索到了一篇叫“PCB Dielectric Material Selection and Fiber Weave Effect on High-Speed Channel Routing”的文献,文章来自于有名的FPGA厂商Altera,在这里面看到了与上面图片里类似的走线。小明吃力的啃起了这篇全英文的APN。小明读完后写下了这篇读后感。

玻纤编织效应(Fiber Weave Effect)

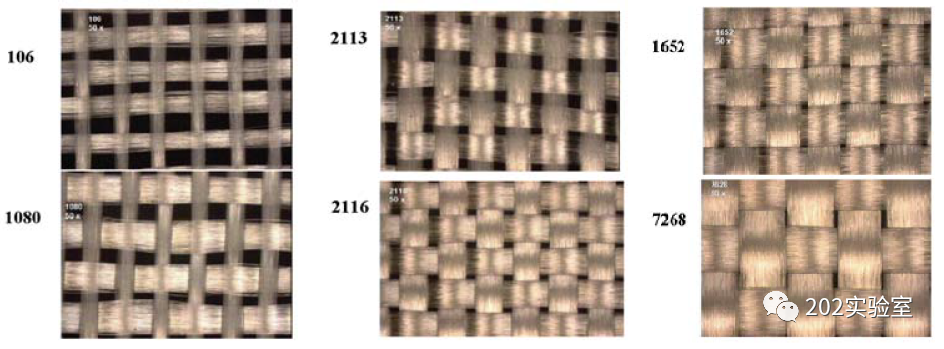

首先标题里出现了一个词:Fiber Weave Effect,翻译过来是纤维编织效应,看来这事可能跟纤维和纤维编织有关。我们知道PCB基板是由玻璃纤维和环氧树脂填充混合制成的,与PCB有关的纤维自然是玻璃纤维了。不同规格的PCB板材,玻璃纤维的规格和编织密度是不一样的,在显微镜下,可以看到不同PCB基板的微观结构,如下图所示:

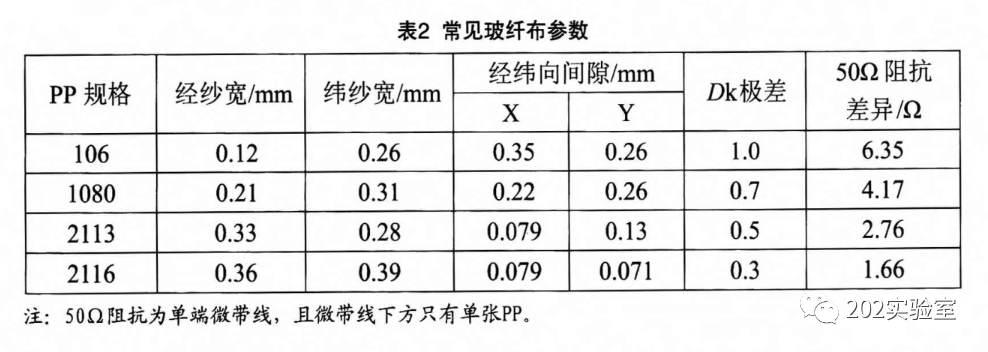

常见玻纤布的参数如下表所示,不同编制的参数差异比较明显。

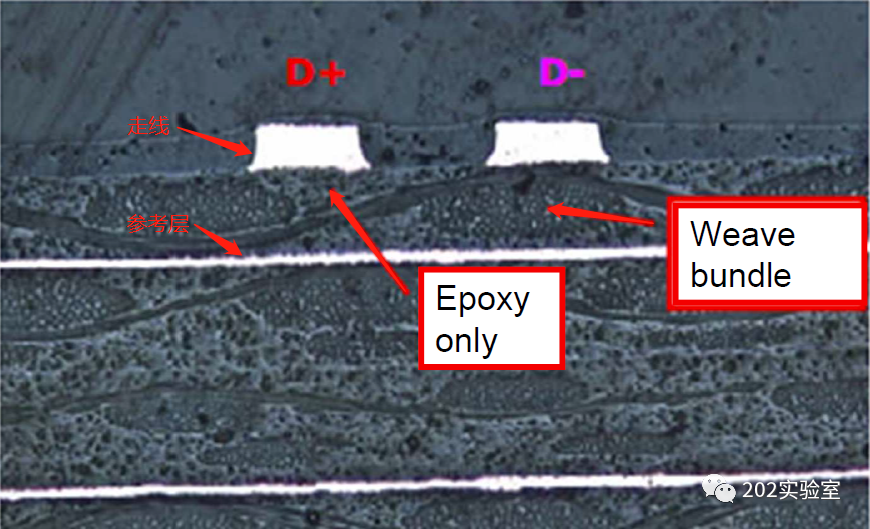

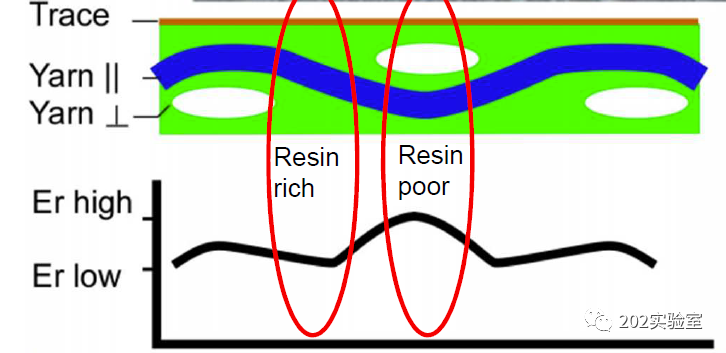

看到这里不禁要问,这样子的结构有什么问题吗?对于PCB板上传输的数字信号来说,包括广泛使用的FR4等许多的电介质材料在内,在低速低频传输时,一直被认为是均匀的。但当系统中信号速率达到Gbps级别时,这种均匀性假设可能不再成立,此时交织在环氧树脂基材中的玻璃纤维束之间的间隙引起的介质层相对介电常数的局部变化将变得不可忽视,回想下前几期文章中有关特性阻抗和传输线延时的推导,很多关键参数都与介质的介电常数直接相关。介电常数的局部扰动将使线路的时延和特征阻抗与空间相关,从而影响高速信号的传输。下图展示了显微镜下的PCB截面示意图:

可以看到,由于玻璃纤维的编织网格导致的介质不均,导致在D+走线的下方仅有树脂填充,而在D-走线下方仅有玻璃纤维束作为填充。由于这两种材料的介电常数不一样,这就导致了D+和D-走线的特性阻抗的不一致,同时这两条走线的延时也不一致。以上结构示意如下:

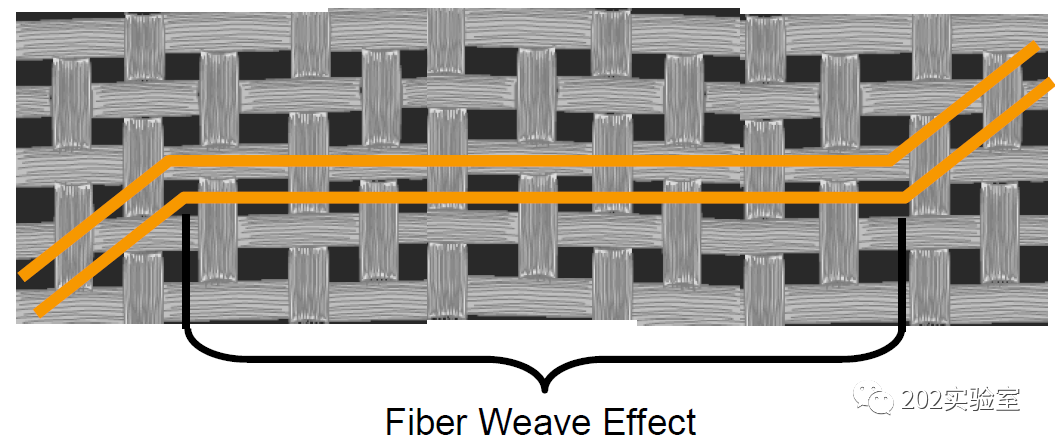

当在PCB上有水平或者垂直走线时,走线将与玻璃纤维的走向平行。在差分走线时,考虑一种极限情况,假如一条走线恰好经过玻纤上方与玻纤平行,而差分线的另一条刚好走在了空隙上,那么,这时候两条线下方的介质将会有最大的介电常数偏差,对信号的影响也将达到最大。

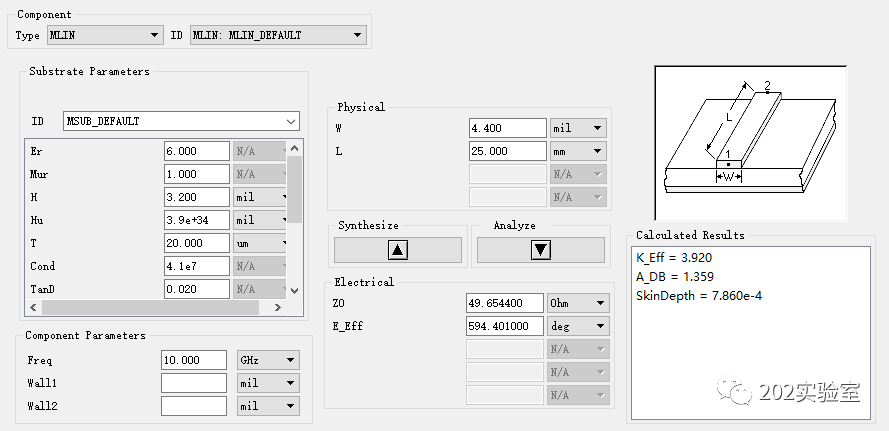

我们通过ADS建模来仿真一下介电常数对阻抗及延时的影响。通常,环氧树脂的介电常数在3左右,而玻璃纤维的介电常数在6左右,PCB介质层的介电常数取决于玻璃纤维和树脂在介质层中所占的体积比。为了比较接近最差的真实情况,仿真中我们设置一种基材的介电常数为4,而另一种的介电常数为6,如下图所示。

传输线我们采用了微带线,微带线特性阻抗为50,线宽通过ADS的"LineCalc"工具计算得出:

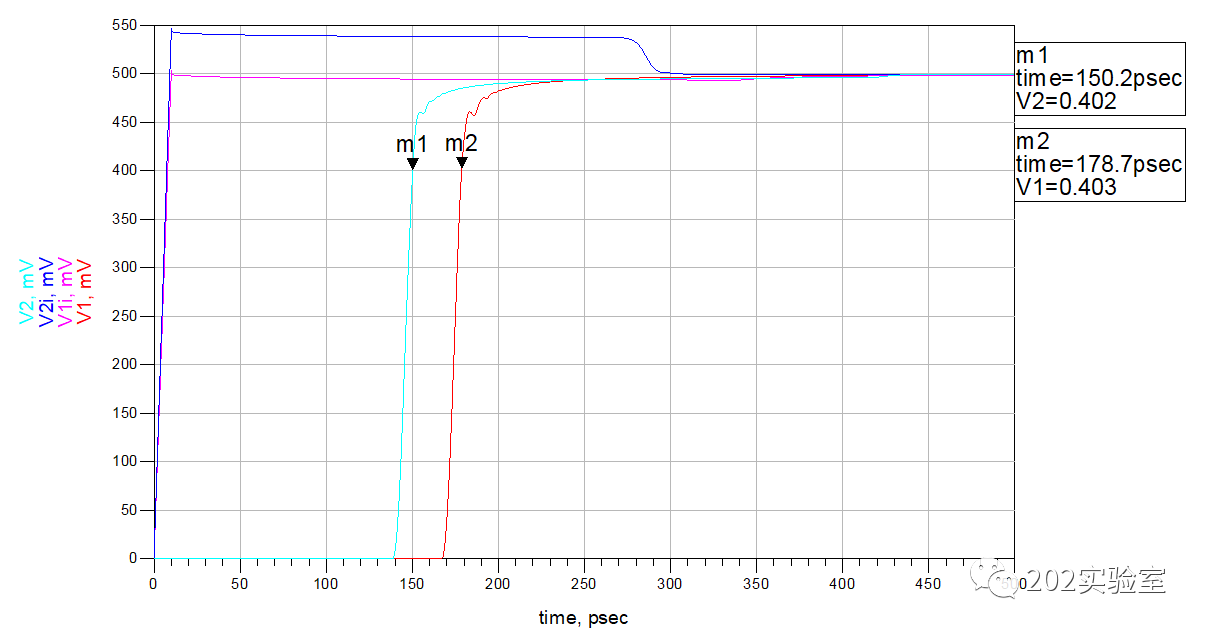

仿真结果见下图:

可以看到,信号的80%上升时间有明显的差异,V1相对于V2时间长了约28pS。由于仿真中我们设置传输线的长度为1英寸(25.4mm),因此我们基本可以得出结论,这种情况下,玻纤上方的传输线的信号传播速度比树脂上方信号线的速度慢了大约28ps/英寸。仿真结果中还有一个明显的不同,那就是源端出射信号的幅度也有所不同,树脂上方信号线的出射电压比玻纤上方的信号出射电压高约40mV,这是由于二者的特性阻抗不同导致的。回想一下反射系数推导一文,你能根据波形算出这两个传输线的特性阻抗分别是多少吗?

至此,我们基本搞清楚了PCB基板由于介质的不均匀性,会导致介质的介电常数不均。在高速信号的场合,由于这种微观上的介质分布不均,会导致传输线的阻抗和延时特性也有所不同。我们称为玻纤编织效应。

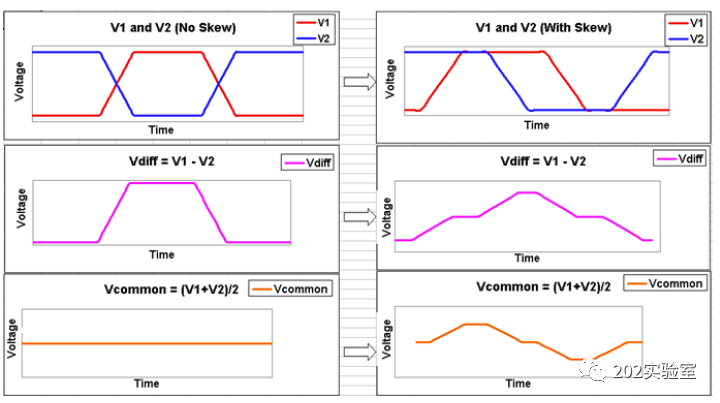

那么,这种被称之为玻纤编织效应的现象,对我们的信号会造成什么样的损害呢?结合我们的仿真数据,以及下图的简要说明,应该能基本说明问题:

正常情况下,差分对的两根信号线上传输了大小相等极性相反的差模信号,如果两根差分线的特性相同,那么接收端的波形也是大小相等极性相反的差模信号,解差分之后,信号将被完整恢复,由于绝对的对称性,不存在差模向共模的转换,因此接收端也不存在共模信号;但是,由于介质不均导致的阻抗特性和延时特性的不同,传输线上将出现一定的信号反射,这将导致接收端波形的失真,同时还会出现差分信号的偏斜,导致时序的对称性被破坏,这还将导致部分信号从差模向共模的转换。它们将导致信号完整性问题和辐射问题。我们同样可以通过仿真结果看到这一点。

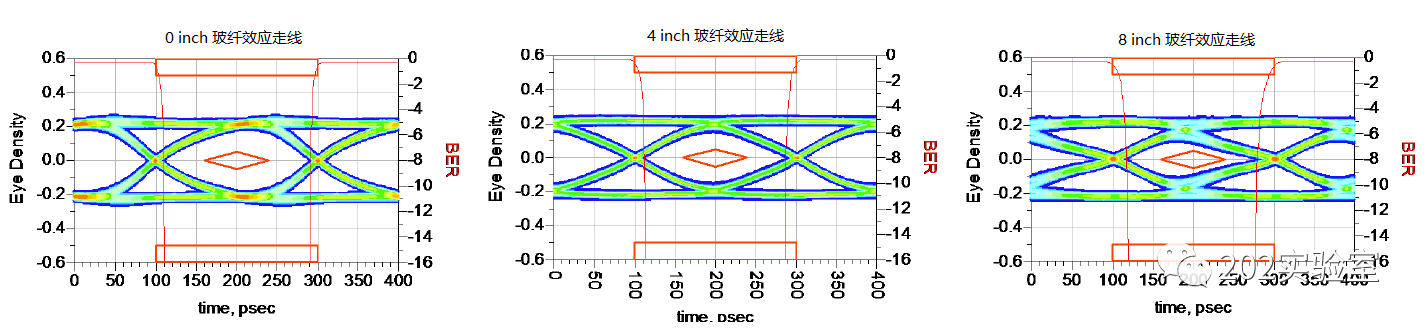

还有一个问题也值得引起注意,当信号速率达到多少时我需要关心玻纤编织效应?intel对此做了大量的测试,其数据表明,当数据速率达到8Gbps以上时,必须慎重处理玻纤编织效应。不过,笔者认为,考虑到材料的特性及加工能力参差不齐,在条件允许的情况下,5Gbps以上的信号最好都按照玻纤编织效应的要求来处理。下图展示了差分信号在8/10Bit编码,数据速率为5Gbps的情况下,玻纤效应对信号眼图的影响,可以看到,随着传输线长度的增长,眼图逐渐变差(眼高变低,眼皮变厚)。

如何解决玻纤效应带来的问题

明白了玻纤效应带来的问题后,就可以采用一些针对性的措施来解决这些问题。一般有如下几种办法:

改变玻纤编织的密度 改用低值的玻纤材料 改变走线宽度,使远比编织间隙宽 改变走线的角度,使之不与玻纤平行 采用之字形(zigzag)走线

首先,我们知道玻纤编织效应是由于玻纤和树脂介质分布不均而导致的,那么,通过改变介质的加工工艺和材料,在一定程度上一定可以改善这种效应。就比如106编织和7628编织相比,7628编织将明显改善介电常数分布不均的问题。其次,如果玻纤和树脂的介电常数差异越大,则他们所导致的介电常数分布不均的问题也将越大,通过使用低值的玻纤材料,也可以改善介电常数分布不均问题。不过,我们都知道一分钱一分货,好的东西价格也贵呀!因此,这两种措施的成本增加都很明显,作为研发工程师,不到万不得已,这显然不是最优选择。

改变走线宽度在RF电路的layout中经常用到,这是一个行之有效的手段。不过,在数字电路中,走线空间极为珍贵,走线加宽就需要更大的面积,更大的面积意味着更高的成本,老板是绝不允许的!

改变走线角度,使差分走线不与玻纤平行,这个的可操作性就比较高了。既不增加成本,也不影响layout的工作量(这一点直接影响了小明有多少时间用来撩妹),是个行之有效的好办法。那么,具体到layout操作时,如何才能走出满足要求的走线呢?

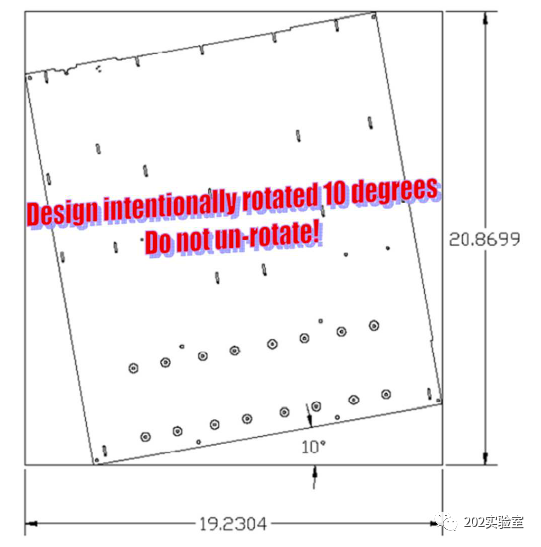

改变走线角度有三个办法,第一个办法是在加工的时候,要求板厂将Gerber对应的Film相对板材旋转一个小角度再来曝光,这样可保证所有走线都不与玻纤平行。如下图所示:

不过这样也存在操作相对困难,板材利用率下降的问题,不是最优解。

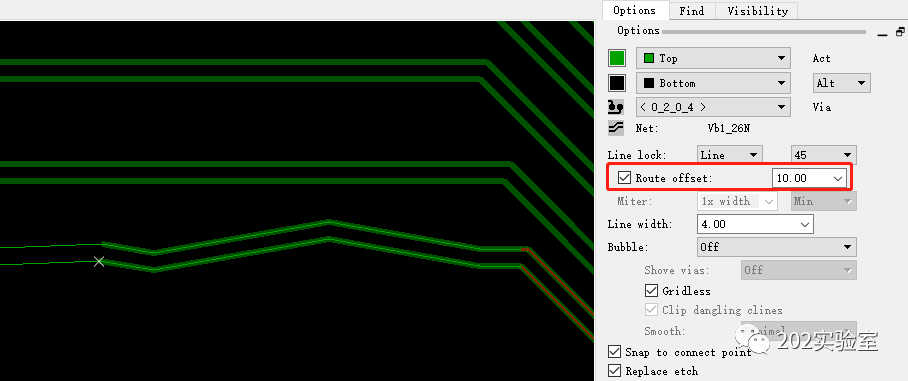

第二个办法是在layout时,针对需要控制的走线,采用偏移一定角度的方式走线。在allegro环境下,单击添加走线命令,通过如下设置即可走出具有一定角度的走线:

在options选项卡中,选中Route offset复选框,在其后输入框填入倾斜角度的数值,即可走出带有倾斜角的走线。

你是否会有这样的疑问,我需要倾斜多大的角度才算合适呢?Altera在文档中给出了一个准则:使用offset走线,下图中的W至少要大于3倍的玻纤编织节距,然后再反转布线方向。通过这个准则和下图中的公式,就可以得知最小满足要求的角度。一般我们选择10°就能够满足几乎所有的板材。

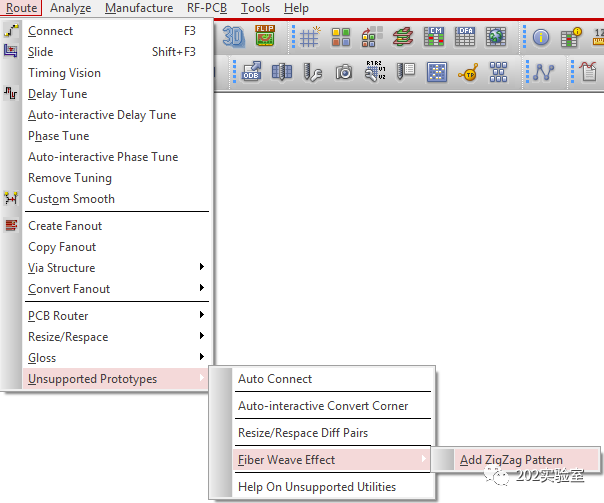

当然,手工拉出一条条这样的走线绝对不是一个好主意,怎么看都有点效率太低(又会影响小明撩妹的)。对于强大的allegro,自然是有对应的方式高效搞定此事的。在allegro中这个功能称为zigzag pattern(之字形走线),通过如下菜单栏路径打开命令:

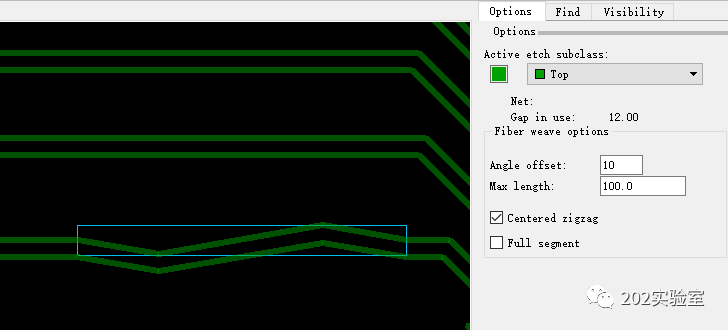

在右侧的options选项卡中有对应的参数可以设置:

在这里只需要填入偏移角度和最大长度两个参数,鼠标框选中需要调整的走线,即可拉出zigzag线段。下面两个小复选框一试便知,不多介绍。之字走线对直角走线和45°走线都可以进行调整,不过,allegro不建议对已经进行了offset走线的走线再做之字走线。

看到这里,小红紧张的表情终于放松了下来,那个奇奇怪怪的走线的意义也真相大白。原来这里面还有这么多学问,有用的知识又增加了!

参考文献:Altera: PCB Dielectric Material Selection and Fiber Weave Effect on High-Speed Channel Routing

文末福利

在“202实验室”公众号后台回复“Zig-Zag布线”可获取本文参考文献全文及“Cadence allegro Fiber Weave Off-Angle Routing”布线指南全文,建议直接复制以下字符发送:

Zig-Zag布线

zigzag走线原理及应用的更多相关文章

- PCB走线分析——直角、差分、蛇形线

PCB直角走线的影响 布线(Layout)是PCB设计工程师最基本的工作技能之一.走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过 Layout 得以实现并验证,由此可见,布 ...

- PCB走线角度选择 — PCB Layout 跳坑指南

现在但凡打开SoC原厂的PCB Layout Guide,都会提及到高速信号的走线的拐角角度问题,都会说高速信号不要以直角走线,要以45度角走线,并且会说走圆弧会比45度拐角更好.狮屎是不是这样?PC ...

- PCB直角走线的影响

PCB直角走线的影响 布线(Layout)是PCB设计工程师最基本的工作技能之一.走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过 Layout 得以实现并验证,由此可见,布 ...

- Altium Designer之AD16在Win10系统下无法切换走线/布线模式的解决办法

有些童鞋会在Win10下使用AD16的时候发现,走线模式/布线模式(切换直角,45°,弧形等)不能切换. 问题出在输入法上,一般是切换到英文输入法即可解决,但是有一种情况是win10系统自带输入法有时 ...

- altium6.x中自动删除重复走线的位置

在protel 2004 DXP中,“自动删除走线”的位置就在"PCB Editor"的默认页面,非常好找. 但是升级到了altium 6.7,6.9之后,很多人就找不到这个了. ...

- Altium Design 中差分走线的设置

1.在原理图中,将要设置的差分对的网络名称的前缀取相同的名字,在前缀后面加后缀分别为_N 和_P,并且加上差分对指示.具体操作如下:2.在原理图界面下,单击 Place>>Directiv ...

- Altium Designer 6 快速进行差分对走线

1: 在原理图中让一对网络前缀相同,后缀分别为_N 和_P,并且加上差分队对指示.在原理图中,让一对网络名称的前缀名相同,后缀分别为_N 和_P,左键点击Place DirectivesDiffere ...

- Altium 9中正确的差分对走线方法

1.在原理图中定义差分对在菜单中Place>>Directive为差分网络放置差分对指令.差分对网络名称必须以“_N”和“_P”作为后辍.对差分网络放置指令后要对其参数进行配置,包括Dif ...

- PCB走线和过孔的过流能力

PCB走线的载流能力与以下因素有关:线宽.线厚(铜箔厚度).容许温升.PCB走线越宽,载流能力越大. 近似计算公式: I=KT0.44A0.75 (K为修正系数,一般覆铜线在内层时取0.024,在外层 ...

随机推荐

- proteus8.1 pro 中文版安装破解教程

Proteus8 Pro是非常有名的EDA工具(仿真软件),从原理图布图.代码调试到单片机与外围电路协同仿真,一键切换到PCB设计,真正实现了从概念到产品的完整设计.是唯一将电路仿真软件.PCB设计软 ...

- MySQL中特别实用的几种SQL语句【转】

一.插入或替换 如果我们想插入一条新记录(INSERT),但如果记录已经存在,就先删除原记录,再插入新记录. 情景示例:这张表存的每个客户最近一次交易订单信息,要求保证单个用户数据不重复录入,且执行效 ...

- 将几张图片合并为一张图片,返回byte数组

需求:通过url数组下载图片,再竖直合成一张新的图片,具体java代码如下 1 /** 2 * 竖直合并图片 3 * 4 * @param urls 5 * @return 6 */ 7 public ...

- Java中泛型的详细解析,深入分析泛型的使用方式

泛型的基本概念 泛型: 参数化类型 参数: 定义方法时有形参 调用方法时传递实参 参数化类型: 将类型由原来的具体的类型参数化,类似方法中的变量参数 类型定义成参数形式, 可以称为类型形参 在使用或者 ...

- javaScript学习关于常用注册监听和对象的创建

JS 中的自定义对象(扩展内容) Object 形式的自定义对象 对象的定义: ...

- Rancher v1.6.29 Docker单节点部署

前言: Docker镜像中心,有两个版本的rancher(1.X),镜像名称为:rancher/server,而rancher(2.X)的镜像名称是rancher/rancher 去daocloud官 ...

- CodeReview of JDK Source Code

jdk1.6.0_35/src.zip, only java package is reviewd(full package review caused a OutofMemory on java h ...

- Java EE-下载安装eclipse并设置环境变量的步骤

1.下载eclipse: 官网:https://www.eclipse.org/downloads/ (1)点击链接后显示如图 (2)点击Download Packages 下载安装包,不要点击&qu ...

- 那些shellcode免杀总结

首发先知: https://xz.aliyun.com/t/7170 自己还是想把一些shellcode免杀的技巧通过白话文.傻瓜式的文章把技巧讲清楚.希望更多和我一样web狗也能动手做到免杀的实现. ...

- 安全工具推荐之Goby篇

Goby(鰕虎鱼) 这个东西出来也很久了,有一年多了吧,个人感觉用起来还不错(当然见仁见智哈,别喷我),今天拿来水一篇 官网有很详细的使用说明,所以本文纯属发表一下感慨,非技术贴 官网在此:https ...