SV-assertion

断言(assert)是一种描述性语言,通过描述的期望结果来进行仿真验证。

断言有一个更加基础的信息,我们称为属性(property),属性可以作为断言结果,功能覆盖点,形式检查和约束随机激励生成。

断言相比较与testcase的仿真验证,对设计的可见度要求比较高,可以帮助快速定位错误的根源,断言可以分布在设计各个部位。

在项目中使用断言,有两种方式(eda tool中都支持):

1) 使用预建的断言库,如OVL,

2) 使用SVA,PSL等断言语言来自己描述。(PSL是完全独立的断言语言,SVA被继承在SV语言中),

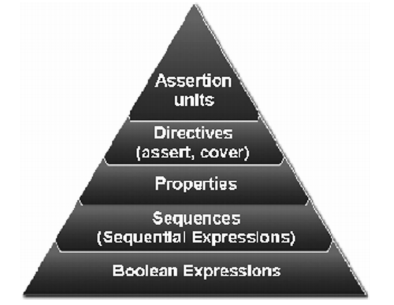

SVA的语言层次结构:

assertion分为:

1) immediate assert,基于simulation event semantics;

assert/assume/cover (expression) action_block;

2) concurrent assert,基于clock semantics;

assert/assume/cover (expression) action_block;

action_block的声明:

statement | [statement] else statement;

immediate assert的action block紧跟着assert执行,就像在procedual block中,(比如active或者NBA region)

可以放在任何procedual中,initial,always,task,function。

concurrent assert的action block,在当前assert的reactive region执行,所以action block中使用$sampled()采样信号值,表示evaluate时的信号值。

assertion中的property,可以用来描述design的某一个行为,必须被例化在assert,assume,cover等编译选项后,

包含在module,interface,package,program,clocking,$unit中。

sequence,用来描述high level property的abort condition或者common start point,一系列的boolean expression。

在sva中,一个property代表一个thread,表示一系列event的sequence,可能持续多个cycle。

在property没有start的时候,thread不会起来,之后的check是不会被evaluation的。被认为是true的。

当该property执行结束或者结果已经出错,property在这个时间点结束。

SV引入了 |->表示overlapping的操作,resulting sequence (consequent) 与causing sequence (antecedent) 在同一个cycle完成。

|=>表示non-overlapping的操作,resulting sequence在causing sequence的下一个cycle开始。

sequence:随着时间增加的SV boolean expression。

可以声明有formal args,local var;

method方法有:ended,matched,triggered,这三个方法都表示sequence的结束;

尽量使用named sequence,来增加代码的可读性。

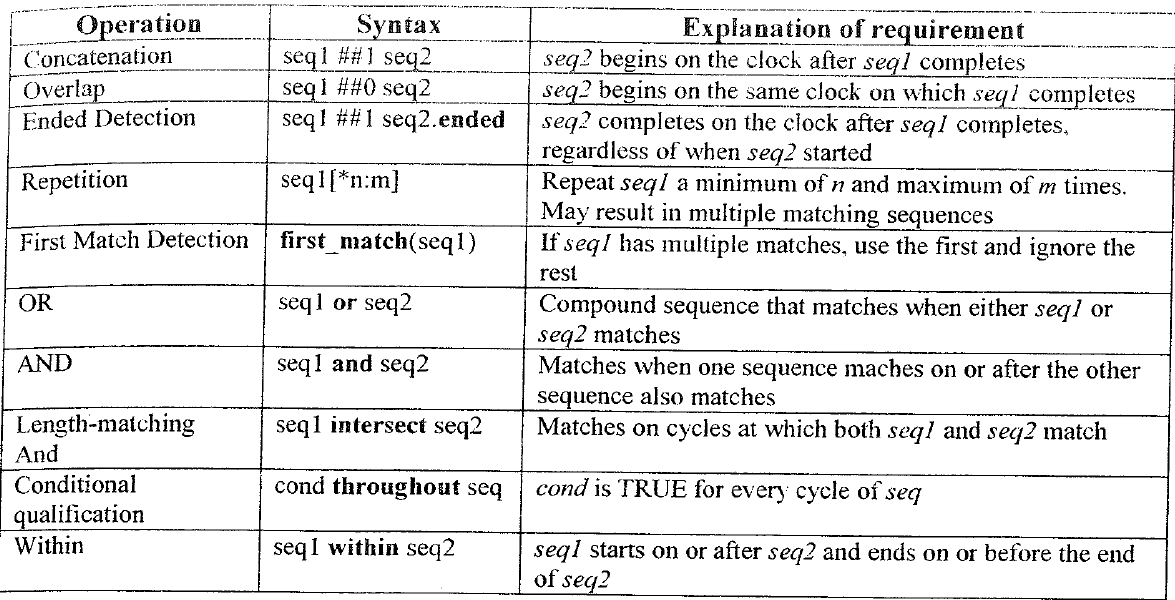

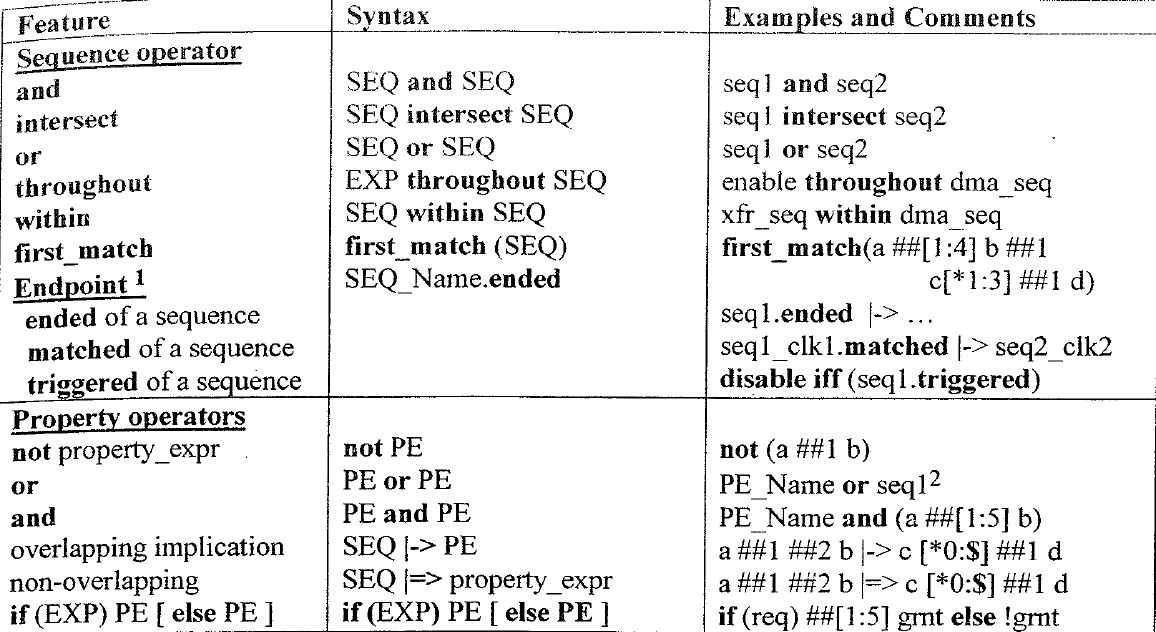

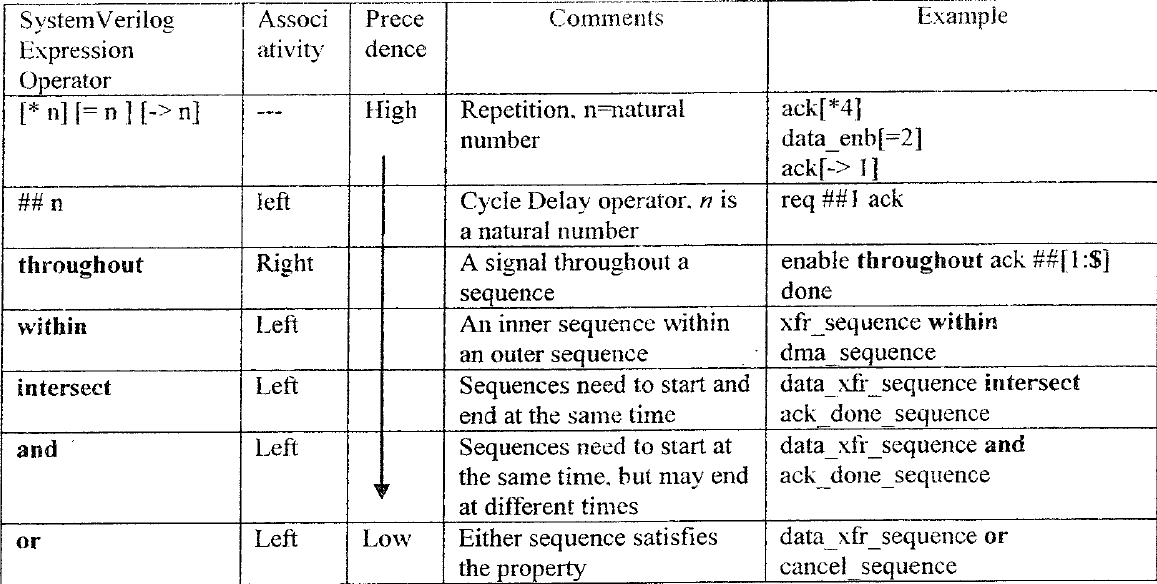

sequence支持的操作符:

注意:1) sequence中的formal args是untyped的;formal args可以是一个signal,sequence,sequence method。

2) sequence中的local var是不能用作setup delay或者repetition ranges的,

property:可以包含formal args,可以有local var;

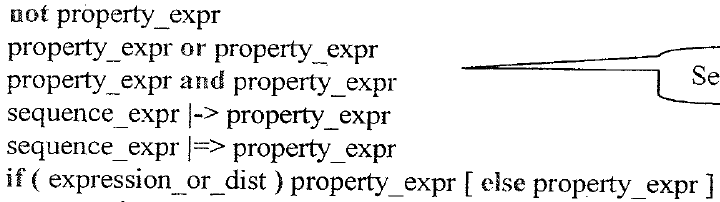

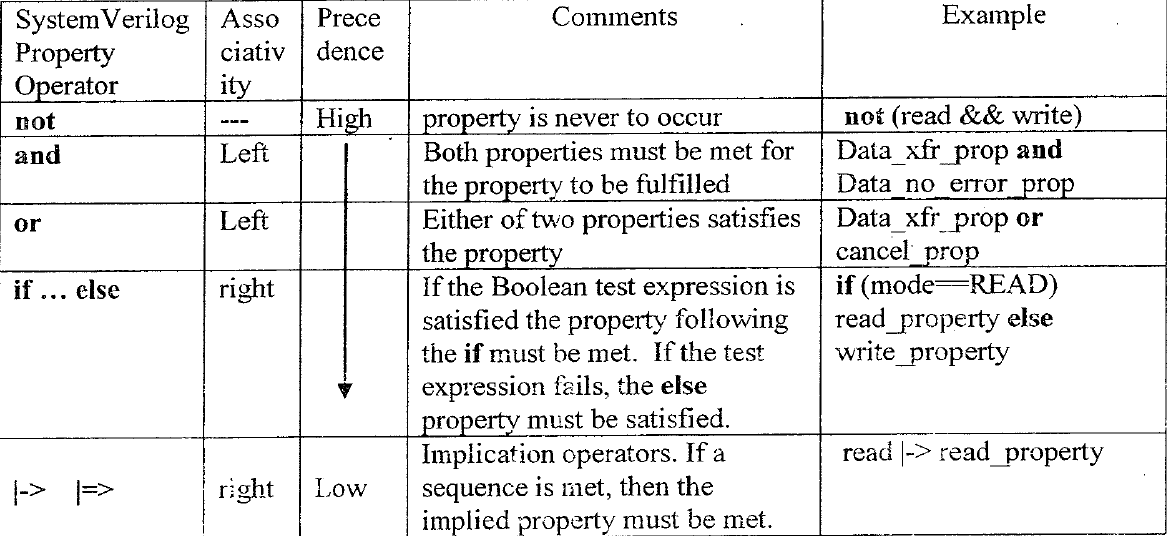

property支持的操作符:

注意:1) 一个property_spec不是一个sequence,但是一个sequence可以是一个property_spec。

2) formal args可以带default value。

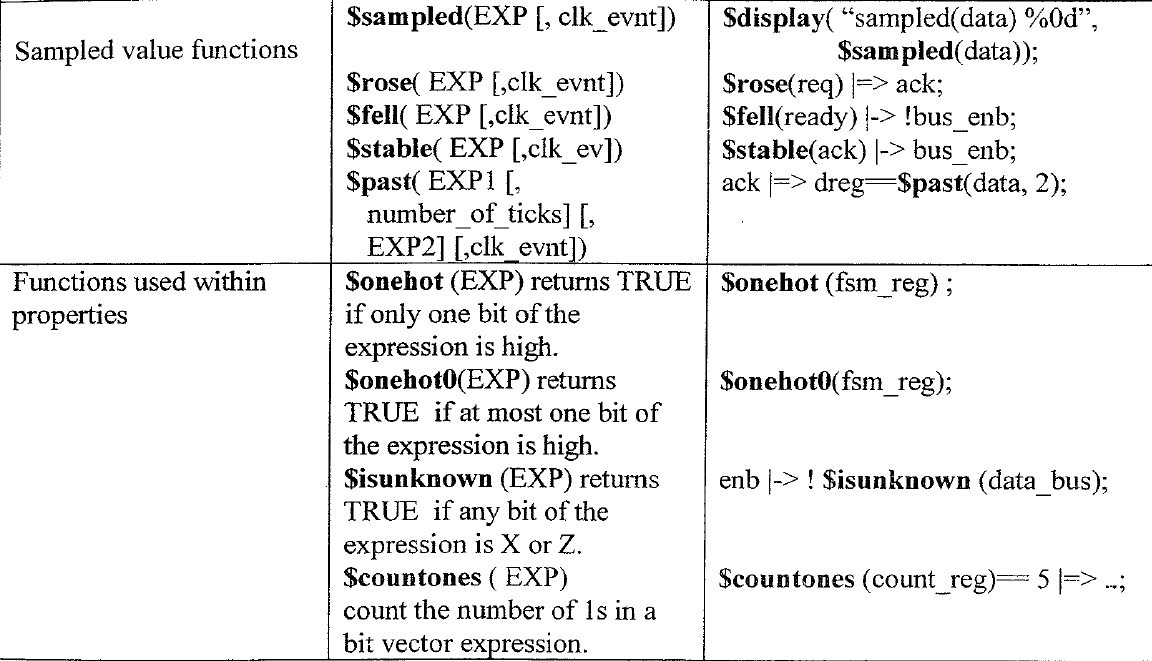

SVA中支持的assertion 语句以及function:

SVA中各个运算符之间的操作,可以是expression,sequence,property。

expression的优先级与logic operate部分相同。

sequence之间的优先级:

property之间的优先级:

verilog中的#表示延时,delay,##号表示延时若干个clock cycles。

如果implication operator中,antecedent fail,property被hold为vacuous success。

property中的not operator不可以和implication operator一同使用,一般只用在sequence组成的property,表示从不true的序列。

sequence中的first_match操作符,用来消除可能发生overlap的assert result:

1.如果property中只由一个sequence组成,则包含一个implicit first_match。

property p_seq; (a##1 b ##[0:5] c); endproperty

2.consequent sequence中默认包含一个implicit first_match。

property p_seq; a=>b##[1:2] c ## [0:4] d; endproperty

property p_seq; a=>## [0:3] qABC.ended; endproperty

first_match主要用在antecedent的sequence中,一个sequence的ended是可以多触发的。

property p_seq; first_match(a##[2:3]b) |-> c; endproperty

property p_seq; first_match(qABC.ended) |-> c; endproperty

重复操作符,可以用于sequence和expression中。

consecutive repetitive, seq[*n], exp[*n]

non-consecutive repetive, seq[=n], exp[=n]

goto repetitive,non-consecutive exact repetitive, seq[->n],exp[->n]

throughtout, condition over sequence。用来保证boolean condition在sequence有效期间是正确的。

property p_seq; @(posedge clk) $rose(req) |-> ##[1:4] enable throughout (ack ##[1:$] done); endproperty

其中enable throughout (ack ##[1:$] done)表示一个sequence;

##[1:4] seq表示一个sequence;

intersect, length-match sequence 表示两个sequence从同一个clock tick 开始并且在同一个clock tick结束。

within, 表示一个sequence在另一个sequence有效中完成。

and, not-length-matching sequence,两个sequence同时开始,但是不需要同时结束。

sequence method:

ended,主要用在sequence在single clock assertion中的endpoint;

ended method方法,在observe region之外是没有意义的,所以只能用在assert evaluation。

property p_seq; @(psoedge clk) dmaWriteBlock(dma_done).ended |-> ##[1:5] cpu_interrupt; endproperty

matched,主要用在sequence在multi_clocks assertion中的endpoint;

将ended的结果进行latch and multi-clock sync,只在第一个clock的observe region有效。

sequence q_1(a, b); @(posedge clk) $rose(a) ##[2:3] b; endsequence

sequence q_2; @(posedge sysclk) c##1 q_1(a,b).matched[->1]##1 d; endsequence

triggered,Level-sensitive control,主要用在disable iff,或者wait sequence.triggered中。

值采样函数,$stable(exp),表示该exp的值与上一个clock tick的值相同。

property p_seq; $fell(req_n) |=> ack ##1 $stable(ack)[*0:100] ##1data_valid; endproperty。

assertion-ctrl system task;

$asserton, $assertoff, $assertkill。

assert cover中,可以收集assert更多的结果,主要分为coverage for properties,coverage for sequences。

1.coverage for properties, Number of times attempted, succeeded, failed, vacuous success.

2.coverage for sequence, Number of times attempted, matched.

assert中的clock定义:

1. sequence中定义,

顶层的clock定义不影响该sequence中的clock定义;

assert property中仍需要定义clock,该sequence中定义的clock不会变为property clock。

2. concurrent property中定义,

3. procedual block中inferred clock,

4. 本身property定义在clocking block中,

clocking block中的input output delay并不影响assert的执行,input,output delay只是对circuit delay的建模。

5. 定义default clocking,

6,声明assert的时候显式指定, assert property (@posedge clk) p_seq);

如果此时property中也定义了clock,两个clock必须相同。

SV-assertion的更多相关文章

- verilog断言(SVA:systemverlog assertion)语法 ---- 转载

转载自:http://blog.sina.com.cn/s/blog_4c270c730101f6mw.html 作者:白栎旸 断言assertion被放在verilog设计中,方便在仿真时查 ...

- systemverilog assertion

1.一般是单独写一个module 里面放assertion, 然后在验证平台顶层和RTL的实例化bind起来 2. |->表示直接进行判断,|=>表示下一拍判断,一般一个断言最好只写一 ...

- SV processses

SV中的structured procedure: 1)intial procedure,keyword只有initial:最开始被调用一次: 2)always procedure,keyword包括 ...

- SV中的覆盖率

SV采用CRT的激励形式,而判断验证进度的标准也就是覆盖率(coverage). 覆盖率的两种指定形式:显式的,直接通过SV来指定出的,如SVA,covergroup. 隐式的,在验证过程中,随&qu ...

- SV中的Interface和Program

Interface:SV中新定义的接口方式,用来简化接口连接,使用时注意在module或program之外定义interface,然后通过'include来添加进工程. interface arb_ ...

- SystemVerilog Assertion 设计、调试、测试总结(2)

上一篇博客主要写了SVA的基本语法(详细),这一篇主要写SVA语法总结,以及如何查看SVA波形等. 断言assertion被放在verilog设计中,方便在仿真时查看异常情况.当异常出现时,断言会报警 ...

- SystemVerilog Assertion 设计、调试、测试总结(1)

暑期实习两个月的其中一个任务是:如何在设计中加入断言?以及断言的基本语法.三种应用场景下的断言(如FIFO.FSM.AXI4-lite总线).参考书籍:<System Verilog Asser ...

- 挣值管理(PV、EV、AC、SV、CV、SPI、CPI) 记忆

挣值管理法中的PV.EV.AC.SV.CV.SPI.CPI这些英文简写相信把大家都搞得晕头转向的.在挣值管理法中,需要记忆理解的有三个参数:PV.AC.EV. PV:计划值,在即定时间点前计划 ...

- Assertion failure in -[UITableView _configureCellForDisplay:forIndexPath:]

今天遇到了Assertion failure in -[UITableView _configureCellForDisplay:forIndexPath:]这个错误,一直也没有百度,不料想却弄了一个 ...

- Assertion failure in -[UITableView _classicHeightForRowAtIndexPath:], /SourceCache/UIKit_Sim/UIKit-3318/UITableView.m:10772

Assertion failure in -[UITableView _classicHeightForRowAtIndexPath:], /SourceCache/UIKit_Sim/UIKit-3 ...

随机推荐

- Unix历史及相关概念回顾

欢迎来到Unix的世界 很多人都用了很多年的Unix(其实更熟悉的是叫Linux),也接触到Unix世界中的各种概念,比如GCC.GNU.BSD.POSIX.GPL等等,也大都知道一些传奇的如雷贯耳的 ...

- Petrozavodsk Summer-2016. Ural FU Dandelion Contest

A. Square Function 留坑. B. Guess by Remainder 询问$lcm(1,2,3,...,n)-1$即可一步猜出数. 计算$lcm$采用分治FFT即可,时间复杂度$O ...

- requirejs的使用和快速理解

样例来自https://www.jianshu.com/p/b8a6824c8e07 requirejs有以下功能 声明不同js文件之间的依赖 可以按需.并行.延时载入js库 可以让我们的代码以模块化 ...

- Java课程2019年3月开学测试

一.登录界面 模板的验证方式已经写在了function里面,我们只需要在提交的过程中进行验证. 我们这里需要注意到的是在login文件夹中,有一个randcode的验证码生成文件,打开代码我们可以看到 ...

- HDFS的WEB页面访问常见问题

HDFS的WEB UI管理页面 50070 端口 无法访问解决办法! 本文基于HADOOP-3..1.0,Cecntos7.0环境下进行测试,所以遇到很多新鲜的问题: 特别注意:HaDoop3.0之前 ...

- Linux下卸载Oracle 11g

第一种方法: 使用oracle自带的runInstaller 卸载 [oracle@VM_0_14_centos deinstall]$ cd $ORACLE_HOME [oracle@VM_0_14 ...

- | dp-the Treasure Hunter

题目: A. Mr. Kitayuta, the Treasure Hunter time limit per test 1 second memory limit per test 256 mega ...

- linux安装jdk配置环境变量

tar -zxvf xxxx.tar.gz export JAVA_HOME=/usr/local/jdk/jdk1.8.0_201export PATH=$JAVA_HOME/bin:$PATHex ...

- robotframework RF使用中需要安装的工具和库

确保 Python 3.6.2 安装成功 安装 如下 RF使用中需要的工具和库 1. RF 在两个Python中安装 robotframework执行命令 pip install robotframe ...

- 安卓点击home键重启

主要原因是:每次启动Intent导致新创建Task的时候,该Task会记录导致其创建的Intent:而如果后续需要有一个新的与创建Intent完全一致(完全一致定位为:启动类,action.categ ...