[转]FPGA实践——基于ROM访问的直接波形合成

本文原创,转载请注明出处:http://www.cnblogs.com/risten/p/4166169.html

1.系统原理

通过频率控制字选择相位步进,产生访问ROM的地址,进而控制DAC的输出波形与频率。整个系统由时钟生成、相位累加、ROM、DAC组成。限于basys2开发板的限制,本次将输出DAC替换为8个led灯显示。

2.系统设计

2.1 时钟生成

1 library IEEE;

2 use IEEE.STD_LOGIC_1164.ALL;

3 use IEEE.STD_LOGIC_ARITH.ALL;

4 use IEEE.STD_LOGIC_UNSIGNED.ALL;

5

6 entity clock_gen is

7 port (

8 clk : IN STD_LOGIC;

9 rst : IN STD_LOGIC;

10 clka : OUT STD_LOGIC

11 );

12 end clock_gen;

13

14 architecture Behavioral of clock_gen is

15 signal cnt : INTEGER;

16 signal clk_reg : STD_LOGIC;

17

18 begin

19 clka<=clk_reg;

20 process(clk,rst)

21 begin

22 if (rst='0') then

23 cnt<=0;

24 clk_reg<='0';

25 elsif (clk'event and clk='1') then

26 if (cnt=250000) then --生成时钟为0.01s

27 cnt<=0;

28 clk_reg<=not clk_reg;

29 else

30 cnt<=cnt+1;

31 end if;

32 end if;

33 end process;

34 end Behavioral;

2.2相位累加(地址生成)

1 library IEEE;

2 use IEEE.STD_LOGIC_1164.ALL;

3 use IEEE.STD_LOGIC_ARITH.ALL;

4 use IEEE.STD_LOGIC_UNSIGNED.ALL;

5

6 entity phase_adder is

7 port(

8 clka : IN STD_LOGIC;

9 rst : IN STD_LOGIC;

10 f_level : IN STD_LOGIC_VECTOR(6 DOWNTO 0);

11 addr : OUT STD_LOGIC_VECTOR(9 DOWNTO 0)

12 );

13 end phase_adder;

14

15 architecture Behavioral of phase_adder is

16 signal cnt : STD_LOGIC_VECTOR(9 DOWNTO 0);

17

18 begin

19 addr<=cnt;

20 process(clka,rst,f_level)

21 begin

22 if (rst='0') then

23 cnt<=(others=>'0');

24 elsif (clka'event and clka='1') then

25 cnt<=cnt+f_level;

26 end if;

27 end process;

28

29 end Behavioral;

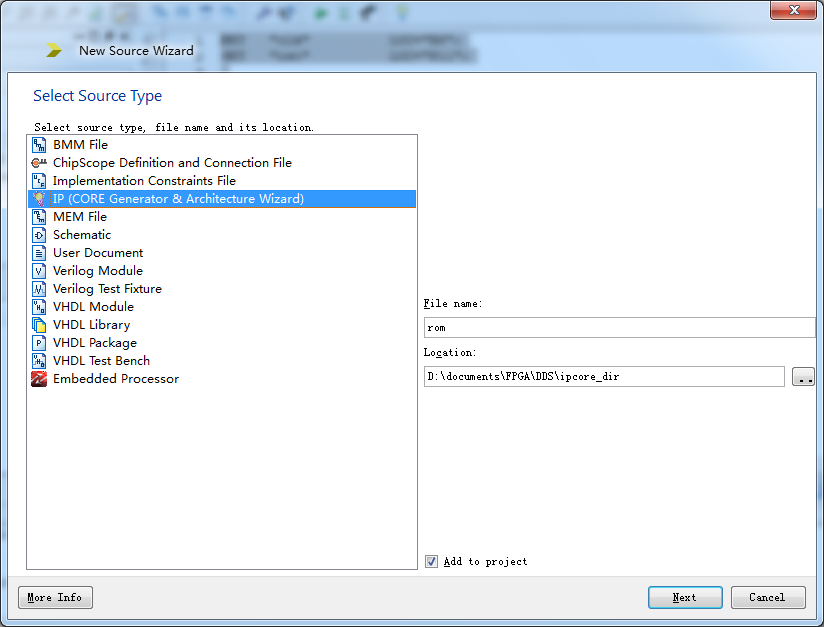

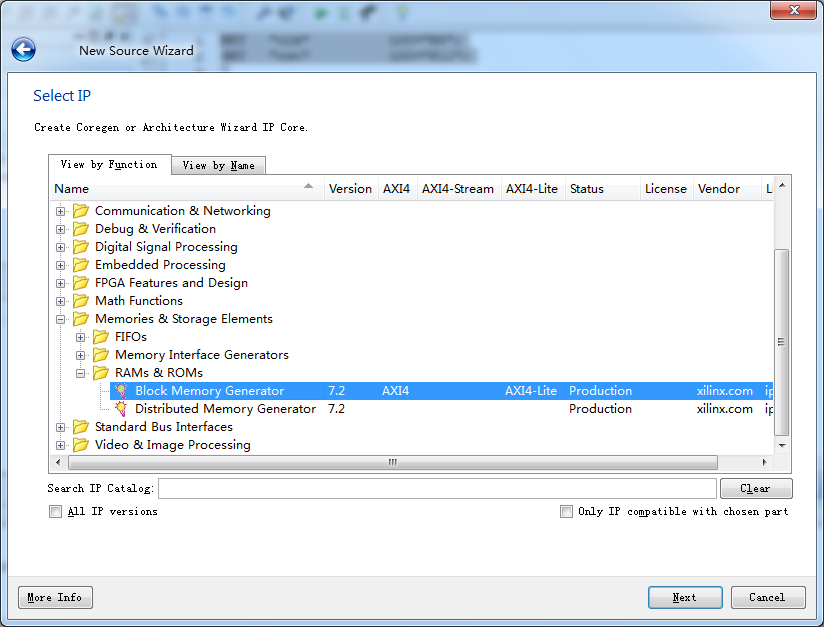

2.3 ROM

新建源文件选择IP核

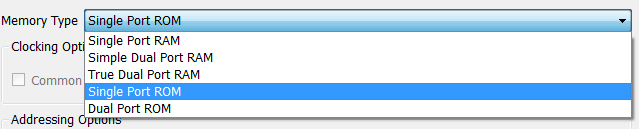

存储类型

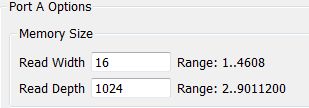

存储大小

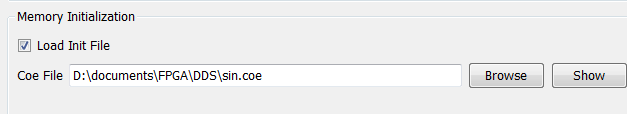

数据初始化

正弦余弦初始化coe文件的生成(使用matlab)

1 clc

2 clear all

3 close all

4 x = linspace(0, 2*pi ,1024); % 在区间[0,2*pi]之间等间隔地取1024个点

5 y_cos = cos(x);

6 y_sin = sin(x);

7 y_cos = y_cos * 2^15;

8 y_sin = y_sin * 2^15;

9 fid = fopen('D:/cos.coe','wt');

10 fprintf(fid, '%5.0f,\n' , y_cos);

11 fclose(fid);

12 fid = fopen('D:/sin.coe','wt');

13 fprintf(fid, '%5.0f,\n' , y_sin);

14 fclose(fid);

用记事本在生成文件开头添加

并把最后的结尾换为 ; 号

存储器选项都设置完毕后点击generate即可。

2.4 LED显示(DAC)

1 library IEEE;

2 use IEEE.STD_LOGIC_1164.ALL;

3 use IEEE.STD_LOGIC_ARITH.ALL;

4 use IEEE.STD_LOGIC_UNSIGNED.ALL;

5 use IEEE.STD_LOGIC_SIGNED.ALL;

6

7 entity led is

8 port (

9 data : IN STD_LOGIC_VECTOR(15 DOWNTO 0);

10 led_seg : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

11 );

12 end led;

13

14 architecture Behavioral of led is

15 begin

16 process(data)

17 begin

18 if (signed(data)<-24576) then

19 led_seg<="10000000";

20 elsif (signed(data)<-16348) then

21 led_seg<="01000000";

22 elsif (signed(data)<-8192) then

23 led_seg<="00100000";

24 elsif (signed(data)<0) then

25 led_seg<="00010000";

26 elsif (signed(data)<8192) then

27 led_seg<="00001000";

28 elsif (signed(data)<16348) then

29 led_seg<="00000100";

30 elsif (signed(data)<24576) then

31 led_seg<="00000010";

32 else

33 led_seg<="00000001";

34 end if;

35 end process;

36

37 end Behavioral;

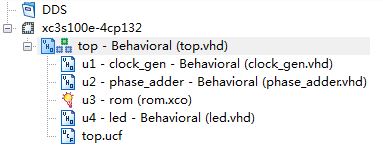

2.5 顶层设计TOP

1 library IEEE;

2 use IEEE.STD_LOGIC_1164.ALL;

3

4 entity top is

5 port (

6 clk : IN STD_LOGIC;

7 rst : IN STD_LOGIC;

8 f_level : IN STD_LOGIC_VECTOR(6 DOWNTO 0);

9 led_seg : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

10 );

11 end top;

12

13 architecture Behavioral of top is

14 COMPONENT clock_gen

15 PORT (

16 clk : IN STD_LOGIC;

17 rst : IN STD_LOGIC;

18 clka : OUT STD_LOGIC

19 );

20 END COMPONENT;

21 COMPONENT phase_adder

22 PORT (

23 clka : IN STD_LOGIC;

24 rst : IN STD_LOGIC;

25 f_level : IN STD_LOGIC_VECTOR(6 DOWNTO 0);

26 addr : OUT STD_LOGIC_VECTOR(9 DOWNTO 0)

27 );

28 END COMPONENT;

29 COMPONENT rom

30 PORT (

31 clka : IN STD_LOGIC;

32 addra : IN STD_LOGIC_VECTOR(9 DOWNTO 0);

33 douta : OUT STD_LOGIC_VECTOR(15 DOWNTO 0)

34 );

35 END COMPONENT;

36 COMPONENT led

37 PORT (

38 data : IN STD_LOGIC_VECTOR(15 DOWNTO 0);

39 led_seg : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

40 );

41 END COMPONENT;

42

43 signal clka : STD_LOGIC;

44 signal addr : STD_LOGIC_VECTOR(9 DOWNTO 0);

45 signal data : STD_LOGIC_VECTOR(15 DOWNTO 0);

46

47 begin

48 u1 : clock_gen PORT MAP (clk,rst,clka);

49 u2 : phase_adder PORT MAP (clka,rst,f_level,addr);

50 u3 : rom PORT MAP (clka,addr,data);

51 u4 : led PORT MAP (data,led_seg);

52

53 end Behavioral;

3. 引脚定义

1 NET "clk" LOC="B8";

2 NET "rst" LOC="P11";

3

4 NET "f_level<0>" LOC="L3";

5 NET "f_level<1>" LOC="K3";

6 NET "f_level<2>" LOC="B4";

7 NET "f_level<3>" LOC="G3";

8 NET "f_level<4>" LOC="F3";

9 NET "f_level<5>" LOC="E2";

10 NET "f_level<6>" LOC="N3";

11

12 NET "led_seg<0>" LOC="M5";

13 NET "led_seg<1>" LOC="M11";

14 NET "led_seg<2>" LOC="P7";

15 NET "led_seg<3>" LOC="P6";

16 NET "led_seg<4>" LOC="N5";

17 NET "led_seg<5>" LOC="N4";

18 NET "led_seg<6>" LOC="P4";

19 NET "led_seg<7>" LOC="G1";

[转]FPGA实践——基于ROM访问的直接波形合成的更多相关文章

- memcached基于socket访问memcache缓存服务器

memcached基于socket访问memcache缓存服务器 操作memcache常用三种方法: .memcache基于php_memcache.dll扩展(php扩展) .memcached基于 ...

- 源码编译安装LAMP环境及配置基于域名访问的多虚拟主机

实验环境及软件版本: CentOS版本: 6.6(2.6.32.-504.el6.x86_64) apache版本: apache2.2.27 mysql版本: Mysql-5.6.23 php版本 ...

- FPGA例化ROM存储表格

FPGA例化ROM存储表格 1.选择ROM 2.填写数据位宽和深度 3.加载ROM初始化信息,coe文件

- 在虚拟机上的关于Apache(阿帕奇)(5)基于端口访问网站

这篇随笔是基于端口访问网站,和前面两篇文章基于ip和基于域名一起练习效果更好 接下来分别创建三个网站数据目录 输入命令: mkdir -p /home/wwwroot/{8001,8002,800 ...

- 在虚拟机上的关于Apache(阿帕奇)(4)基于域名访问网站

这篇随笔是基于域名访问网站,和前后两篇文章基于ip和基于端口一起练习效果更好 首先配置网卡Ip地址与hosts文件 输入命令: vi /etc/hosts/ (每行只能写一条,格式为IP地址+空格 ...

- 在虚拟机上的关于Apache(阿帕奇)(3)基于IP访问网站

这篇随笔是基于IP访问网站,和后面两篇文章基于域名和基于端口一起练习效果更好 基于IP(记得下载httpd服务) 首先使用nmtui命令为网卡添加多个ip地址 输入命令:nmtui 进入下面这个界 ...

- 基于Socket访问西门子PLC系列教程(二)

本文是西门子开放式TCP通信的第2篇,上一篇我们讲了使用西门子1200PLC作为TCP服务器的程序编写,可以点击下方链接阅读:[公众号dotNet工控上位机:thinger_swj] 基于Socket ...

- 【阿里云产品公测】OTS使用之简单线上产品实践基于PythonSDK

阿里云用户:morenocjm 实践是检验真理的唯一标准,学习技术需要通过实践过程中的不断尝试,才能够快速掌握要领.OTS是构建在阿里云飞天分布式系统之上的NoSQL数据库服务,提供海量结构化数据的存 ...

- Laravel + go-micro + grpc 实践基于 Zipkin 的分布式链路追踪系统 摘自https://mp.weixin.qq.com/s/JkLMNabnYbod-b4syMB3Hw?

分布式调用链跟踪系统,属于监控系统的一类.系统架构逐步演进时,后期形态往往是一个平台由很多不同的服务.组件构成,用户请求过来后,可能会经过其中多个服务,如图 不过,出问题时往往很难排查,如整个请求变慢 ...

随机推荐

- awk理论详解、实战

答疑解惑: 为什么用awk取IP的时候用$4? ifconfig eth0 | awk -F '[ :]+' 'NR==2{print $4}' IP第二行内容如下: inet addr:10.0.0 ...

- git移除上一次的commit中误添加的文件

在使用git进行版本管理时,往往会出现一些误操作,比如将一些不加上传的文件放到了暂存区,即上传到了上一次commit中 比如: commit c134ab90ca7c4daf8bfa22e3ad706 ...

- C# SQL帮助类

C# SQL帮助类 本人自己封装的SQLHelper类,执行sql server与Oracle数据的增删改查 vs自带的Oracle数据库引用需要安装Oracle客户端,如不想安装Oracle客户端, ...

- iOS开发之分段控制器(UISegmentedControl)

今天我们来说下iOS中的分段选择控制器UISegmentedControl,这一控件有什么作用呢 每个segment都能被点击,相当于集成了多个button 通常我们会点击不同的segment来切换不 ...

- Lazarus安装使用

Lazarus安装使用 最后还是安装了Lazarus: 安装之后,新建了项目,还引入了Unit,就可以跑了: 学习:http://tieba.baidu.com/p/3164001113 progra ...

- 转: svn服务器路径名修改(不需要全部重新拉取文件)

svn路径名修改之后, 一大波的研发代码都可能面临变更.还有有一个svn relote神器 大家可以借助各自的SVN工具中哦relote命令完成路径的切换,而不需要全部重新download所有的新路径 ...

- erlang 小程序:整数序列,搜索和为正的最长子序列

近期学习了一下erlang, 编了个小程序 算法例如以下: 把參数分为三个 当前位置的前子序列(Save)(比方 -5, 1,2,-1, _, ... ) 当前位置为_时, 前子序列就是 1,2,-1 ...

- vue2.0 自定义 下拉刷新和上拉加载更多(Scroller) 组件

1.下拉刷新和上拉加载更多组件 Scroller.vue <!-- 下拉刷新 上拉加载更多 组件 --> <template> <div :style="mar ...

- js逻辑非同时两次使用 !!null

今天遇到了“!!null”的写法,百度没有找到直接的解释,翻书在<javascript高级设计>P44找到了相应的解释: 同时使用两个逻辑非操作符,实际上就会模拟Boolean()转型函数 ...

- 初步探讨WPF的ListView控件(涉及模板、查找子控件) - GavinJun

本文结合模板的应用初步介绍ListView的应用 一.Xaml中如何建立数据资源 大部分数据都会来自于后台代码,如何Xaml同样的建立数据源呢?比如建立一个学生List: 首先引入命名空间: xmln ...