FPGA热设计

任何芯片要工作,必须满足一个温度范围,这个温度是指硅片上的温度,通常称之为结温(junction temperature)。

ALTERA的FPGA分为商用级(commercial)和工业级(induatrial)两种,商用级的芯片可以正常工作的结温范围为0~85摄氏度,而工业级芯片的范围是-40~100摄氏度。在实际电路中,我们必须保证芯片的结温在其可以承受的范围之内。

随着芯片的功耗越来越大,在工作的时候就会产生越来越多的热量。如果要维持芯片的结温在正常的范围以内,就需要采取一定的方法使得芯片产生的热量迅速发散到环境中去。

学过中学物理的人都知道,热量传递主要采用三种方法,即传导、对流和辐射,芯片向外散热同样是采用这几种方式。

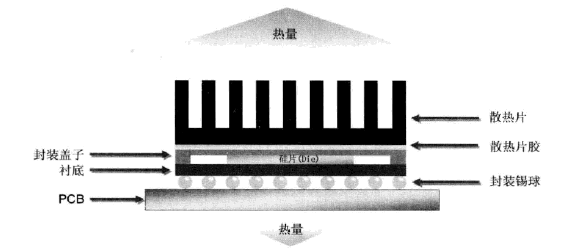

下图所示为一个芯片散热的简化模型。图中芯片产生的热量主要传给芯片外封装,如果没有贴散热片,就由芯片封装外壳直接散布到环境中去;如果加了散热片,热量就会由芯片的外封装通过散热片胶传到散热片上,再由散热片传到环境中。一般来说,散热片的表面积都做的相当大,与空气的接触面就大,这样有利于传热。在平时的实践中已经发现,绝大多数散热片都是黑色的,由于黑色物体容易向外辐射热量,这样也有利于热量向外散发。而且散热片表面的风速越快,散热越好。

简化的芯片热流模型

除此之外,有一小部分热量经过芯片衬底传导到芯片的焊锡球上,再经由PCB把热量散步到环境中。由于这部分热量所占的比例比较小,所以在下面讨论芯片封装和散热片的热阻时就忽略了这一部分。

首先需要理解“热阻(thermal resistance)”的概念,热阻是描述物体导热的能力,热阻越小,导热性越好,反之越差,这一点有点类似电阻的概念。

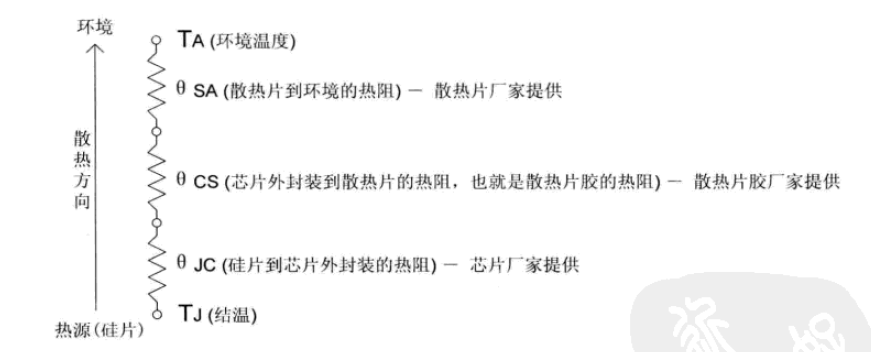

从芯片的硅片到环境的热阻,假设所有的热量都最终由散热片散布到环境中,这样可以得到一个简单的热阻模型,如下图:

带散热片的芯片散热模型

从硅片到环境的总热阻称为JA,因此满足:

JA=JC+CS+SA

JC是指芯片到外封装的热阻,一般由芯片供应商提供;CS是指芯片外封装到散热片的热阻,如果散热片采用导热胶附着在芯片表面,这个热阻就是指导热胶的热阻,一般由导热胶供应商提供;SA是指散热片到环境的热阻,一般由散热片厂家给出这个热阻值,这个热阻值是随着风速的提高而降低的,厂家通常会给出不同风速情况下的热阻值。

芯片的封装本身就是作为一个散热装置。如果芯片没有加散热片,JA就是硅片经过外封装,再到环境中的热阻值,这个值显然要大于有散热片是的JA值。这个值取决于芯片本身封装的特性,一般由芯片厂家提供。

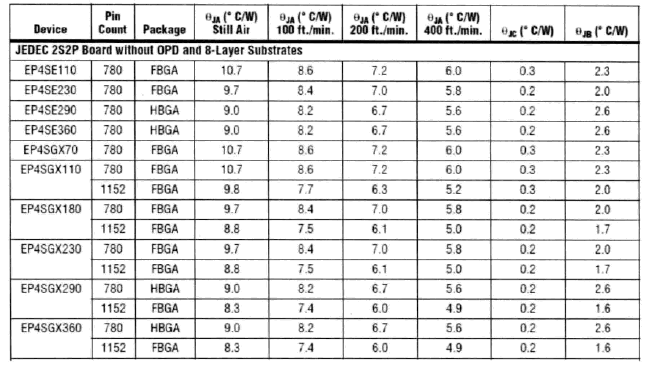

下图显示为ALTERA的STRATIX IV器件的封装热阻。其中给出了各种风速下的芯片的JA值,这些值可以用来计算无散热器时的情况。另外,其中的JC是用来计算带散热片时的总JA值。

Stratix iv器件封装的热阻

假设硅片消耗的功率是P,则:

TJ(结温)=TA+P*JA

需要满足TJ不能超过芯片允许的最大的结温,再根据环境温度和芯片实际消耗的功率,可以计算出对JA最大允许的要求。

JAMax=(TJMax - TA)/P TA(环境温度)

如果芯片封装本身的JA大于这个值,那么必须考虑给芯片加合适的散热装置,以降低芯片到环境的有效JA值,防止芯片过热。

在实际的系统中,部分热量也会从PCB散出,如果PCB层数多,面积较大,也是非常有利于散热的。

版权所有权归卿萃科技 杭州FPGA事业部,转载请注明出处

作者:杭州卿萃科技ALIFPGA

原文地址:杭州卿萃科技FPGA极客空间 微信公众号

扫描二维码关注杭州卿萃科技FPGA极客空间

FPGA热设计的更多相关文章

- 优化基于FPGA的深度卷积神经网络的加速器设计

英文论文链接:http://cadlab.cs.ucla.edu/~cong/slides/fpga2015_chen.pdf 翻译:卜居 转载请注明出处:http://blog.csdn.net/k ...

- FPGA与simulink联合实时环路系列——实验三 按键key

实验三 按键key 实验内容 在FPGA的实验中,经常涉及到按键的使用,按键是必不可少的人机交互的器件之一,在这些实验中,有时将按键的键值读取显示到数码管.LCD或者是通过串口传送到PC的串口助手上进 ...

- FPGA与simulink联合实时环路系列——实验二LED

实验二LED 实验内容 在实验一的基础上,将simulink产生的测试信号输出到FPGA开发板上的LED灯进行显示,这里要在生成的硬件模型上进行修改,将传送到FPGA的信号输出到8个LED灯上,并且对 ...

- FPGA优化之高扇出

Fanout即扇出,模块直接调用的下级模块的个数,如果这个数值过大的话,在FPGA直接表现为net delay较大,不利于时序收敛.因此,在写代码时应尽量避免高扇出的情况.但是,在某些特殊情况下,受到 ...

- 关于 FPGA 内部信号扇入扇出

扇入.扇出系数 扇入系数是指门电路允许的输入端数目.一般门电路的扇入系数为1—5,最多不超过8.扇出系数是指一个门的输出端所驱动同类型门的个数,或称负载能力.一般门电路的扇出系数为8,驱动器的扇出系数 ...

- FPGA Timing笔记

很多FPGA工程师都会遇到timing的问题,如何让FPGA跑到更快的处理频率是永久话题.决定FPGA的timing关键是什么?如何才能跑到更快的频率呢? A. 第一步需要了解FPGA的timing路 ...

- FPGA的引脚VCCINT 、VCCIO VCCA

首先是看到FPGA在配置的时候有三种不同的电VCCINT .VCCIO VCCA,于是就查了下有什么不同: FPGA一般会有许多引脚,那它们都有什么用呢? VCCINT为施加于 FPGA 内核逻辑的电 ...

- FPGA与simulink联合实时环路系列——实验一 测试

实验一 测试 实验内容 在simulink创建测试模块,通过测试模块产生信号,再传送到FPGA,FPGA读出后再将信号无处理传送回simulink进行显示.由此来测试整个硬件在环的功能是否正常,并且熟 ...

- FPGA与simulink联合实时环路系列—开篇

FPGA与simulink联合实时环路系列—开篇 作为网络上第一个开源此技术,笔者迫不及待地想将此技术分享出来,希望大家多多支持.笔者从2011年接触FPGA以来,从各个方面使用FPGA,无论是控制. ...

随机推荐

- JNI简单HelloWorld

1.编写Java代码 建立hello目录,编写HelloWorld.java: class HelloWorld { public native void displayHelloWorld(); s ...

- Spring:通配符的匹配很全面, 但无法找到元素 XXXXX' 的声明

问题:配置Spring的时候容易发生如题的这样一个经常性的错误,错误如下(以context为例) org.springframework.beans.factory.xml.XmlBeanDefini ...

- 使用maven时报错An error occurred while filtering resources

解决办法:右键项目-->maven-->update project .

- Word批量设置表格宽度自动适应页面宽度

怎么批量修改Word表格的宽度呢.Word表格可根据窗口自动调整表格宽度,使得所有的表格宽度和页面宽度一样. 当页面设置了新的页边距后,所有的表格都需要调整新的宽度.或者文档中有许多大大小小的表格,希 ...

- CSS颜色表示法、颜色表(调色板)

1.CSS 颜色使用组合了红绿蓝颜色值 (RGB) 的十六进制 (hex) 表示法进行定义.对光源进行设置的最低值可以是 0(十六进制 00).最高值是 255(十六进制 FF). 2.十六进制值使用 ...

- 基于suse linux系统的cacti系统部署——rpm包方式

豆丁 http://www.docin.com/p-191889788.html rpm包方式:啊扬--沙迳:2010-12-1:更改:2011/5/16:一.Cacti的简介(来源:网络):Cact ...

- 析构函数和Dispose方法的区别

1. 析构函数(Finalize)只能释放非托管资源, 它是由GC调用. 2. Dispose方法可以释放托管资源和非托管资源,它是由用户手动调用的. 在Dispose()中调用 GC.Suppres ...

- js、jq、ajax之间的关系

一句话:js是一种客户端脚本语言,jq是在js基础上封装起来的一个开发工具,ajax是基于js的一种技术(异步刷新). javascript是一种在客户端执行的脚本语言,用来给网页添加动态功能,使网页 ...

- Codeforces Round #394 (Div. 2) E. Dasha and Puzzle

E. Dasha and Puzzle time limit per test:2 seconds memory limit per test:256 megabytes input:standard ...

- Node大文件处理

之前有个需求要将文件解析再处理,当时直接将整个文件内容读到内存中然后解析,也是没有考虑到大文件的问题,那么要如何解析大文件呢? 输入:文件的内容是多个json,按顺序排列 输出:解析后的json数据 ...