Verilog HDL那些事_建模篇笔记(实验八:键盘解码)

1.PS2接口与协议时序图

对于PS2的接口来说,需要额外关注的是PIN5与PIN1,一个是时钟,一个是数据。PS2协议对数据的移位是“CLOCK下降沿”有效,其CLOCK的频率通常在10KHz左右。每当CLOCK的下降沿到来时,发送一位数据。

协议时序图

传输数据定义表

|

第N位 |

属性 |

|

0 |

开始位 |

|

1~8 |

数据位 |

|

9 |

校验位 |

|

10 |

结束位 |

要想获得键盘的数据,我们只需要关注(1~8)数据位,其余的位可以忽略,但程序中要给出相应的处理。

2.电平检测模块

下面对PS2解码过程建模,本模型有两个输入,PS2的时钟信号输入与PS2的数据输入。其中电平检测模块用于检测PS2的“下降沿”,当下降沿到来时,使能PS2解码模块,解码模块对输入的每一帧数据进行解码,最后将解码后的数据输出,并产生一个解码完成信号。

以上为检测下降沿到来的always块语句。对于电平检测模块的编写一般遵循以下技巧:设定两个reg型变量,一个用来接收新的时钟周期传进来的电平信号,另外一个用来存储上一个时钟周期的电平信号。即:

H2L_F1 <= PS2_CLK_Pin_In;

H2L_F2 <= H2L_F1;

其中需要说明的是,以上两个语句采用的是非阻塞式赋值,非阻塞式赋值语句是在整个模块结束之际才完成赋值操作。

位于begin/end块内的多条非阻塞式赋值语句是并行执行的,这些非阻塞赋值语句都会在其中任何一条语句执行完成之前开始执行。这是硬件电路的特点,因为实际的逻辑门电路都是独立工作的,而不是等到其他门电路运转结束之后自己才开始运转。

因此,第一条赋值语句并不会立刻改变H2L_F1的值。而是H2L_F1与H2L_F2的值是同时刷新的。

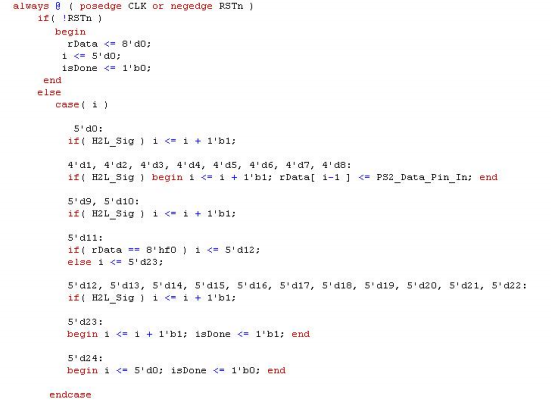

3.解码模块

解码模块的输入为键盘码数据与解码使能信号,输出为解码后的数据与解码完成信号。

键盘码的数据是一位一位传给解码模块的,即PS2的时钟由高电平跳变到低电平时,传入键盘码的一位数据。always块语句中的i是一个状态标志位,用来控制状态变化后的相应操作。

4’d1,4’d2,4’d3......:

If(H2L_Sig) begin i <= i + 1’b1; rData[i-1] <= PS2_Data_Pin_In; end

当PS2时钟信号由高变低,需要作出的处理有:将系统转移到下一个状态,接收当前传来的数据。

注意:本实验有两个时钟,一个是系统时钟,带动整个系统运行。一个是PS2的时钟,用来接收键盘传过来的数据。

Verilog HDL那些事_建模篇笔记(实验八:键盘解码)的更多相关文章

- Verilog HDL那些事_建模篇笔记(实验一,实验二)

实验一:永远的流水灯 扫描频率配置为100Hz,即是说扫描周期为10ms.这里需要注意的是扫描周期的概念.流水灯嘛,顾名思义,扫描周期指的是流水灯扫一轮所需要的时间.听到说周期,就应该想到在建模的时候 ...

- Verilog HDL那些事_建模篇笔记(实验九:VGA驱动)

1.了解VGA协议 VGA协议有5个输入信号,列同步信号(HSYNC Signal),行同步信号(VSYNC Signal),红-绿-蓝,颜色信号(RGB Signal). 一帧屏幕的显示是由行从上至 ...

- Verilog HDL那些事_建模篇笔记(实验七:数码管电路驱动)

1.同步动态扫描 多个数码管的显示采用的是同步动态扫描方法,同步动态扫描指的是:行信号和列信号同步扫描,是一种并行操作. 2.数码管驱动电路实现思路 如果要求数码管显示我们想要的数字,首先需 ...

- Verilog HDL那些事_建模篇笔记(实验三:按键消抖)

实验三:按键消抖 首先将按键消抖功能分成了两个模块,电平检查模块和10ms延迟模块.电平检测模块用来检测按键信号的变化(是否被按下),10ms延迟模块用来稳定电平检查模块的输入,进而稳定按键信号,防止 ...

- 基于Verilog HDL 的数字时钟设计

基于Verilog HDL的数字时钟设计 一.实验内容: 利用FPGA实现数字时钟设计,附带秒表功能及时间设置功能.时间设置由开关S1和S2控制,分别是增和减.开关S3是模式选择:0是正常时钟 ...

- 【黑金教程笔记之003】【建模篇】akuei2的Verilog hdl心路

Verilog hdl不是“编程”是“建模” Verilog hdl语言是一种富有“形状”的语言. 如果着手以“建模”去理解Verilog hdl语言,以“形状”去完成Verilog hdl语言的设计 ...

- 【转】Verilog HDL常用建模方式——《Verilog与数字ASIC设计基础》读书笔记(四)

Verilog HDL常用建模方式——<Verilog与数字ASIC设计基础>读书笔记(四) Verilog HDL的基本功能之一是描述可综合的硬件逻辑电路.所谓综合(Synthesis) ...

- Verilog HDL实用教程笔记

Verilog HDL实用教程笔记 DRC - Design Rule Check 几何规则检查ERC - Electrical Rule Check 电学规则检查自动参数提取LVS - Logic ...

- 【黑金教程笔记之003】【建模篇】【Lab 02 闪耀灯和流水灯】—笔记

(1) 扫描频率和闪耀频率? 模块: /**************************************** module name:flash_module function ...

随机推荐

- winform中listview imagelist问题

参考:http://www.it165.net/pro/html/201410/23603.html 关于imagelist失真问题: 1.颜色 将ColorDepth属性设置成Depth32Bit ...

- 简单理解Struts2中拦截器与过滤器的区别及执行顺序

简单理解Struts2中拦截器与过滤器的区别及执行顺序 当接收到一个httprequest , a) 当外部的httpservletrequest到来时 b) 初始到了servlet容器 传递给一个标 ...

- BackTrack5-r3安装VMware Tools

bt login:root //默认的BT系统账号password:toor //默认的BT系统密码,这里的密码是不显示的.root@bt:~#startx //进入图形模式 启动BT虚拟机系统-在V ...

- Struts2框架下表单数据的流向以及映射关系

本例框架很简单:默认页面为用户登录界面login.jsp,提交后由action类LoginAction.java来判断成功或失败,登录结果分别由success.jsp和failure.jsp呈现. 一 ...

- MVCC PostgreSQL实现事务和多版本并发控制的精华

原创文章,同步发自作者个人博客,http://www.jasongj.com/sql/mvcc/ PostgreSQL针对ACID的实现机制 事务的实现原理可以解读为RDBMS采取何种技术确保事务的A ...

- entity framework 数据加载三种方式的异同(延迟加载,预加载,显示加载)

三种加载方式的区别 显示加载: 显示加载

- mysqlbinlog 参数及用法说明

mysqlbinlog用法说明 服务器生成的二进制日志文件写成二进制格式.要想检查这些文本格式的文件,应使用mysqlbinlog实用工具.应这样调用mysqlbinlog:shell> mys ...

- akka各模块

Akka的模块化做得非常好,它为不同的功能提供了不同的Jar包. akka-actor-2.0.jar – 标准Actor, 有类型Actor,等等 akka-remote-2.0.jar – 远程A ...

- 在Android Studio中使用lambda表达式

build.gradle中添加以下配置 Android{ ..... compileOptions { sourceCompatibility JavaVersion.VERSION_1_8 targ ...

- serialVersionUID的作用

Java的序列化机制是通过在运行时判断类的serialVersionUID来验证版本一致性的.在进行反序列化时,JVM会把传来的字节流中的serialVersionUID与本地相应实体(类)的seri ...