模拟摄像头解码模块最新测试 TVP5150模块 FPGA+SDRAM+TVP5150+VGA 实现PAL AV输入 VGA视频输出

模拟摄像头解码模块最新测试 TVP5150模块 FPGA+SDRAM+TVP5150+VGA 实现PAL AV输入 VGA视频输出

测试使用电视机顶盒的AV模拟信号输入,VGA显示器输出测试,效果如下

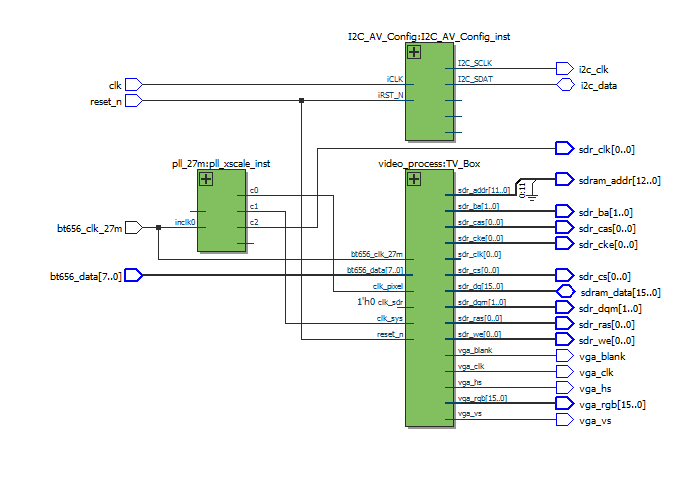

FPGA使用verilog编程,顶层RTL视图如下

module action_vip(

input clk,

input reset_n,

input bt656_clk_27m,

input [7:0] bt656_data,

output [12:0] sdram_addr,//

output [1:0] sdr_ba,

output [0:0] sdr_cas,

output [0:0] sdr_cke,

output [0:0] sdr_cs,

inout [15:0] sdram_data,

output [1:0] sdr_dqm,

output [0:0] sdr_ras,

output [0:0] sdr_we,

output [0:0] sdr_clk,

output vga_clk,

output vga_blank,

output vga_hs,

output vga_vs,

output [15:0] vga_rgb,

output i2c_clk,

inout i2c_data

//output [5:0] leds

);

wire clk_sys;

wire clk_sys_p90;

wire clk_pixel;

wire clk_xscale;

wire clk_24m;

//reg clk_pixel;

//pll_xscale pll_xscale_inst

pll_27m pll_xscale_inst

(

.inclk0 ( bt656_clk_27m/*clk_0*/ ),

.c0 ( /*clk_xscale*/clk_pixel ),

.c1 ( clk_sys ),

.c2 (clk_sys_p90)

);

/*

odd_div #(

.DIV_NUM (5)

)

odd_div_inst(

.clk ( clk_sys ), // input clk_sig

.rst_n ( reset_n ), // input rst_n_sig

.clkout ( clk_24m ) // output clkout_sig

);

*/

//assign clk_o = clk;//clk_24m;//

assign sdr_clk = clk_sys_p90;

assign sdram_addr[12] = 1'b0;

video_process TV_Box

(

.reset_n(reset_n) , // input reset_n_sig

.clk_sys(clk_sys) , // input clk_sys_sig

.clk_sdr(clk_sdr) , // input clk_sdr_sig

.clk_pixel(clk_pixel) , // input clk_pixel_sig

.bt656_clk_27m(bt656_clk_27m) , // input bt656_clk_27m_sig

.bt656_data(bt656_data) , // input [7:0] bt656_data_sig

.vga_clk(vga_clk) , // output vga_clk_sig

.vga_blank(vga_blank) , // output vga_blank_sig

.vga_hs(vga_hs) , // output vga_hs_sig

.vga_vs(vga_vs) , // output vga_vs_sig

.vga_rgb(vga_rgb) , // output [23:0] vga_rgb_sig

.sdr_addr(sdram_addr) , // output [11:0] sdr_addr_sig

.sdr_ba(sdr_ba) , // output [1:0] sdr_ba_sig

.sdr_cas(sdr_cas) , // output [0:0] sdr_cas_sig

.sdr_cke(sdr_cke) , // output [0:0] sdr_cke_sig

.sdr_cs(sdr_cs) , // output [0:0] sdr_cs_sig

.sdr_dq(sdram_data) , // inout [15:0] sdr_dq_sig

.sdr_dqm(sdr_dqm) , // output [1:0] sdr_dqm_sig

.sdr_ras(sdr_ras) , // output [0:0] sdr_ras_sig

.sdr_we(sdr_we) // output [0:0] sdr_we_sig

// ,.sdr_clk(sdr_clk) // output [0:0] sdr_clk_sig

);

I2C_AV_Config I2C_AV_Config_inst( // Host Side

.iCLK(clk),

.iRST_N(reset_n),

// I2C Side

.I2C_SCLK(i2c_clk),

.I2C_SDAT(i2c_data)

);

endmodule

联合博客技术交流(您可以通过以下方式了解,关注我们的博客和交流)

http://blog.chinaaet.com/shenyae86

http://www.openedv.com/posts/list/58978.htm

http://www.cnblogs.com/ccjt/

http://blog.sina.com.cn/u/5625282126

http://xinanhejishu.blog.163.com/

QQ交流群:层层惊涛 26210916

辐射防护交流群 224673609

百度云盘资料下载

http://yun.baidu.com/s/1kThKzaf

http://yun.baidu.com/s/1c0SKEC4

http://yun.baidu.com/s/1mgVml3i

模拟摄像头解码模块最新测试 TVP5150模块 FPGA+SDRAM+TVP5150+VGA 实现PAL AV输入 VGA视频输出的更多相关文章

- 基于iCamera测试模拟摄像头-TVP5150模块小结

基于iCamera测试模拟摄像头-TVP5150模块小结 首先先认识下模拟摄像头,相信大家都不陌生, CCD模拟摄像头 CMOS模拟摄像头 可以看到,ccd摄像头电路较复杂,接口少,而cmos摄像头, ...

- TVP5150 PAL/NTSC ccd cmos 模拟摄像头视频 转换 VGA输出

新做了一批 视频模块,特此总结下: 解码ic:tvp5150 输入:CVBS PAL 输出:DVP(bt565 yuv dvp8 含vs hs) 测试分辨力:(vga输出 640*480) 实 ...

- 模拟摄像头,AV视频信号线解码,PAL制 NTSC,输入解码显示,终于搞定,记录下!

模拟摄像头,AV视频信号线解码,PAL制 NTSC,输入解码显示,终于搞定,记录下! 咱们常用的摄像头,监控等,大多数都是AV信号,国内制式都是PAL,采用同轴,传输,这样的好处在于,传输距离可以很长 ...

- 图像处理:卷积模块FPGA 硬件加速

本文记录了利用FPGA加速图像处理中的卷积计算的设计与实现.实现环境为Altera公司的Cyclone IV型芯片,NIOS II软核+FPGA架构. 由于这是第一次设计硬件加速模块,设计中的瑕疵以及 ...

- .net单元测试——常用测试方式(异常模拟、返回值测试、参数测试、数据库访问代码测试)

最近在看.net单元测试艺术,我也喜欢单元测试,今天介绍一下如何测试异常.如何测试返回值.如何测试模拟对象的参数传递.如何测试数据库访问代码.单元测试框架使用的是NUnit,模拟框架使用的是:Rhin ...

- surging如何使用swagger 组件测试业务模块

1.前言 微服务架构概念的提出已经有非常长一段时间了,但在近期几年却开始频繁地出现,大家都着手升级成微服务架构,使用着各种技术,大家认为框架有服务治理就是微服务,实现单一协议的服务调用,微服务虽然没有 ...

- fiddler学习总结--通过Fiddler模拟弱网进行测试

弱网测试的目的: 弱网测试可以发现一些因为网络问题导致的交互问题,从而更好的完善应用的性能. 关注点:1.卡死,崩溃,无响应,闪退.2.业务交互数据传输正确性. 通过Fiddler可以模拟弱网进行测试 ...

- [原创]用Charles模拟App各种网络带宽测试介绍

[原创]用Charles模拟App各种网络带宽测试介绍 相信每个测试在进行自己公司App测试时,都会碰到一个问题,如何去模拟各种App在各种带宽下的测试情况,估计很少有公司直接去采用2g/3g/4g卡 ...

- 如何通过Fiddler模拟弱网进行测试

[本文出自天外归云的博客园] 弱网测试的目的 弱网测试可以发现一些因为网络问题导致的交互问题,从而更好的完善应用的性能. 弱网的模拟 通过Fiddler可以模拟弱网进行测试,拿手机测试举例,进行手机a ...

随机推荐

- thinkphp volist标签中加if判断的写法

<if condition="$vo['devstatus'] eq 1">在线<else /> 离线</if> IF标签用法 <if c ...

- C#:转义字符 \n 和 \r 的区别

1.\n,换行符,作用是换行符之后的字符换到下一行: 例如:1234/n567 得出的结果是1234 567 2.而\r,回车符,作用是回车符之后的字符会回到当前行的最前面,把回车符之前的字符覆 ...

- hdu 1028 Sample Ignatius and the Princess III (母函数)

Ignatius and the Princess III Time Limit: 2000/1000 MS (Java/Others) Memory Limit: 65536/32768 K ...

- 领扣(LeetCode)Fizz Buzz 个人题解

写一个程序,输出从 1 到 n 数字的字符串表示. 1. 如果 n 是3的倍数,输出“Fizz”: 2. 如果 n 是5的倍数,输出“Buzz”: 3.如果 n 同时是3和5的倍数,输出 “FizzB ...

- C语言1博客作业01

1 你对软件工程专业或者计算机科学与技术专业了解是怎样? 主修大数据技术导论.数据采集与处理实践(Python).Web前/后端开发.统计与数据分析.机器学习.高级数据库系统.数据可视化.云计算技术. ...

- python:模块1——标准库简介

一.文档 windows系统:IDLE中打开帮助文档 Tutorial:简单入门 Library Reference:python内置函数和标准库(看不完的,当做字典来查)(此外还有pypi(拍派社区 ...

- selenium滑块验证

使用selenium模拟登录解决滑块验证问题 本次主要是使用selenium模拟登录网页端的TX新闻,本来最开始是模拟请求的,但是某一天突然发现,部分账号需要经过滑块验证才能正常登录,如果还是模拟 ...

- Mac 下安装并配置 Tomcat

1,下载 点击 官网 ,进入下载页面, 2,安装 解压出来,即安装完成. 移动解压后的文件,换个文件目录(方便集中管理),将它改个名字(毕竟名字太长了). 我将其改名为 tomcat9 ,移入资源库目 ...

- Java开发中常用jar包整理及使用

本文整理了我自己在Java开发中常用的jar包以及常用的API记录. <!-- https://mvnrepository.com/artifact/org.apache.commons/com ...

- AppBoxFuture: 集成第三方Sql数据库

框架设计之初是不准备支持第三方数据库的,但最近几个朋友都提到需要将旧的基于传统Sql数据库的应用迁移到框架内,主要是考虑到一方面目前框架内置的分布式数据库尚未完善,另一方面是希望能逐步迭代旧应用替 ...