ZYNQ笔记(1):PL端——led灯

ZYNQ分为PS和PL,本篇文章实际上是Vivado中一个完整的FPGA工程的创建,正所谓万事开头难。

PS:处理系统 (Processing System) 即ARM部分

PL:可编程逻辑(Programable Logic) 即FPGA部分

一、新建工程

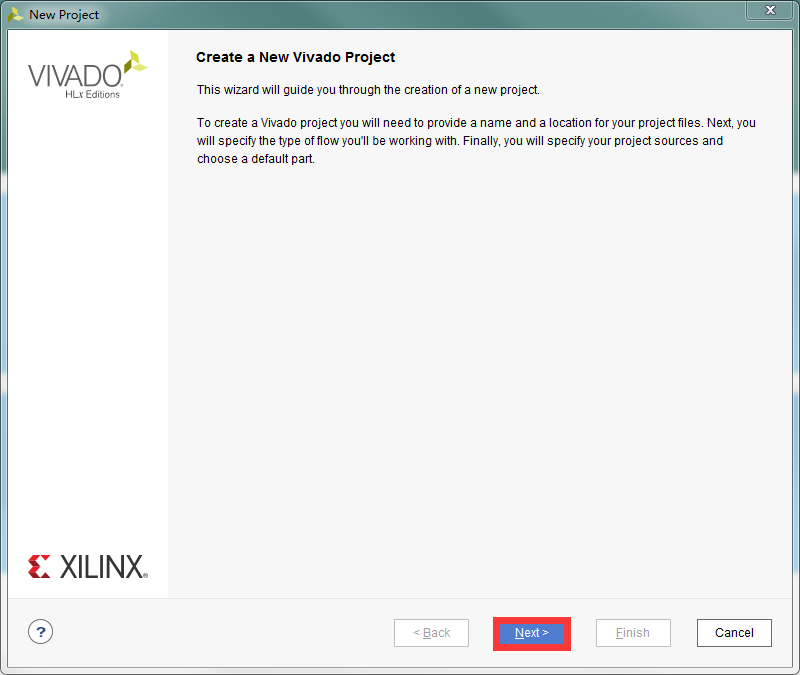

1.打开Vivado,新建一个工程,Next

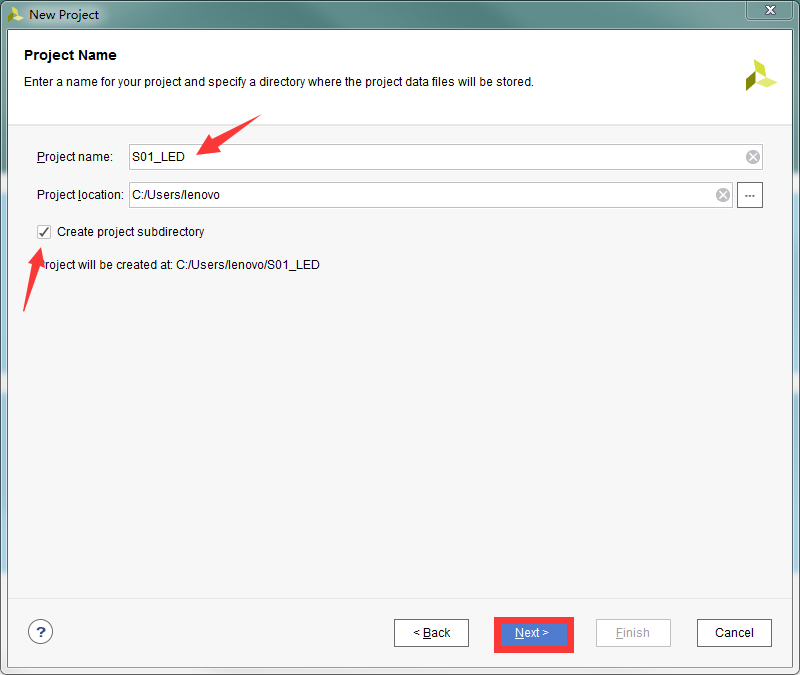

2.设置工程名称和工程所在目录,Next

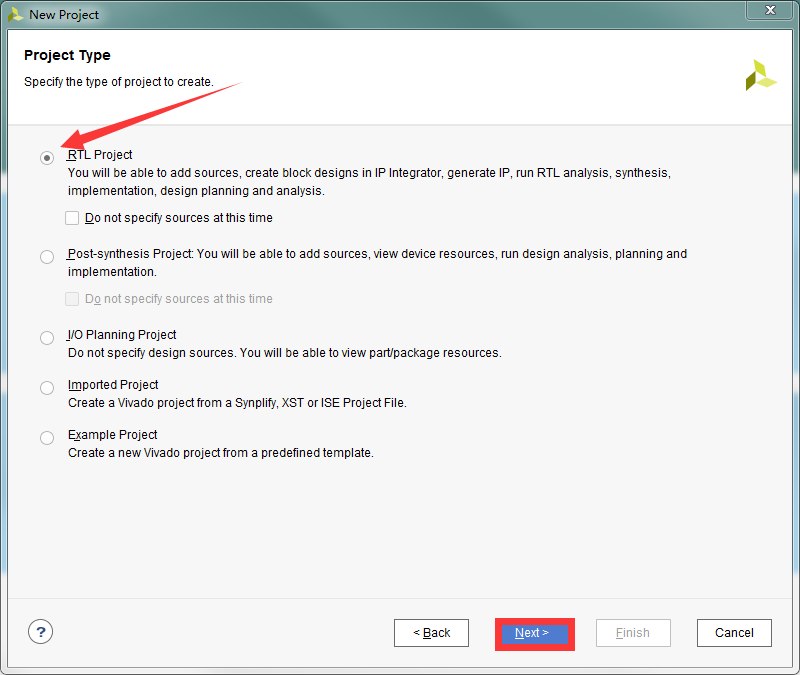

3.选择第一项:RTL Project,Next

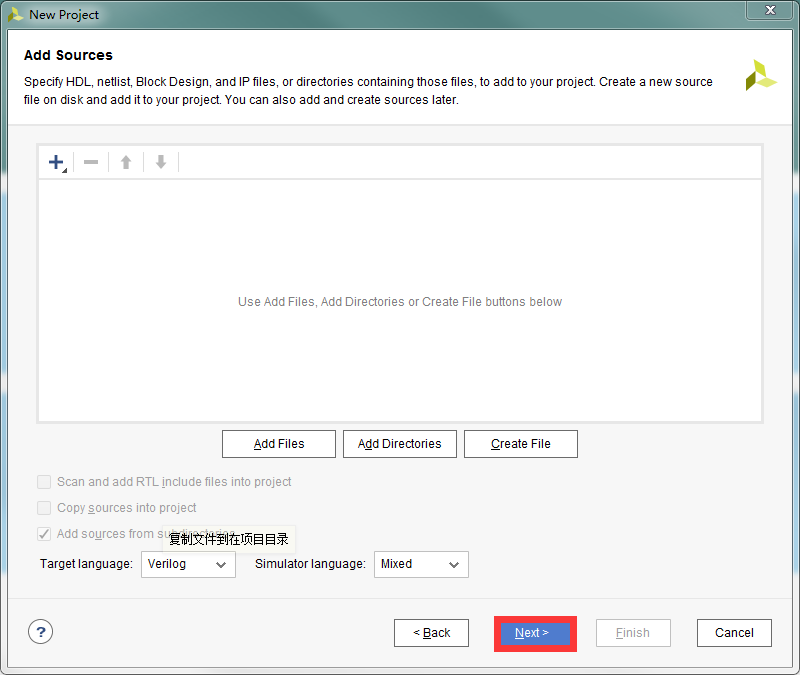

4.添加资源,可以直接Next

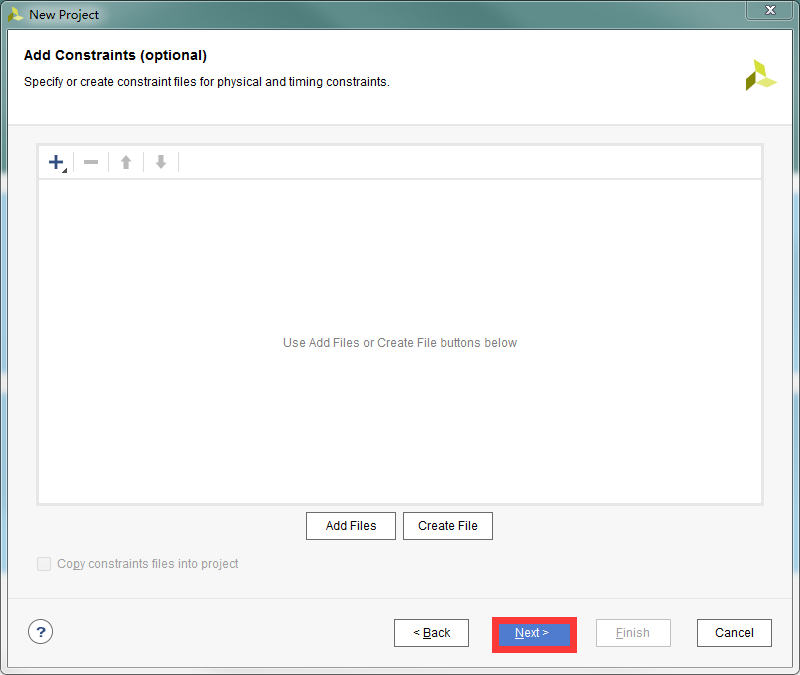

5.添加约束,可以直接Next

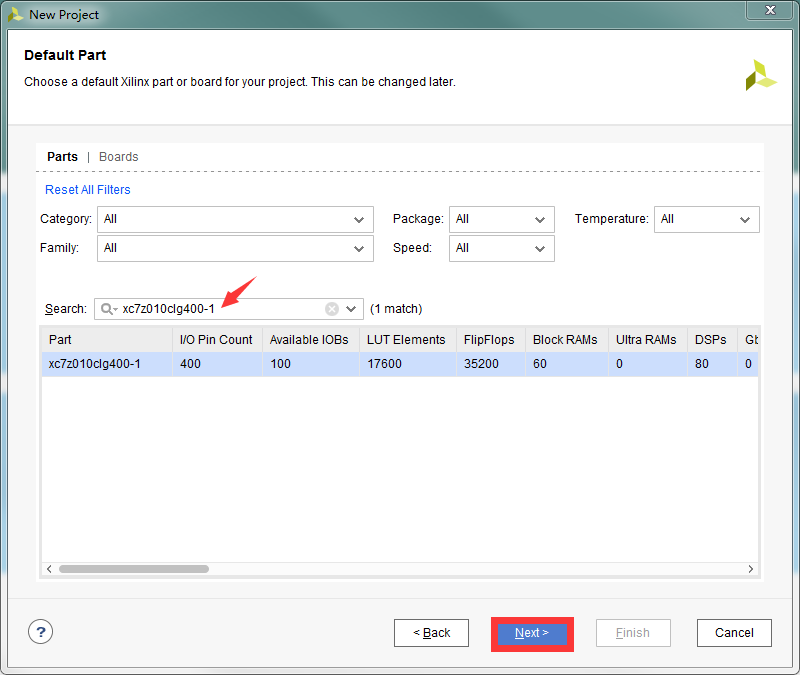

6.芯片型号选择xc7z020clg400-1,Next

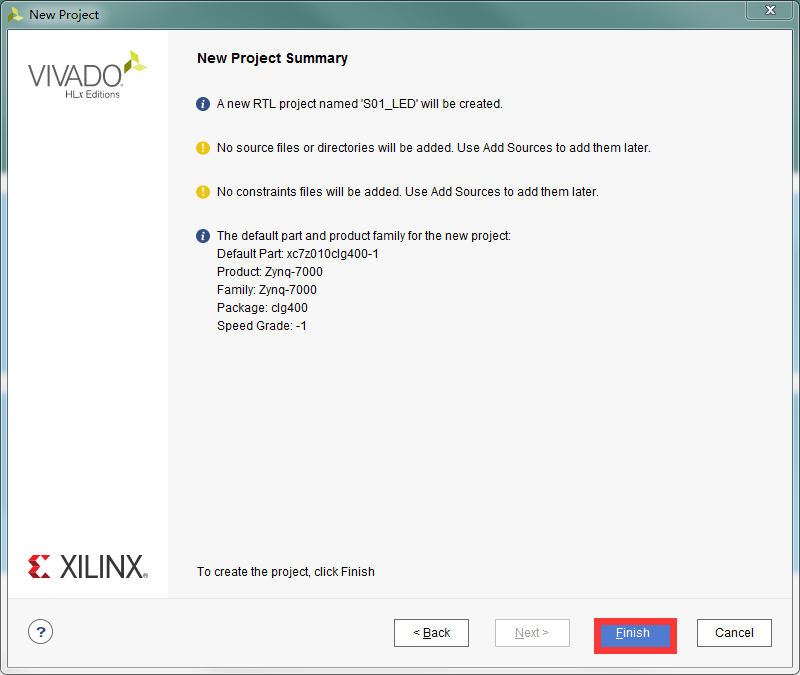

7.总结页面,Finish

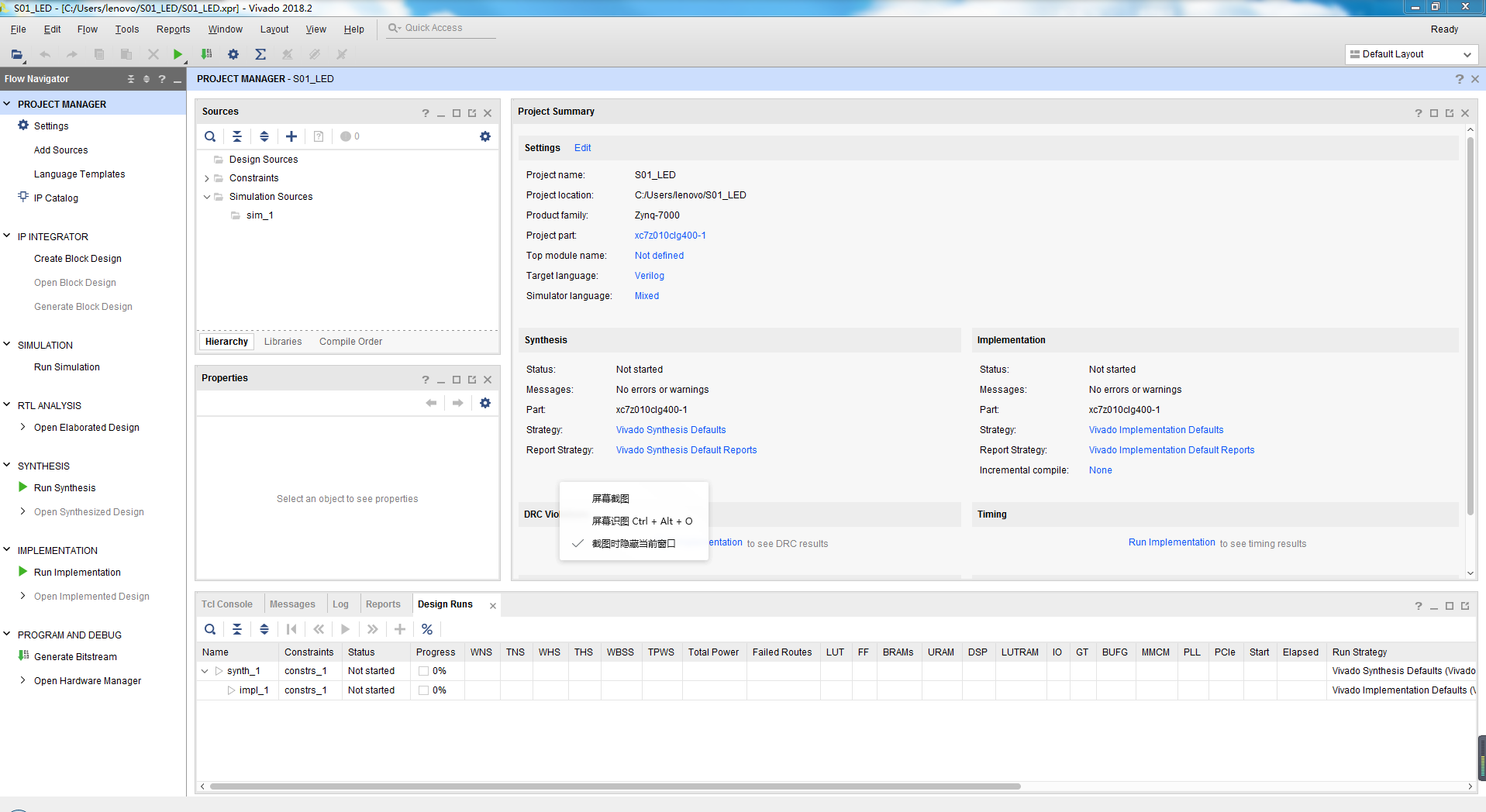

8.建好后的页面如下所示

二、PL端(FPGA)设置

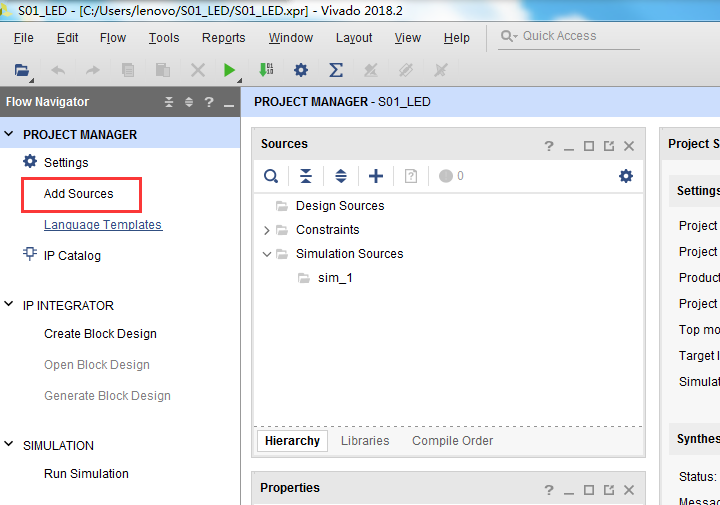

1.点击左侧导航栏的第一项PROJECT MANAGER --- Add Sources

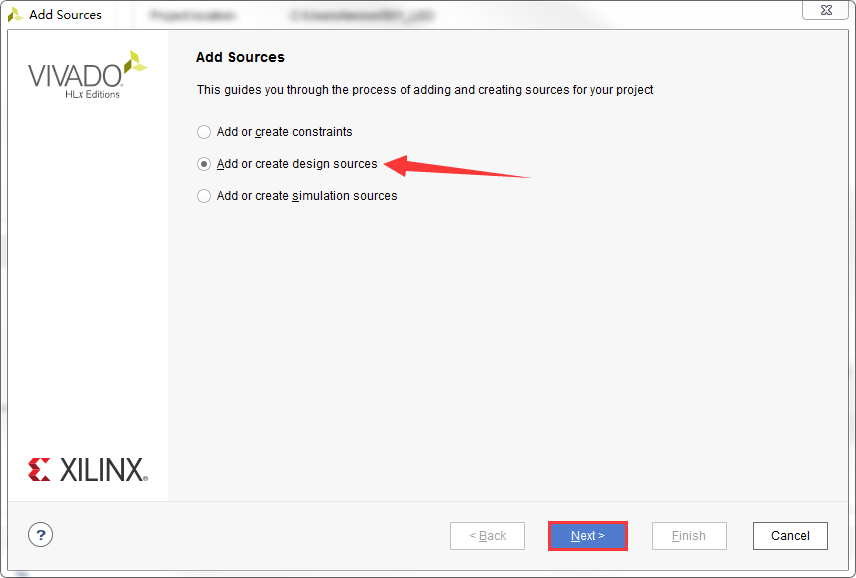

2.选择Add or create design sources,点击Next

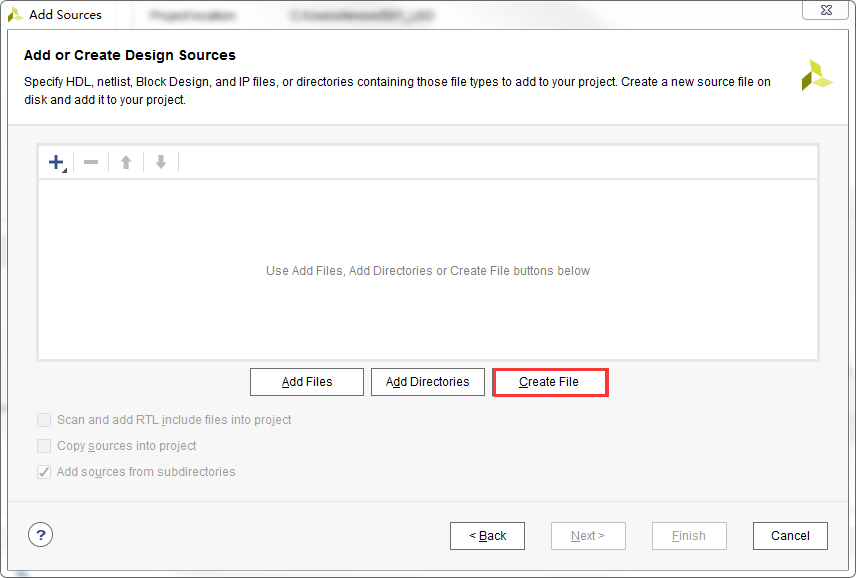

3.点击Create File来创建新的文件

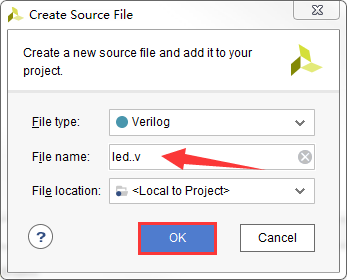

4.设置文件类型、文件名、文件位置,完了点OK

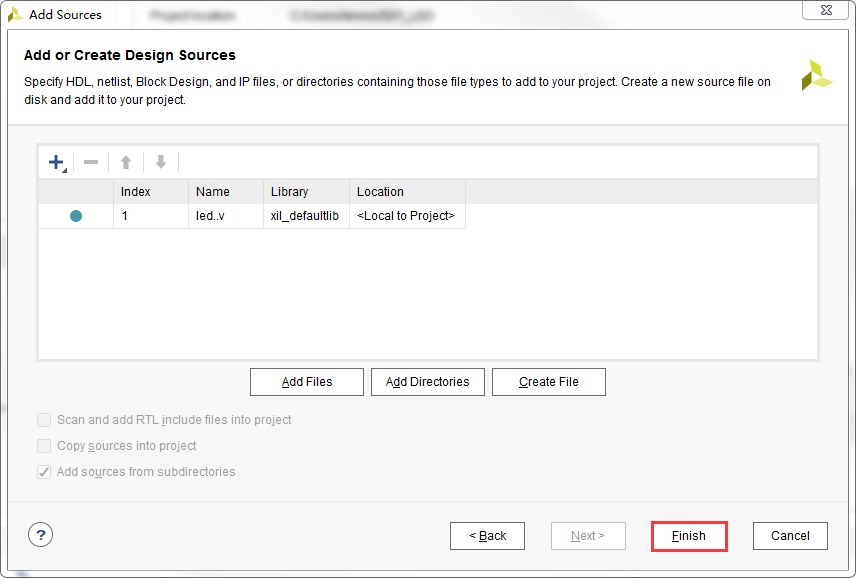

5.点击Finish

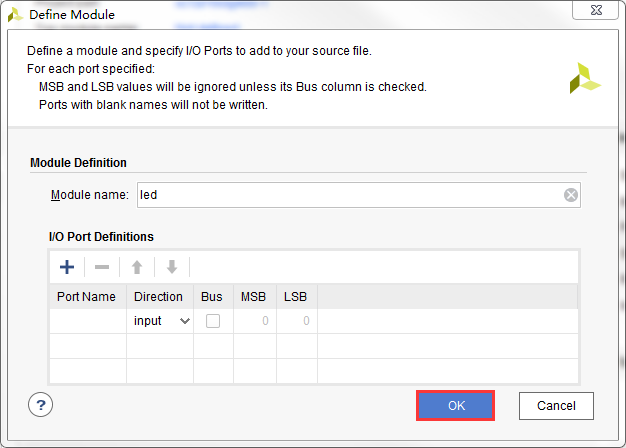

6.向导会提示定义 I/O 的端口,可以不定义,后面在程序中编写即可。

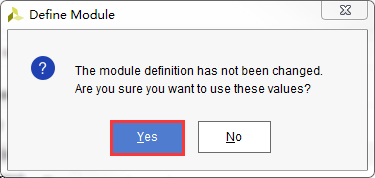

7.点击Yes

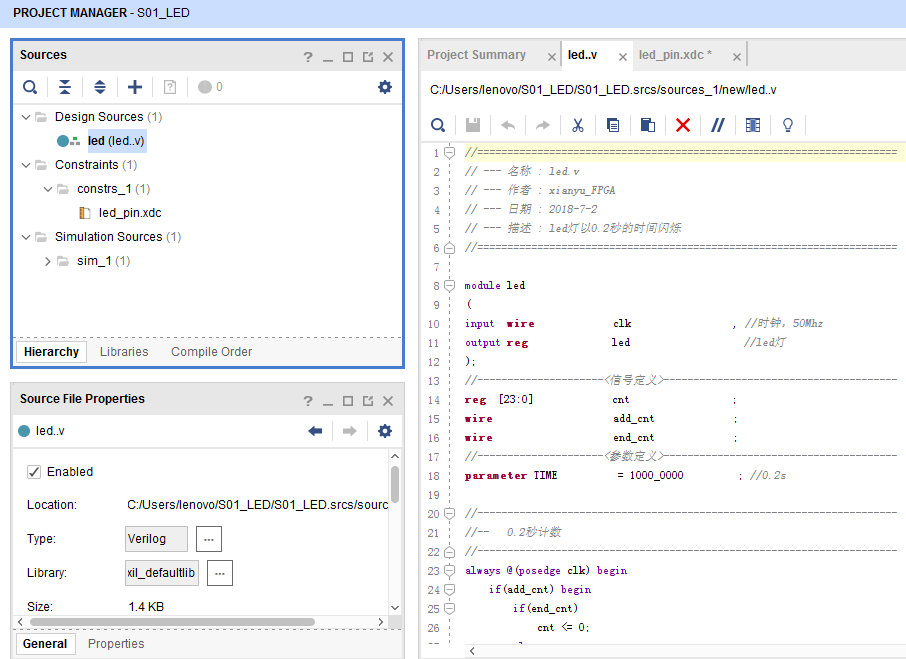

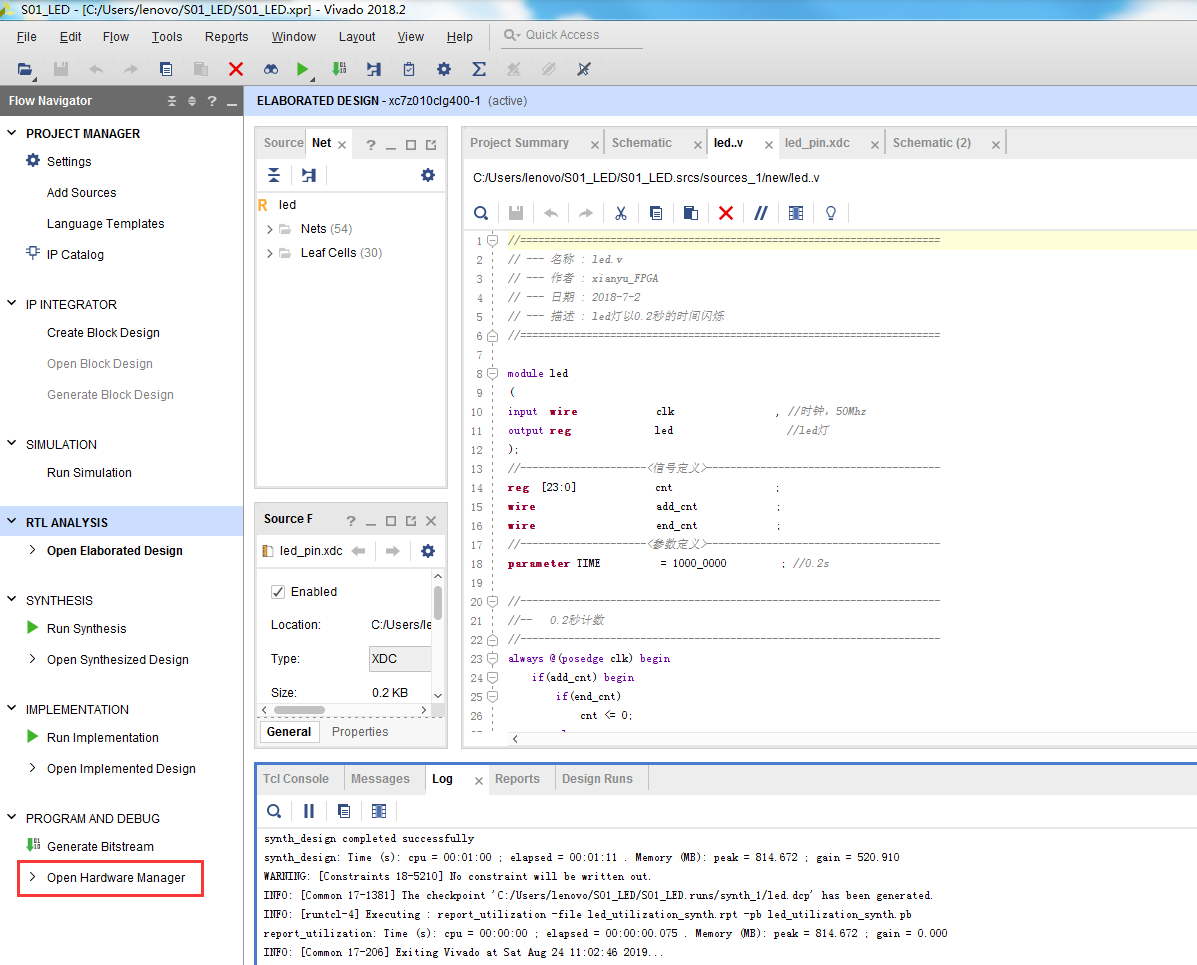

8.完成之后的页面如下所示,双击左侧 led 可以打开代码编辑页面,在里面编写Verilog代码,完成后按 Ctrl+S 保存

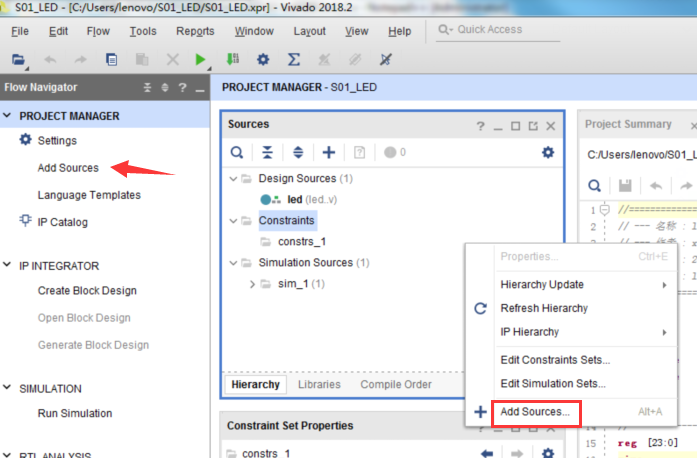

9.添加引脚约束文件,可以点击左侧导航栏的PROJECT MANAGER --- Add Sources,也可以直接在Sources空白处鼠标右键选择 Add Source

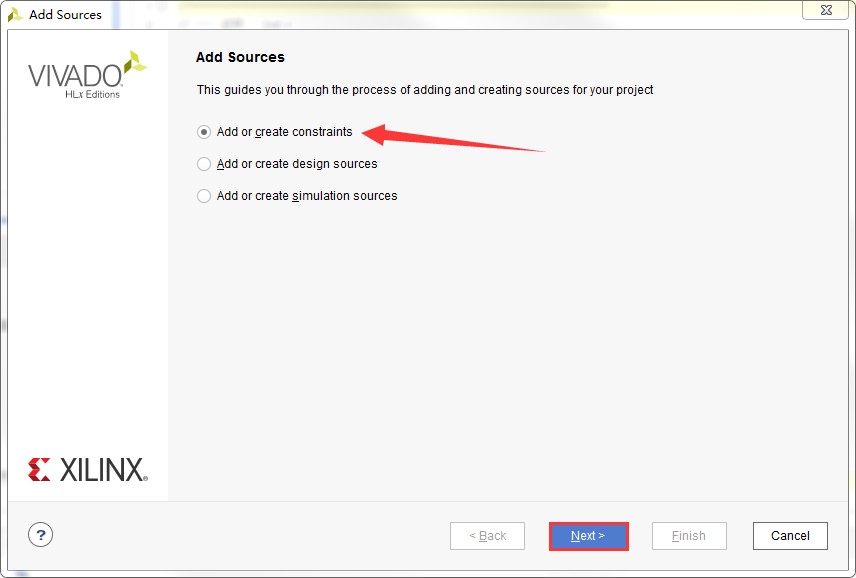

10.选择 Add or create constraints,点击Next

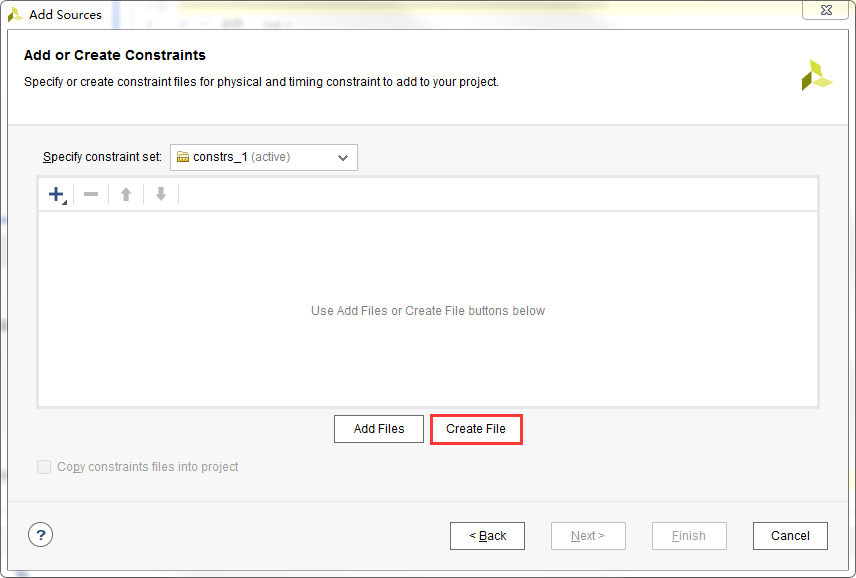

11.点击Create File来创建新的文件

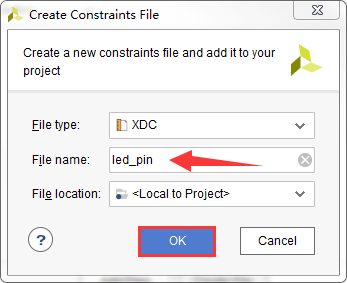

12.设置文件类型、文件名、文件位置,完了点OK

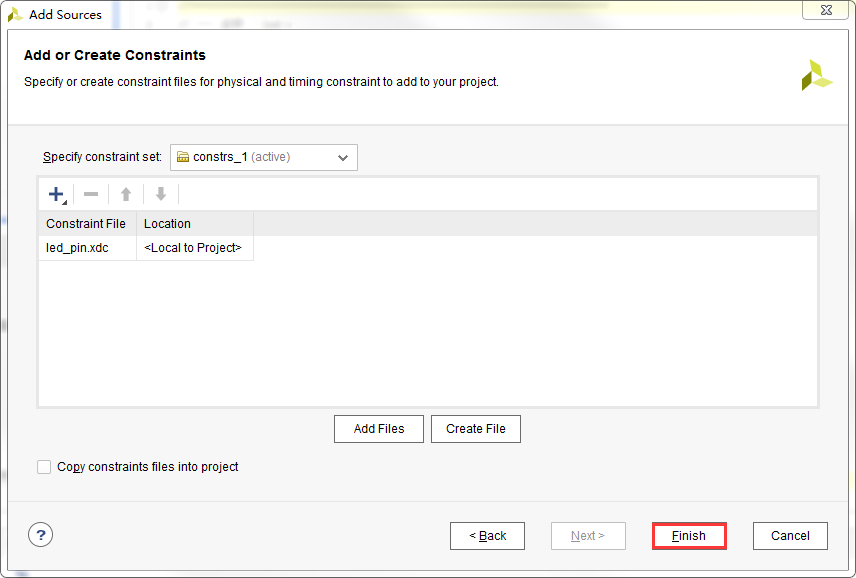

13.点击Finish

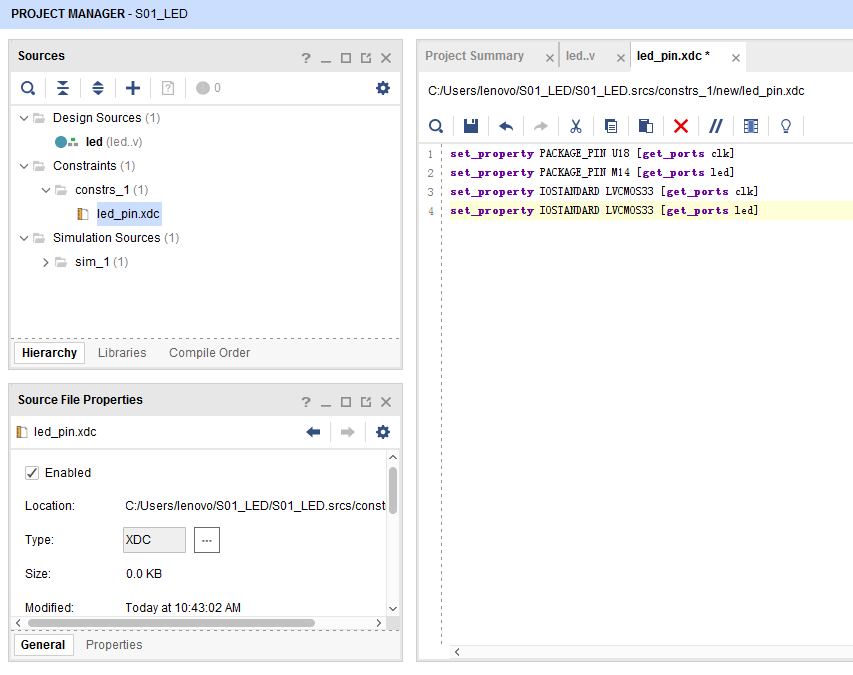

14.完成之后的页面如下所示,双击左侧 led_pin 可以打开代码编辑页面,在里面编写Tcl约束代码,完成后按 Ctrl+S 保存

最基本的XDC语法如下所示:

管脚约束:set_property PACKAGE_PIN "引脚编号" [get_ports “端口名称”]

电平约束:set_property IOSTANDARD "电压" [get_ports “端口名称”]

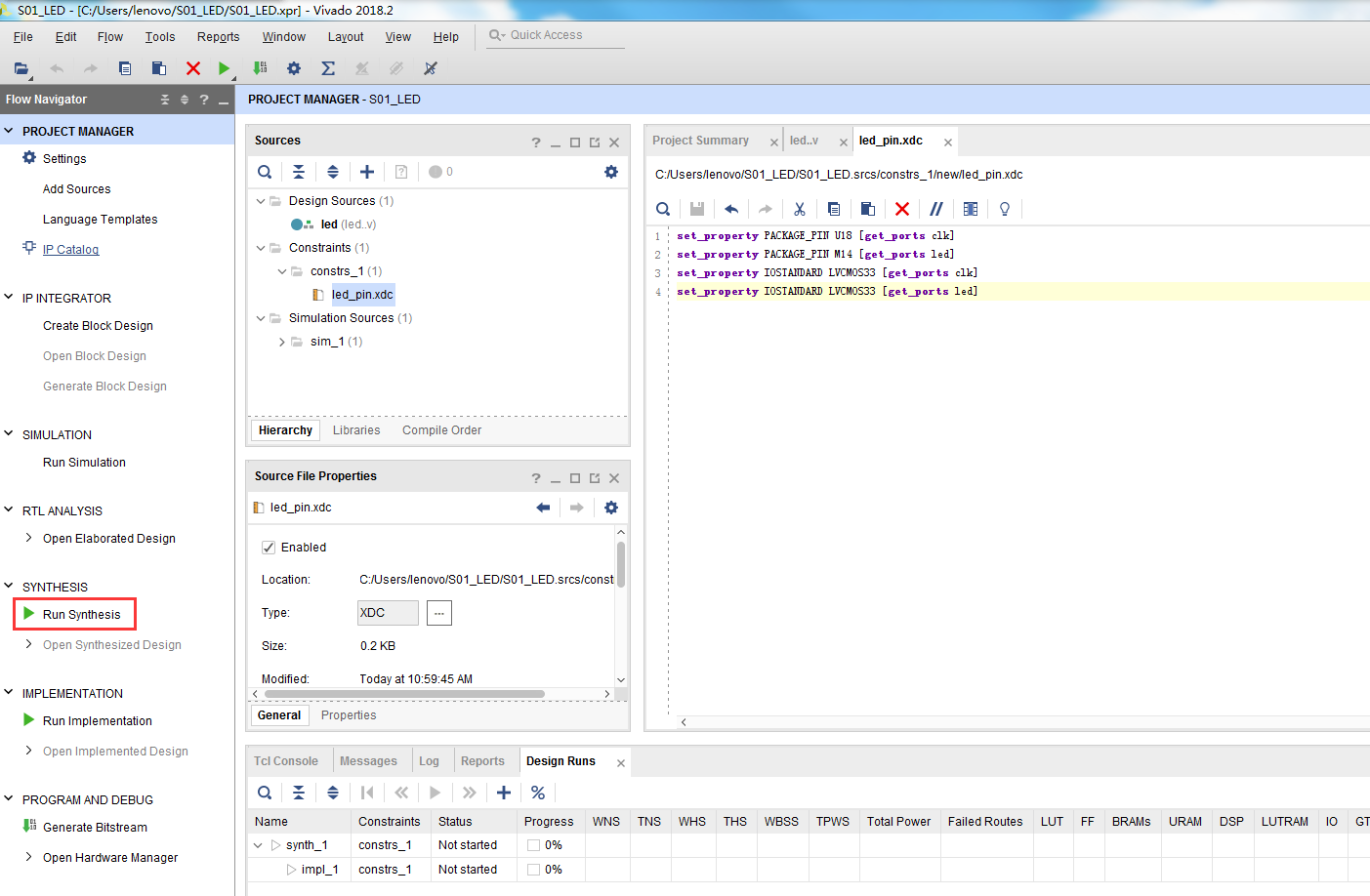

三、编译和综合

1.点击左侧导航栏的 RunSynthesis,即可开始综合并生成网表文件

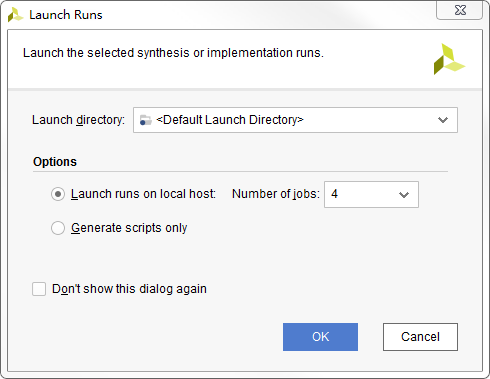

2.线程按照自己电脑配置选择,一般能选多大就多大

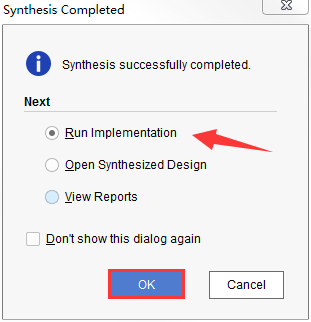

3.综合完成后弹出一个小窗口,选择 Run Implementation来开始布局布线

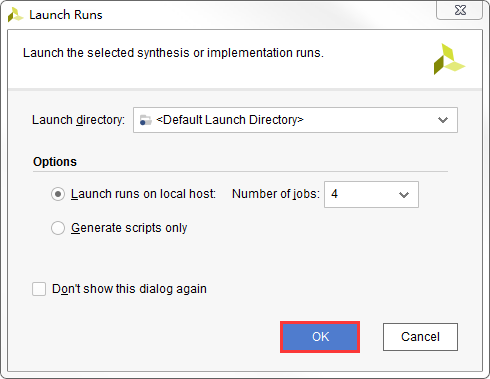

4.线程按照自己电脑配置选择,一般能选多大就多大

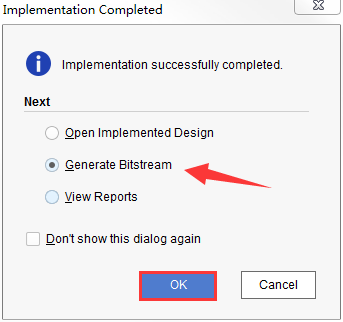

5.布线完成后弹出一个小窗口,选择 Generate Bitstream来生成下载用的bit文件

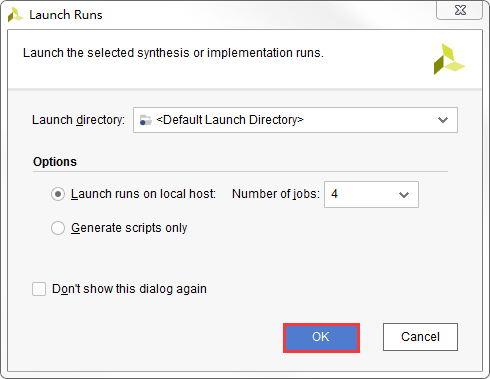

6.线程按照自己电脑配置选择,一般能选多大就多大

7.点击左侧导航栏的 Open Hardware Manager来下载bit流到板卡中

四、补充

1.编写完设计文件和约束文件后,编译和综合也可以直接点击左侧导航栏的按钮或者主页上方的快捷按钮。

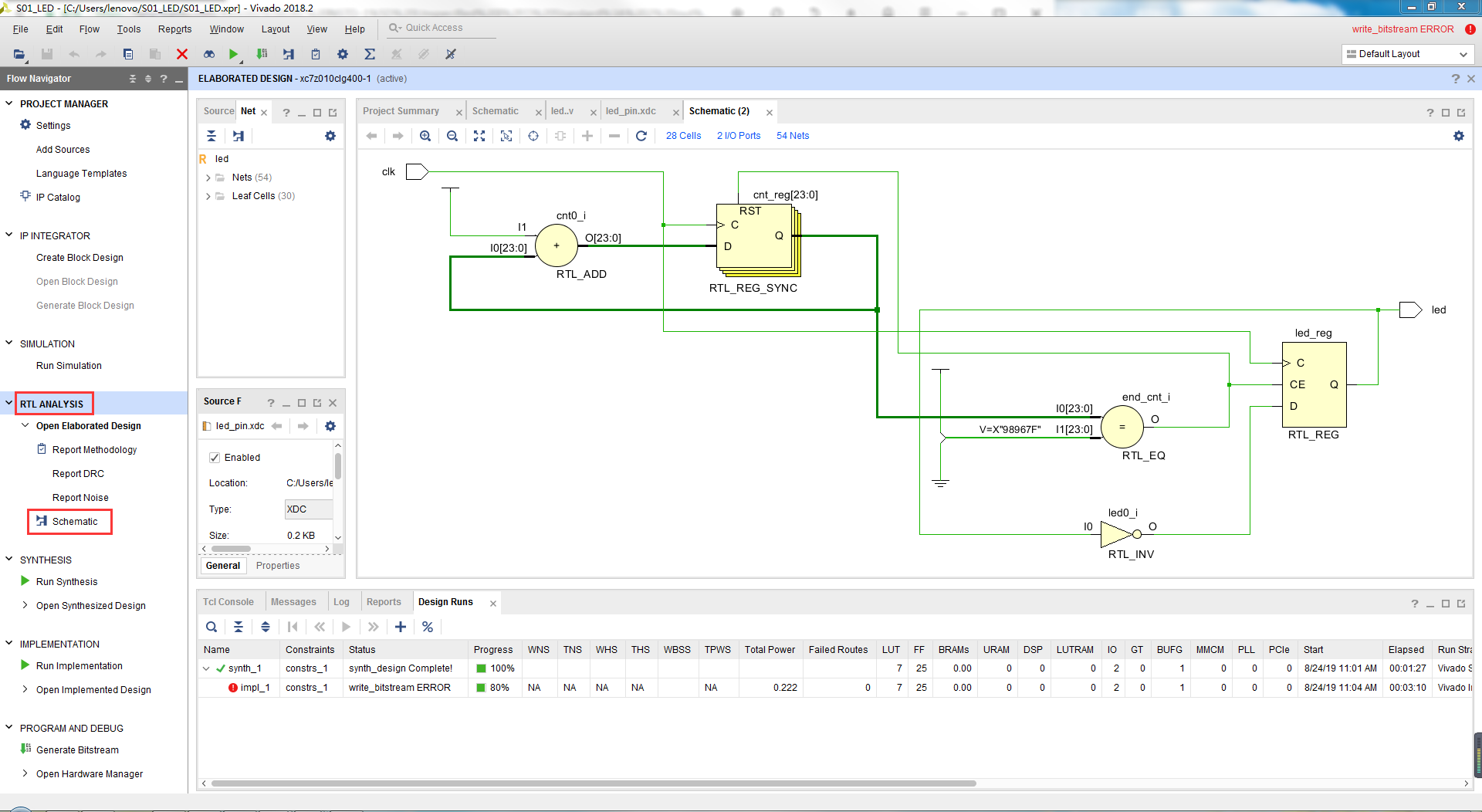

2.点击左侧导航栏的RTL ANALYSIS --- Schematic可以看到 RTL 视图,有时候 RTL 视图还是挺重要的。

3.添加约束文件可以打开RTL视图后,点击RTL视图上方的“I/O port”进行手动添加,保存后也可生成XDC文件。

参考资料:

[1]V3学院FPGA教程

[2]何宾, 张艳辉. Xilinx Zynq-7000嵌入式系统设计与实现[M]. 电子工业出版社, 2016.

ZYNQ笔记(1):PL端——led灯的更多相关文章

- ZYNQ笔记(3):GPIO的使用(MIO、EMIO)——led灯

一.GPIO原理 1.GPIO介绍 程序员通过软件代码可以独立和动态地对每个 GPIO 进行控制,使其作为输入.输出或中断. (1)通过一个加载指令,软件可以读取一个 GPIO 组内所有 GPIO 的 ...

- 在ZYNQ-7000平台上利用PS点亮PL上的LED灯

在ZYNQ-7000平台上利用PS点亮PL上的LED灯 1.实验方案 图1 实验方案系统框图 2.具体步骤 2.1.vivado工程建立 ①打开vivado集成开发环境,点击“Create Pr ...

- 51单片机学习笔记(郭天祥版)(1)——单片机基础和点亮LED灯

关于单片机型号的介绍: STC89C52RC40C-PDIP 0721CV4336..... STC:STC公司 89:89系列 C:COMS 52(还有51,54,55,58,516,):2表示存储 ...

- 嵌入式学习笔记(综合提高篇 第一章) -- 利用串口点亮/关闭LED灯

1 前言 从踏入嵌入式行业到现在已经过去了4年多,参与开发过的产品不少,有交换机.光端机以及光纤收发器,停车场出入缴费系统,二维码扫码枪,智能指纹锁以及数字IC芯片开发等; 涉及产品中中既有 ...

- ZYNQ笔记(2):PS端——Hello World !

PL端使用过后,来到了ZYNQ核心的部分:PS端,现在用Vivado软件对ZYNQ-7000开发板的PS端进行第一个程序设计:Hello World. 一.新建Vivado工程 1.打开Vivado, ...

- ZYNQ笔记(4):PL触发中断

一.ZYNQ中断框图 PL到PS部分的中断经过ICD控制器分发器后同时进入CPU1 和CPU0.从下面的表格中可以看到中断向量的具体值.PL到PS部分一共有20个中断可以使用.其中4个是快速中断.剩余 ...

- stm32开发笔记(三):stm32系列的GPIO基本功能之输出驱动LED灯、输入按键KEY以及Demo

前言 stm32系列是最常用的单片机之一,不同的版本对应除了引脚.外设.频率.容量等'不同之外,其开发的方法是一样的. 本章讲解使用GPIO引脚功能驱动LED灯和接收Key按钮输入. STM ...

- JZ2440开发板:用按键点亮LED灯(学习笔记)

本文是对韦东山嵌入式第一期学习的记录之一,如有您需要查找的信息,可以继续往下阅读. 想要用按键点亮LED灯,就需要知道按键和LED灯的相关信息,这样才可以进行之后的操作.阅读JZ2440的原理图,可以 ...

- zedboard如何从PL端控制DDR读写(七)

前面已经详细介绍了从PL端如何用AXI总线去控制DDR的读写,并且从AXI_BRESP的返回值来看,我们也是成功写入了的.但是没有通过别的方式来验证写入的数据的话,总是感觉差了点什么. 今天试了一把从 ...

随机推荐

- 用正确的姿势使用 celery

简介 celery 是一个简单.灵活.可靠的分布式系统,可以处理大量的消息. celery 是一个任务队列,关注实时处理,同时支持任务调度. 它的工作机制是这样的: 快速使用 安装:pip3 inst ...

- OpenVSwitch实验参考

1. 使用Floodlight管理OVS桥 (1) 下载:https://codeload.github.com/floodlight/floodlight/tar.gz/v1.2 (2) tar x ...

- Sequelize 数据类型

Sequelize.STRING // VARCHAR(255)Sequelize.STRING(1234) // VARCHAR(1234)Sequelize.STRING.BINARY // VA ...

- zabbix监控ESXI主机

ESXI6.0默认SSH关闭的,打开SSH的方法如下图: SSH打开后,主机会有警报,关闭警报的方法如下图 esxcli system snmp set --communities publi ...

- unity序列化

什么是序列化 unity的序列化在unity的开发中起着举重足轻的地位,许多核心的功能都是基于序列化和反序列化来实现的.序列化简单来讲就是就是将我们所要保存的数据进行二进制存储,然后当我们需要的时候, ...

- idea2017显示maven Project菜单

右侧就出现 maven project菜单了.

- 虚拟机ubuntu16下cheese打开摄像头黑屏问题

在win7上安装了一个ubuntu1604的虚拟机: 在虚拟机下打开电脑上连接的摄像头时,用ubuntu16自带的cheese软件查看是黑屏: 但是cheese上有摄像头名字显示,就是打不开:如下图 ...

- MLflow系列4:MLflow模型

英文链接:https://mlflow.org/docs/latest/models.html 本文链接:https://www.cnblogs.com/CheeseZH/p/11946260.htm ...

- 【Node.js】Node.js的安装

Node.js的简介 简单的说,Node.js 是运行在服务端的 JavaScript. Node.js 是一个基于Chrome JavaScript 运行时建立的一个平台. Node.js是一个事件 ...

- 多线程高效合作之master-warker模式

对于高并发的任务,有些任务是相互独立的,任务与任务之间没有依赖关系,因此可以采用 master - worker 模式. master 用于接受任务和分发任务给 worker,并将 worker 返回 ...