DDR3(4):读控制

写控制完成后开始设计读控制,写控制和读控制是非常相似的。

一、总线详解

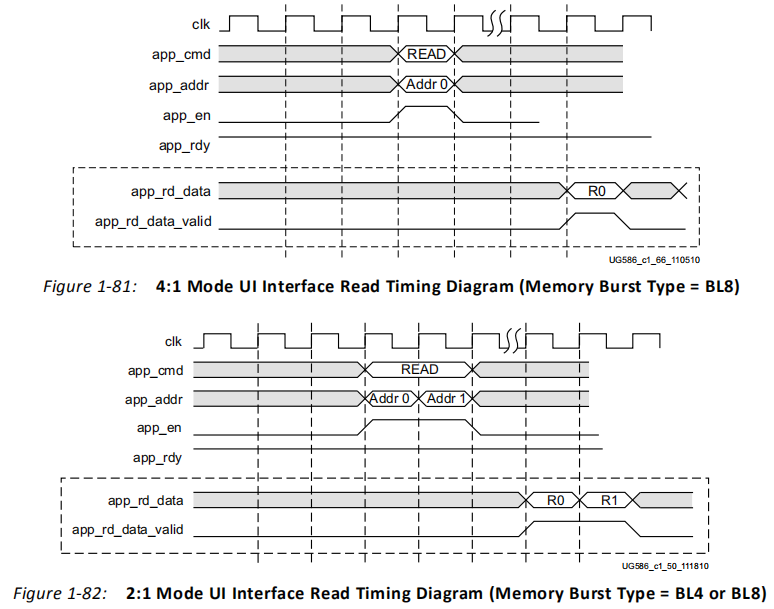

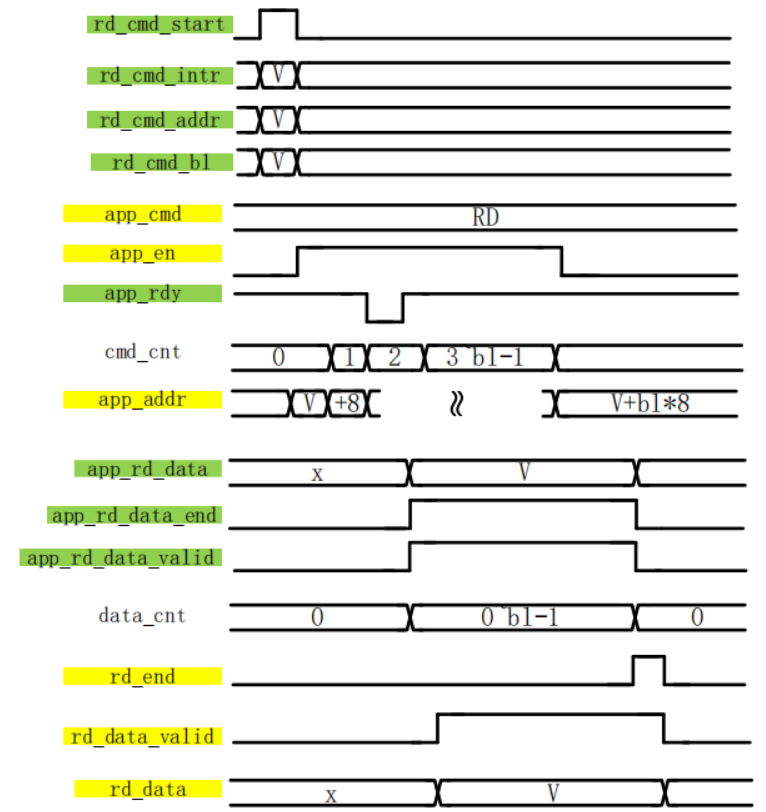

由 User Guide 可知各信号之间的逻辑关系,读数据是在给出命令之后一段时间后开始出现的。图中没有给出app_rd_data_end信号,此信号和app_wdf_end是相同的,即在DDR3的物理层端与用户端存在两种速率情况,此次设计速率为4:1,app_rd_data_end 和 app_rd_data_valid 相同。

二、读控制模块设计

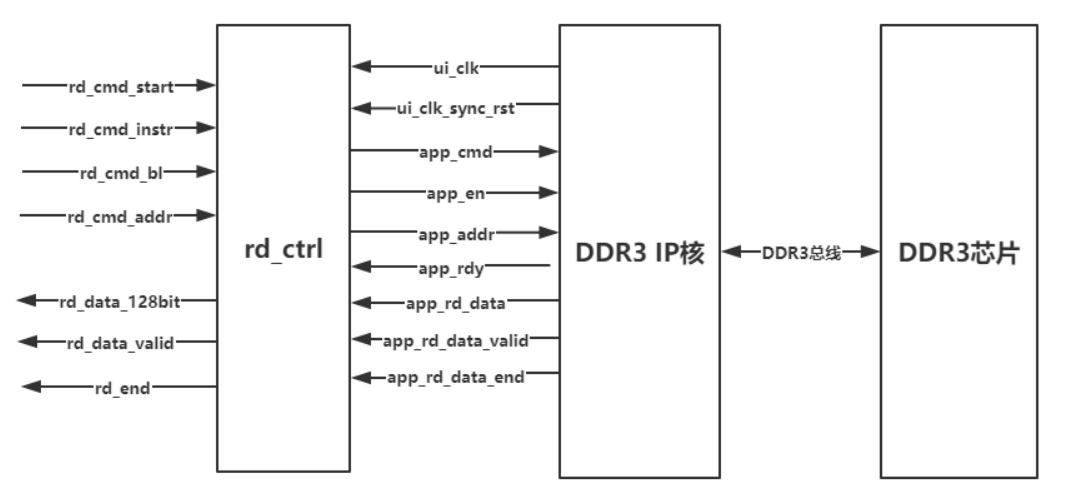

本次设计读控制模块,试着将之前写控制模块的64个128bit数据读回来,并最终进行仿真验证。写控制模块框图如下所示:

当 rd_cmd_start 有效时,启动本次的读突发,根据由外部输入的 rd_cmd_bl 可以确定本次突发需要读多少个数据。wr_cmd_addr 代表本次突发读的起始地址,数据是128bit的,一个地址能存16bit,因此每个128bit数据需要占用8个地址,即每次的地址计数+8。rd_end 用于告知其他模块,本次突发读结束。

本次设计均学自《威三学院FPGA教程》,具体代码就不贴了。

顶层文件不要忘了例化此模块,此外此处设计只考虑读控制,应该把top层中写控制先注释掉,以免两方打架。关于如何复用总线,见下一章:仲裁模块

/*

//写控制模块 ---------------------------------------------------------------

wr_ctrl u_wr_ctrl

(

.sclk (ui_clk ), // input 100Mhz

.rst (ui_clk_sync_rst | (~init_calib_complete)), // input

.wr_cmd_start (wr_cmd_start ), // input

.wr_cmd_instr (wr_cmd_instr ), // input [ 2:0]

.wr_cmd_bl (wr_cmd_bl ), // input [ 6:0]

.wr_cmd_addr (wr_cmd_addr ), // input [27:0]

.wr_cmd_mask (wr_cmd_mask ), // input [15:0]

.data_128bit (data_128bit ), // input [127:0]

.data_req (data_req ), // output

.wr_end (wr_end ), // output

.app_rdy (app_rdy ), // input

.app_wdf_rdy (app_wdf_rdy ), // input

.app_en (app_wr_en ), // output

.app_addr (app_wr_addr ), // output [27:0]

.app_cmd (app_wr_cmd ), // output [ 2:0]

.app_wdf_mask (app_wdf_mask ), // output

.app_wdf_wren (app_wdf_wren ), // output

.app_wdf_data (app_wdf_data ), // output [127:0]

.app_wdf_end (app_wdf_end ) // output

);

*/ //读控制模块 ----------------------------------------------------------------

rd_ctrl u_rd_ctrl

(

.sclk (ui_clk ), // input 100Mhz

.rst (ui_clk_sync_rst | (~init_calib_complete)), // input

.rd_cmd_start (rd_cmd_start ), // input

.rd_cmd_instr (rd_cmd_instr ), // input [ 2:0]

.rd_cmd_bl (rd_cmd_bl ), // input [ 6:0]

.rd_cmd_addr (rd_cmd_addr ), // input [27:0]

.rd_data_128bit (rd_data_128bit ), // output [127:0]

.rd_data_valid (rd_data_valid ), // output

.rd_end (rd_end ), // output

.app_rdy (app_rdy ), // input

.app_en (app_rd_en ), // output

.app_addr (app_rd_addr ), // output [27:0]

.app_cmd (app_rd_cmd ), // output

.app_rd_data (app_rd_data ), // input

.app_rd_data_valid (app_rd_data_valid ), // input

.app_rd_data_end (app_rd_data_end ) // input

);

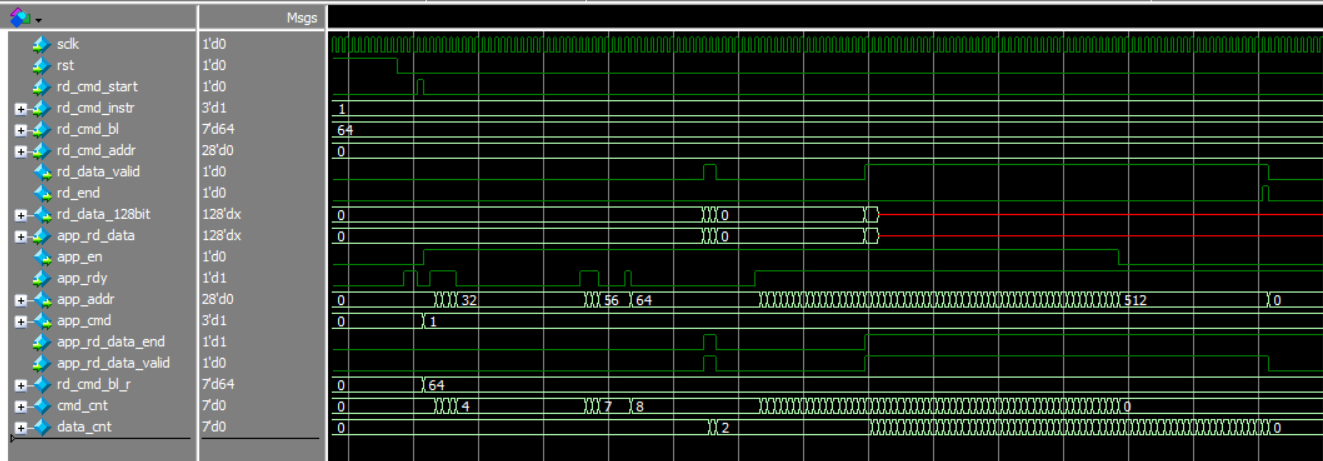

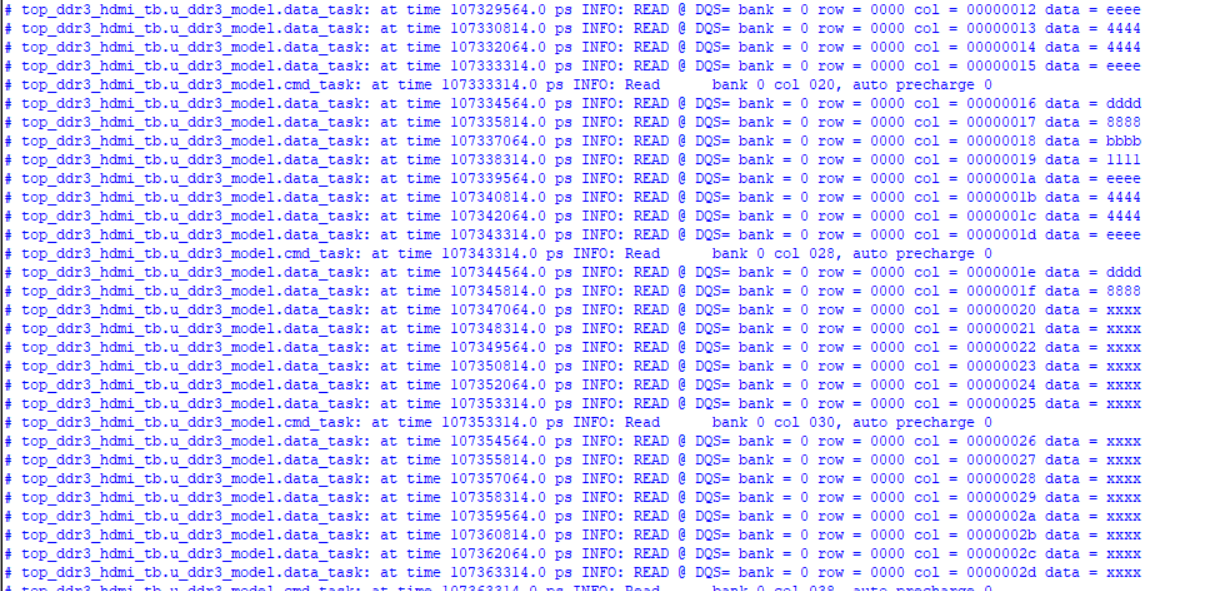

三、读控制模块仿真

可以看到一开始读出的数据是ddr3进行自我校验时残留的数据,后面则都是xxxx,由此看出读控制模块设计大致成功,具体对不对得结合写控制,那就涉及到信号复用了,下章记录仲裁模块解决读写复用问题。

参考资料:威三学院FPGA教程

DDR3(4):读控制的更多相关文章

- 异步fifo with 读控制

之前做LDPC编码器时,学习了一下异步FIFO的相关知识,主要参考了http://www.cnblogs.com/aslmer/p/6114216.html,并在此基础上根据项目需求,添加了一个读控制 ...

- 基于FPGA的DDR3多端口读写存储管理系统设计

基于FPGA的DDR3多端口读写存储管理系统设计 文章出处:电子技术设计 发布时间: 2015/03/12 | 1747 次阅读 每天新产品 时刻新体验专业薄膜开关打样工厂,12小时加急出货 机载 ...

- 基于MIG IP核的DDR3控制器(二)

上一节中,记录到了ddr控制器的整体架构,在本节中,准备把ddr控制器的各个模块完善一下. 可以看到上一节中介绍了DDR控制器的整体架构,因为这几周事情多,又要课设什么的麻烦,今天抽点时间把这个记录完 ...

- M1卡修改各区块控制位值和数据

(一),以常用设置"08 77 8F 69"控制条件为例,先搞清楚它――具有的访问权限. 1.对"08 77 8F 69"值进行计算,该值定位于各区块3的6,7 ...

- 如何读懂 STATSPACK 报告 (转) & Toad 结合

可与 toad 相结合的内容, 用 这种颜色可以利用 toad(database->monitor->server statistics)查看到下边的很多信息, 比如 wait event ...

- M1卡区块控制位详解

M1卡区块控制位详解 Mifare 1S50/Mifare 1S70 每个扇区的密码和存取控制都是独立的,可以根据实际需要设定各自的密码及存取 控制.存取控制为4个字节,共32位,扇区中的每个块(包括 ...

- 如何读懂statspack报告

前言:这篇文章是我从网上找到的,但可惜不知道是哪位大侠写(译)的,因此这里无法注明了.仔细看了看,这篇文章对初学者应该很有帮助,写的比较详细,通俗易懂,因此整理一下,便于阅读:内容略有调整,不单做调整 ...

- am335x 内核频率 ddr3频率 电压调整

由Makefile可知,SPL的入口在u-boot-2011.09-psp04.06.00.08\arch\arm\cpu\armv7\start.S中 SPL的功能无非是设置MPU的Clock.PL ...

- 【等待事件】等待事件系列(3+4)--System IO(控制文件)+日志类等待

[等待事件]等待事件系列(3+4)--System IO(控制文件)+日志类等待 1 BLOG文档结构图 2 前言部分 2.1 导读和注意事项 各位技术爱好者,看完本文后,你可 ...

随机推荐

- CSS 总结 [目录]

一.CSS 基础 1.CSS 初识 2.CSS 用法和特性 二.CSS 选择器 1.基本选择器 2.组合选择器 3.属性选择器 4.伪类选择器 5.伪元素选择器 三.CSS 字体样式 四.CSS 文本 ...

- Caml 多表关联查询

using (SPSite site = new SPSite(SiteUrl)) { using (SPWeb web = site.RootWeb) { SPQuery query = new S ...

- mysql的my.cnf

配置参数详解 [client] #客户端设置,即客户端默认的连接参数port = 3307 #默认连接端口socket = /data/mysqldata/3307/mysql.sock #用于本 ...

- Golang循环中调用go func参数异常分析

项目中,需要循环调用API服务器列表,在循环中使用go func创建协程时遇到了参数失灵的现象. 具体代码如下所示: for _, apiServerAddr := range apiServerAd ...

- svn更换repos时保留svn log

两种情况 1. 直接移动库 问题:svn如何把A服务器上的reposA上传到B服务器的reposB并保留各种上传更新记录? 这个问题要感想敢干,直接复制改名即可 #登录到B服务器 scp -r cmo ...

- Linux操作系统的日志管理之rsyslog实战案例

Linux操作系统的日志管理之rsyslog实战案例 作者:尹正杰 版权声明:原创作品,谢绝转载!否则将追究法律责任. 一.日志介绍 1>.什么是日志 历史事件: 时间,地点,人物,事件 日志级 ...

- piral 基于typescript 的微前端开发框架

piral有一个微前端开发框架,功能强大,文档比较全,扩展能力也比较好 包含以下特性: 特性 高度模块化 多框架兼容 支持资源文件的拆分 全局状态管理 独立开发和部署 CLI工具 与同类框架的比较 参 ...

- three.js 打包为一个组-几个单独的模型

代码: <!DOCTYPE html> <html lang="en"> <head> <title>three.js webgl ...

- Android 开发基础入门篇: 复制一个工程作为一个新的工程

说明 咱们做项目很多时候都需要复制一份工程出来作为一个新的工程 把第一节的工程拷贝到这一节 修改工程名字 打开软件导入此工程 修改包名 第一节的时候说了,一个APP一个包名 自行添加修改 自行修改 自 ...

- [RN] React Native代码转换成微信小程序代码的转换引擎工具

React Native代码转换成微信小程序代码的转换引擎工具 https://github.com/areslabs/alita