nexys4-DDR开发板数码管驱动-第二篇

1. 有这个板子使用的是Artix-7系列的XC7A100T-1CSG324C芯片。作为7系列中的一款FPGA,这个芯片的结构与Kintex-7和Virtex-7几乎一样。也配备了XADC。在Artix-7系列中,100T和200T与其它芯片不同,这两款是ISE与Vivado同时支持的芯片,而更小的35T,50T和75T,ISE的支持会相对差一些。从这个角度说,100T的可玩性比较大。这也是Nexys-4比Avnet Artix-5 50T板子要好一些的地方。

2. 打算用数码管驱动测试一下。打开vivado2014.2软件,创建工程

3. 增加文件,shumaguan.v,代码比较简单。

`timescale 1ns / 1ps

module shumaguan(seg,dig,clock,);

input clock;

output [:] seg; //数码管段码输出

output [:] dig; //数码管位码输出

reg [:] seg; //数码管段码输出寄存器

reg [:] dig; //数码管位码输出寄存器

reg [:] disp_dat; //显示数据寄存器

reg [:] count; //定义计数寄存器

always @ (posedge clock )

begin

count = count + 'b1;

dig= 'b1110;//

end

always @ (count[])

begin

disp_dat = {count[:]};

end

always @ (disp_dat)

begin case (disp_dat)

'h0 : seg = 8'hc0; //显示"0"

'h1 : seg = 8'hf9; //显示"1"

'h2 : seg = 8'ha4; //显示"2"

'h3 : seg = 8'hb0; //显示"3"

'h4 : seg = 8'h99; //显示"4"

'h5 : seg = 8'h92; //显示"5"

'h6 : seg = 8'h82; //显示"6"

'h7 : seg = 8'hf8; //显示"7"

'h8 : seg = 8'h80; //显示"8"

'h9 : seg = 8'h90; //显示"9"

'ha : seg = 8'h88; //显示"a"

'hb : seg = 8'h83; //显示"b"

'hc : seg = 8'hc6; //显示"c"

'hd : seg = 8'ha1; //显示"d"

'he : seg = 8'h86; //显示"e"

'hf : seg = 8'h8e; //显示"f"

endcase

end

endmodule

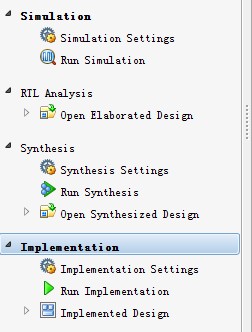

4. 先点击Simulation功能仿真,然后Synthesis综合,综合完之后,在Implementation下面Implemented Design会从灰色切换到可点击状态。

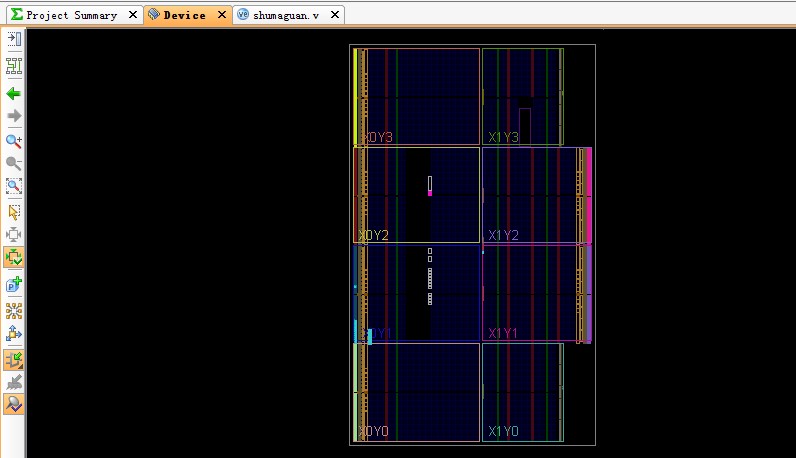

5. 看下器件的内部结构图,大致分为8个区域

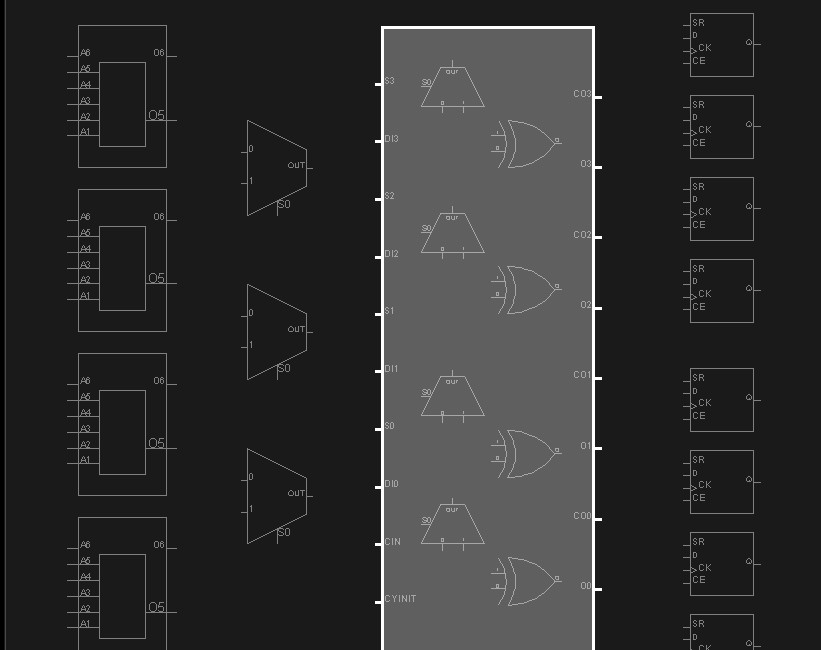

6. 放大看下内的结构,这个有时间要研究下了。感觉是技术核心。

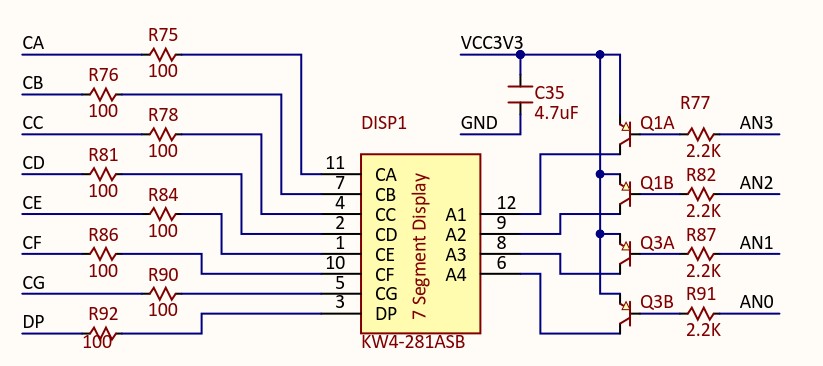

7. 配置引脚,打开I/O Ports这个界面,在site栏选择需要的引脚,电平选择LVCOMS33,看下原理图

8. 看下引脚对应的

## segment display

#NET "ca" LOC=T10 | IOSTANDARD=LVCMOS33; #IO_L24N_T3_A00_D16_14

#NET "cb" LOC=R10 | IOSTANDARD=LVCMOS33; #IO_25_14

#NET "cc" LOC=K16 | IOSTANDARD=LVCMOS33; #IO_25_15

#NET "cd" LOC=K13 | IOSTANDARD=LVCMOS33; #IO_L17P_T2_A26_15

#NET "ce" LOC=P15 | IOSTANDARD=LVCMOS33; #IO_L13P_T2_MRCC_14

#NET "cf" LOC=T11 | IOSTANDARD=LVCMOS33; #IO_L19P_T3_A10_D26_14

#NET "cg" LOC=L18 | IOSTANDARD=LVCMOS33; #IO_L4P_T0_D04_14

#NET "dp" LOC=H15 | IOSTANDARD=LVCMOS33; #IO_L19N_T3_A21_VREF_15 #NET "an<0>" LOC=J17 | IOSTANDARD=LVCMOS33; #IO_L23P_T3_FOE_B_15

#NET "an<1>" LOC=J18 | IOSTANDARD=LVCMOS33; #IO_L23N_T3_FWE_B_15

#NET "an<2>" LOC=T9 | IOSTANDARD=LVCMOS33; #IO_L24P_T3_A01_D17_14

#NET "an<3>" LOC=J14 | IOSTANDARD=LVCMOS33; #IO_L19P_T3_A22_15

#NET "an<4>" LOC=P14 | IOSTANDARD=LVCMOS33; #IO_L8N_T1_D12_14

#NET "an<5>" LOC=T14 | IOSTANDARD=LVCMOS33; #IO_L14P_T2_SRCC_14

#NET "an<6>" LOC=K2 | IOSTANDARD=LVCMOS33; #IO_L23P_T3_35

#NET "an<7>" LOC=U13 | IOSTANDARD=LVCMOS33; #IO_L23N_T3_A02_D18_14

9. 修改I/O Ports,修改完之后,Ctrl+S保存一下,会让保存一个文件,XDC格式的。

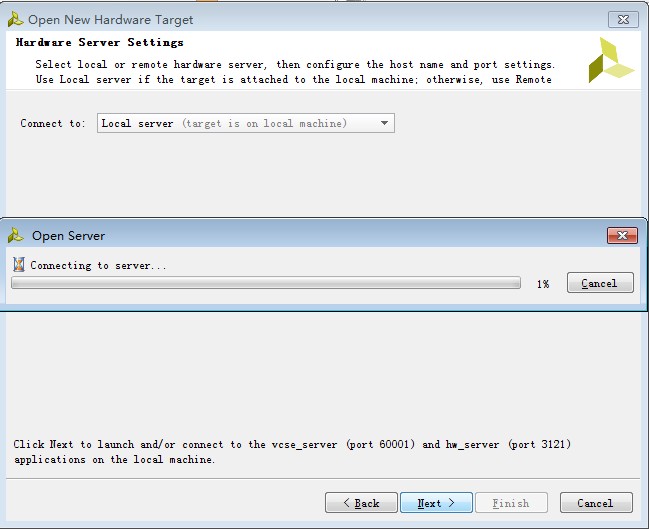

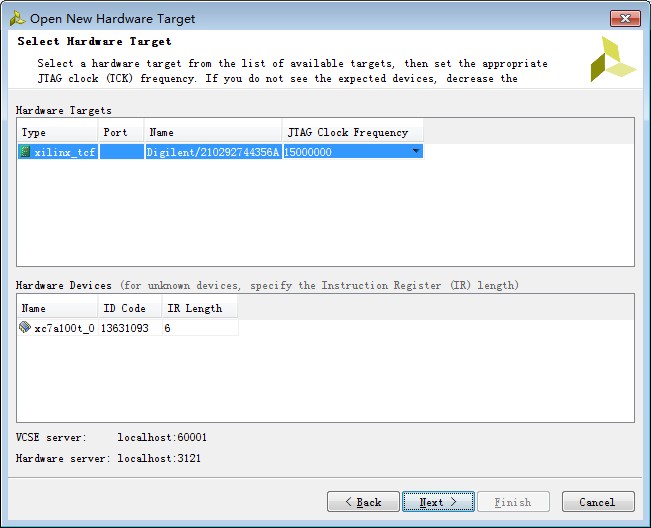

10. 插上板子USB接口J6,等待驱动识别,点击生成二级制文件Generate Bitstream。需要的时间比较久,耐心等待

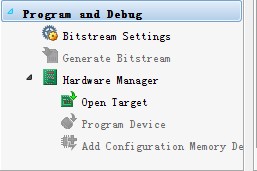

点击Open Target

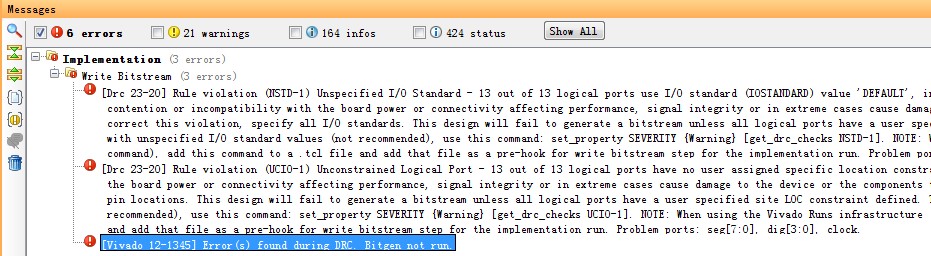

11. 看到到的XADC,是内部的ADC吗?生成2进制文件的时候,遇到一个错误

12. 网上说法是将下面保存成.tcl文件

set_property SEVERITY {Warning} [get_drc_checks NSTD-]

set_property SEVERITY {Warning} [get_drc_checks RTSTAT-]

set_property SEVERITY {Warning} [get_drc_checks UCIO-]

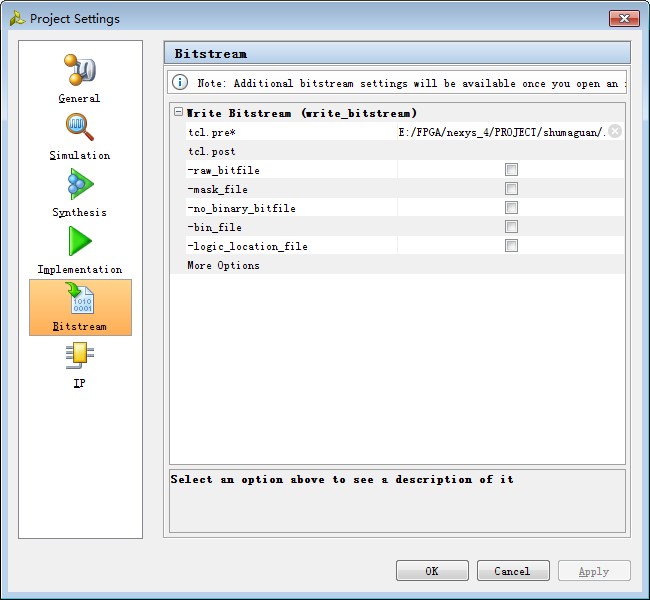

再到bitstream settings做如下设置即可:

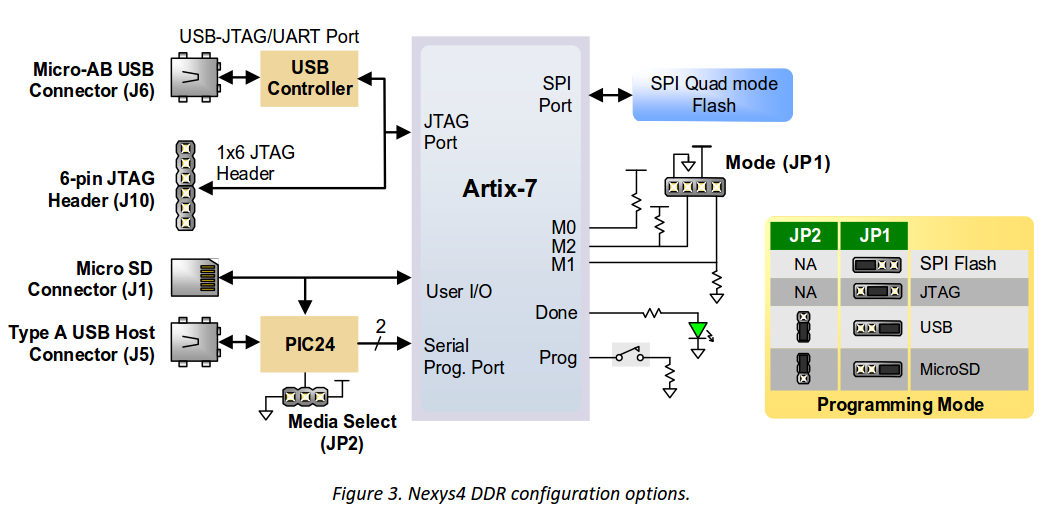

13. 最后Program Devices。不过烧写之后,程序并没有运行,所以我检查了一下,跳线帽,主要是JP1和JP2的选择,本次是用JTAG烧写的,编程烧写成功之后,Done灯会亮,但是不知道亮多久。Prog按键是按下会复位FPGA内部的配置内存,并且按照下图的编程,重新从外置器件读取配置信息到FPGA内部的配置内存。

14. 最后数码管正常运行。

nexys4-DDR开发板数码管驱动-第二篇的更多相关文章

- OK6410开发板系统安装---嵌入式回归第二篇

1. 嵌入式系统须要被安装到开发板的nandflash上 或者 SD卡上 2. 须要安装的嵌入式Linux系统能够分三个部分 watermark/2/text/aHR0cDovL2Jsb2cuY3Nk ...

- 使用wepy开发微信小程序商城第二篇:路由配置和页面结构

使用wepy开发微信小程序商城 第二篇:路由配置和页面结构 前言: 最近公司在做一个微信小程序的项目,用的是类似于vue的wepy框架.我也借此机会学习和实践一下. 小程序官方文档:https://d ...

- 小白自制Linux开发板 七. USB驱动配置

本文章基于https://whycan.com/t_3087.htmlhttps://whycan.com/t_6021.html整理 F1c100s芯片支持USB的OTG模式,也就是可以通过更改Us ...

- JZ2440开发板学习 1. 刚接触开发板, 安装驱动

一. jtag和串口驱动 1. 驱动下载 http://pan.baidu.com/s/1pJkAHJH 2. 驱动安装 禁用win10的驱动数字签名 http://www.100ask.org/bb ...

- iOS开发:深入理解GCD 第二篇(dispatch_group、dispatch_barrier、基于线程安全的多读单写)

Dispatch Group在追加到Dispatch Queue中的多个任务处理完毕之后想执行结束处理,这种需求会经常出现.如果只是使用一个Serial Dispatch Queue(串行队列)时,只 ...

- android系统平台显示驱动开发简要:LCD驱动调试篇『四』

平台信息: 内核:linux3.4.39系统:android4.4 平台:S5P4418(cortex a9) 作者:瘋耔(欢迎转载,请注明作者) 欢迎指正错误,共同学习.共同进步!! 关注博主新浪博 ...

- linux设备驱动第二篇:构造和运行模块

上一篇介绍了Linux驱动的概念,以及linux下设备驱动的基本分类情况及其各个分类的依据和差异,这一篇我们来描述如何写一个类似hello world的简单测试驱动程序.而这个驱动的唯一功能就是输 ...

- LARK BOARD开发板入门学习-第2篇

1. 本次主要研究下HDMI接口,使用芯片是CH7033,这个芯片可以接VGA和HDMI两种接口,和FPGA的接口是地址数据总线 2. 值得注意的地方,下图的D1,双二极管BAT54S在电路中一般用于 ...

- iTOP-4412开发板_驱动_adc驱动升级和测试例程

本文档介绍 iTOP-4412 开发板的 adc 驱动的升级和测试例程.自带的驱动只能支持一路 adc,本文介绍如何修改可以支持 4 路 adc 的控制.1 硬件简介如下图所示,这是 4412 的 d ...

随机推荐

- linux一切皆文件之文件描述符

一.知识准备 1.在linux中,一切皆为文件,所有不同种类的类型都被抽象成文件.如:普通文件.目录.字符设备.块设备.套接字等2.当一个文件被进程打开,就会创建一个文件描述符.这时候,文件的路径就成 ...

- 牛客网多校训练第三场 A - PACM Team(01背包变形 + 记录方案)

链接: https://www.nowcoder.com/acm/contest/141/A 题意: 有n(1≤n≤36)个物品,每个物品有四种代价pi,ai,ci,mi,价值为gi(0≤pi,ai, ...

- VS 2013 代码注释掉,编译不执行问题

先说说我遇到的问题吧.修改别人的代码,注释原来的代码或者添加新的代码,都不执行,还是编译原来的代码.而且还有一个错误:lc.exe 已退出 代码为 -1 解决方法: 1.先把lc.exe 已退出 代码 ...

- 剑指offer 14 调整数组顺序使奇数位于偶数前面

牛客网上的题目还有一个额外的要求,就是不改变数组原始的前后数据,这种可以用队列来存储,或者把前后比较变为相邻的元素比较. 这个题目,主要要考察扩展性,用func函数就实现了扩展性.只需要改func函数 ...

- building for production...Killed

npm run build报错 building for production...Killed 原理 按照他人的说法是,服务器内存不够用了,这样就给他配置一个单独的内存出来就解决了 解决方法 sud ...

- Android 复制 粘贴 剪贴板的使用 ClipboardManager

Copy and Paste 版本:Android 4.0 r1 快速查看 用于复制粘贴数据的基于剪贴板的框架. 同时支持简单和复杂的数据,包括文本串.复杂的数据结构.文本和二进制流数据.程序 as ...

- 【题解】洛谷P2375 [NOI2014] 动物园(KMP)

洛谷P2375:https://www.luogu.org/problemnew/show/P2375 思路 这道题可以说是完全刷新了本蒟蒻对KMP的理解 感觉对next数组的理解上升到一个新的高度 ...

- 一个有意思的CSS样式库--BUTTONS

我最近发现了一个有意思的CSS样式库,和Bootstrap相似,但是它是专门的一个高度可定制的,免费的并且开源的按钮CSS样式库,这里附上它的网址:http://www.bootcss.com/p/b ...

- 轻量ORM-SqlRepoEx (八)MySQL、Sql Service 迁移

数据库变更在编程应用中是常的,MySQL.Sql Service之间的数据迁移更为常见,在 SqlRepoEx2.0DemoForAspCore中演示了,这种数据库之间切换时SqlRepoEx是如何的 ...

- Kadane算法

Kadane算法用于解决连续子数组最大和问题,我们用ci来表示数组a[0...i]的最大和. 观察可以发现当ci-1 < 0时,ci = ai.用e表示以当前为结束的子数组的最大和,以替代数组c ...