Verilog基础入门——Vivado流水灯工程(四)(实验报告)

今日进行了数字逻辑实验,完成了一个最简单的FPGA设计,即流水灯设计。

此处记录我们的指导文件以及实验报告,同时记录遇到的问题及解决方法。

一、vivado工程源文件编写

counter.v文件

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2020/10/08 12:01:18

// Design Name:

// Module Name: counter

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

////////////////////////////////////////////////////////////////////////////////// module counter(

input clk,

input rst,

output clk_bps

);

reg[13:0]cnt_first,cnt_second;

always@(posedge clk or posedge rst)

if(rst)

cnt_first<=14'd0;

else if (cnt_first == 14'd10000)

cnt_first<=14'd0;

else cnt_first <=cnt_first + 1'b1;

always@(posedge clk or posedge rst)

if(rst)

cnt_second <= 14'd0;

else if (cnt_second == 14'd10000)

cnt_second<=14'd0;

else if (cnt_first == 14'd10000)

cnt_second <= cnt_second + 1'b1;

assign clk_bps = cnt_second == 14'd10000 ? 1'b1 : 1'b0;

endmodule

flash_led_ctl.v

`timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////////////// module flash_led_ctl(

input clk,

input rst,

input dir,

input clk_bps,

output reg[15:0]led

);

always @( posedge clk or posedge rst )

if( rst )

led <= 16'h8000;

else

case( dir )

1'b0: //从左向右

if( clk_bps )

if( led != 16'd1 )

led <= led >> 1'b1;

else

led <= 16'h8000;

1'b1: //从右向左

if( clk_bps )

if( led != 16'h8000 )

led <= led << 1'b1;

else

led <= 16'd1;

endcase

endmodule

flash_top_led.v

`timescale 1ns / 1ps module flash_led_top(

input clk,

input rst_n,

input sw0,

output [15:0]led

);

wire clk_bps;

wire rst;

assign rst = ~rst_n; counter counter(

.clk( clk ),

.rst( rst ),

.clk_bps( clk_bps )

);

flash_led_ctl flash_led_ctl(

.clk( clk ),

.rst( rst ),

.dir( sw0 ),

.clk_bps( clk_bps ),

.led( led )

);

endmodule

flash_top_led_tb.v

module flash_led_top_tb;

reg clk,rst,sw0;

wire [15:0] led;

initial begin

clk = 1'b0;

rst = 1'b1;

sw0 = 1'b0;

#10 rst = 1'b0;

#10 rst = 1'b1;

#1000000000 //6ms后改变位移方向

#1000000000

#1000000000

#1000000000

#1000000000

#1000000000

sw0 = 1'b1;

end

always #5 clk <= ~clk;

flash_led_top flash_led_top(

.clk( clk ),

.rst_n( rst ),

.sw0( sw0 ),

.led( led )

);

endmodule

二、工程流程设计

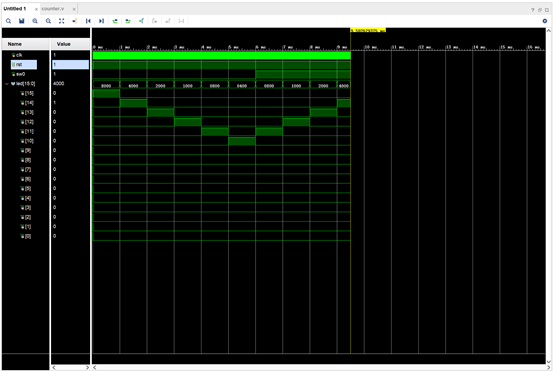

给出流水灯仿真结果截图,对波形进行简要解释:

1、 初始条件下,流水灯从led[15]开始向右移动

2、 6ms后移动至led10亮,改变位移方向向左移动。

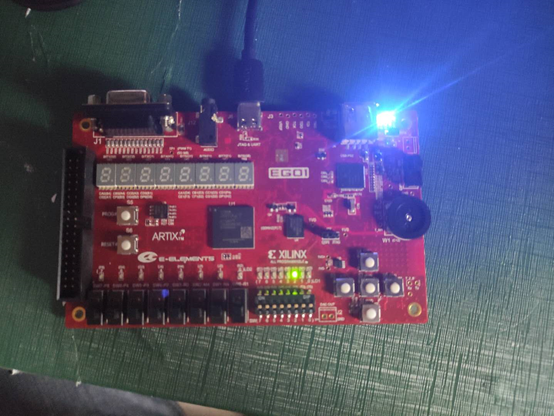

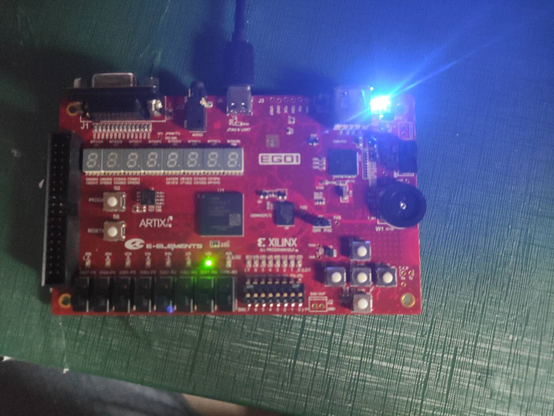

给出板子运行结果照片,以及你的操作过程:

灯向左移动

按下sw0后反向

counter模块的作用是什么?

计时模块

三、实验总结

遇到的问题

1、仿真时波形与预期不相同,排查结果后发现是”Set as top”设置错误。

【在编写源文件的过程中,应该注意到flash_led_top.v文件是应该放到最上方的】

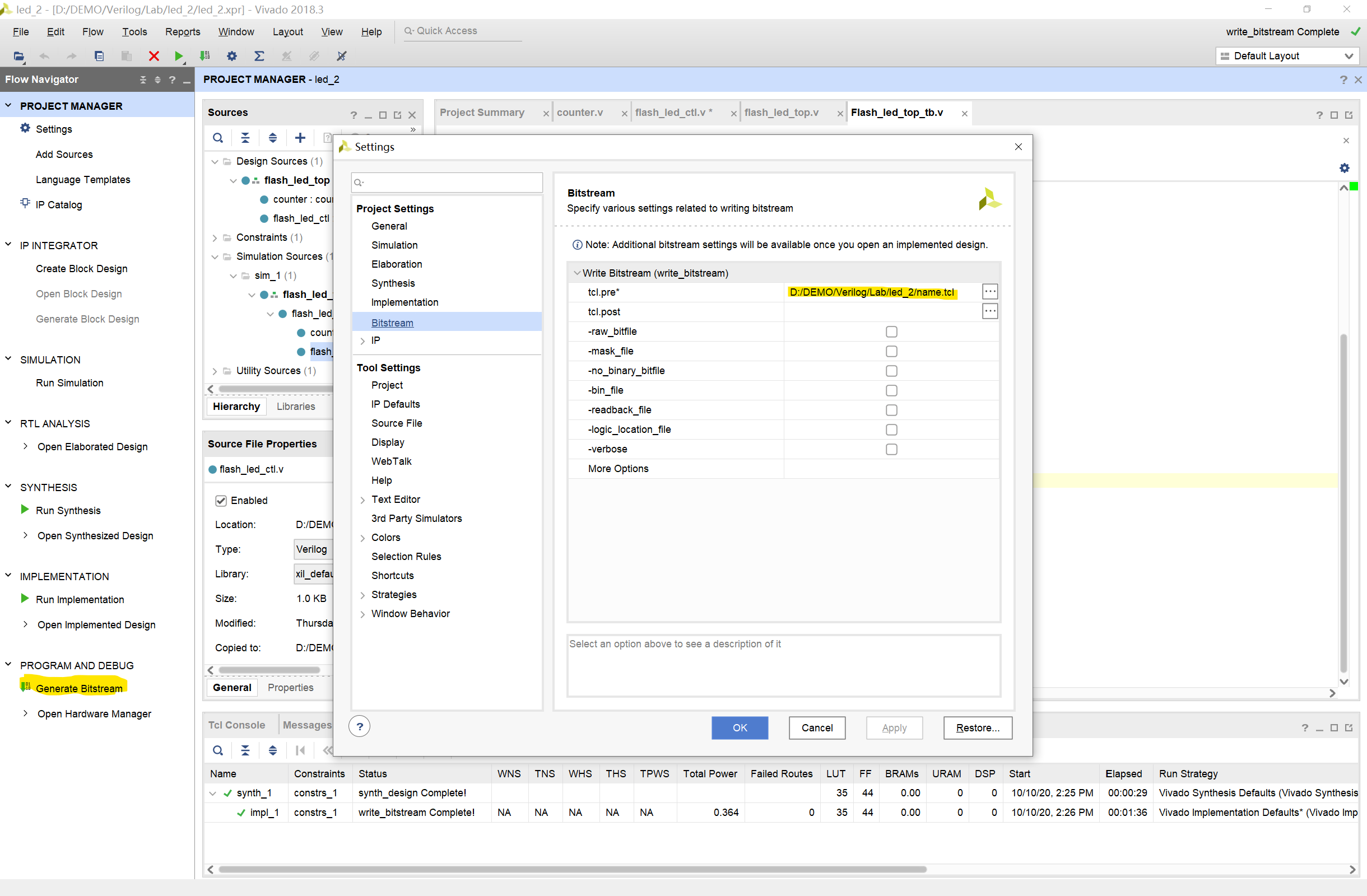

2、无法生成bit流文件,参照csdn上的博客,添加tcl文件代码如下

【set_property

SEVERITY {Warning} [get_drc_checks NSTD-1]

set_property

SEVERITY {Warning} [get_drc_checks UCIO-1]

set_property

SEVERITY {Warning} [get_drc_checks RTSTAT-1]】

右键click左下方的generate bitstream——添加tcl文件。

体会

多查,网上有很多的解决方案,不断排查问题才能得到正确解决方案。

Verilog基础入门——Vivado流水灯工程(四)(实验报告)的更多相关文章

- Verilog基础入门——Vivado工程创建(三)

Verilog基础入门--Vivado工程创建(三) Vivado是Verilog语言的一个集成环境,目前使用的版本为英文版,简单介绍一下在Vivado中创建一个工程并写入源文件 [配置] win10 ...

- 实验四实验报告————Android基础开发

实验四实验报告----Android基础开发 任务一 关于R类 关于apk文件 实验成果 任务二 活动声明周期 实验成果 任务三 关于PendingIntent类 实验成果 任务四 关于布局 实验成果 ...

- 20145120 《Java程序设计》实验四实验报告

20145120 <Java程序设计>实验四实验报告 实验名称:Android开发基础 实验目的与要求: 用SDK成功编译出HelloWorld 实验内容.步骤 PSP 步骤 耗时 百分比 ...

- 20145328 《Java程序设计》实验四实验报告

20145328 <Java程序设计>实验四实验报告 实验名称 Andoid开发基础 实验内容 基于Android Studio开发简单的Android应用并部署测试; 了解Android ...

- 20145227 《Java程序设计》实验四实验报告

20145227 <Java程序设计>实验四实验报告 实验内容 安装Andriod Studio并配置软件 使用Andriod Studio软件实现Hello World的小程序 实验步骤 ...

- 20145315 《Java程序设计》实验四实验报告

20145315 <Java程序设计>实验四实验报告 第一步 安装Android Studio 按教程安装即可,安装过程中需要配置JAVA_HOME环境变量为jdk安装目录. 第二步 在I ...

- # 20155337 《Android程序设计》实验四实验报告

20155337 <Android程序设计>实验四实验报告 实验一 实验内容 Android Stuidio的安装测试: 参考<Java和Android开发学习指南(第二版)(EPU ...

- 20145314郑凯杰 《Java程序设计》实验四 实验报告

20145314郑凯杰 <Java程序设计>实验四 实验报告 实验要求 完成实验.撰写实验报告,实验报告以博客方式发表在博客园,注意实验报告重点是运行结果,遇到的问题(工具查找,安装,使用 ...

- 《Java程序设计》实验四 实验报告

实验四 Android开发基础 实验内容 XP基础 XP核心实践 相关工具 实验要求 1.没有Linux基础的同学建议先学习<Linux基础入门(新版)><Vim编辑器> 课程 ...

随机推荐

- 用Nginx将web请求引导到本机两个tomcat

如何在本机启动两个tomcat请参考:https://www.cnblogs.com/xiandedanteng/p/12100461.html 而Nginx这边,将\conf\nginx.conf ...

- 如何PJ IDEA

1.打开:http://idea.medeming.com/jets/,点击下载PJ码 2.下载完成后解压,会得到2个文件 3.启动IDEA时,将PJ码复制到: 点击ok,就可进入idea中.接着PJ ...

- h5内嵌微信小程序,调用微信支付功能

在小程序中不能使用之前在浏览器中配置的支付功能,只能调用小程序专属的api进行支付. 因为需要在现在实现的基础上,再添加在小程序中调用微信支付功能,所以我的思路是这样的 1.在点击支付按钮时,判断是不 ...

- Java多线程--两个线程同时对一个人的年龄进行增加和修改

public class Thread_A extends Thread { Human human; public Thread_A(String name, Human human) { supe ...

- jmeter做简单的压测

一.JMeter概述jmeter除了可以做借口测试外,还可以做压力测试:首先介绍jmeter中各个组件在压力测试中扮演的角色 1)线程(Threads(Users))即虚拟用户,线程组里可设置需要模拟 ...

- 再学ajax--第二天 | 基于php+mysql+ajax的表单注册、登录、注销

写在前面 ajax学习到了第二天,这次是用第一天封装的ajax函数,后端使用了php+mysql实现基本的注册,登录,注销. php是我前几个月get到的技能,我已经学习到了面向对象,知道各修饰符的含 ...

- ThreadLocal 和神奇的数字 0x61c88647

这篇文章会详细阐述ThreadLocal的内部结构及其原理,以及神奇的0x61c88647 在Java 1.4之前,ThreadLocals会产生线程间的竞争,无法写出高性能的代码. Java 1.5 ...

- pwnable.kr-lotto-witeup

执行分析题目代码,发现是输入值和十进制是1到45的ASCII码系统生成对应字母做比较:而比较方法是遍历输入值的所有位和系统生成字符串的每个位作比较,相同计数为6则爆出flag.漏洞啊,只要押中有一字母 ...

- SON Web Tokens 工具类 [ JwtUtil ]

pom.xml <dependency> <groupId>io.jsonwebtoken</groupId> <artifactId>jjwt< ...

- 项目里出现两个配置类继承WebMvcConfigurationSupport时,为什么只有一个会生效(源码分析)

为什么我们的项目里出现两个配置类继承WebMvcConfigurationSupport时,只有一个会生效.我在网上找了半天都是说结果的,没有人分析源码到底是为啥,博主准备讲解一下,希望可以帮到大家! ...