Clock Domain Crossing

Clock Domain Crossing

CDC问题主要有亚稳态问题,多比特信号同步,握手信号同步,异步Fifo等

Topics

- Describe the SoC Design Issues

- Understand the tranditonal verification limitation

- Know about the CDC Issues

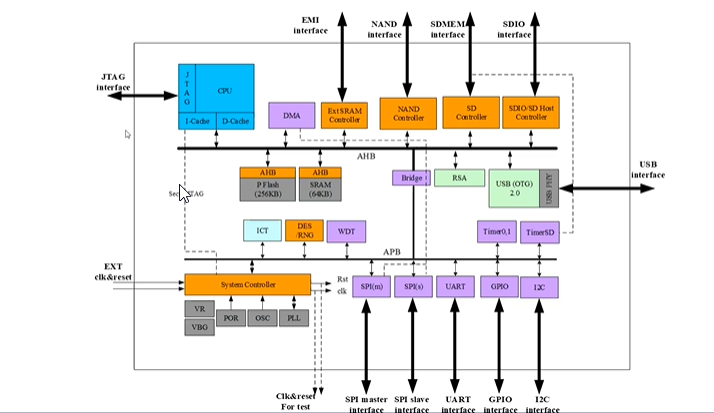

Soc架构

- CPU是整个Soc的大脑,会执行一些指令,这些指令可以控制Soc中的模块,CPU可以给DMA发送指令,还可以给NAND FLASH CONTROLLER发指令....

- CPU有指令的cache(I-Cache),也有数据的Cache(D-Cache),CPU通过JTAG接口与外界连接,进行调试,CPU如果在执行某些代码时出现问题,通过JTAG进行调试

- DMA是一个直接访问的存储器,可以将数据从外存搬移到内存,或者将数据从内部的一个组件搬移到内部的另外一个组件,DMA数据在进行搬移数据的时候,不需要通过CPU进行搬移,可以通过CPU下发一个指令给DMA,DMA进行数据的搬移

- 数据不一定存储在Soc内部,内部的PFLASH,SRAM存储空间都比较小,可以通过外挂存储芯片存储数据,通过控制器来访问外接的存储芯片,比如SRAM芯片和NAND Flash(存储密度更大一些);SD Controller可以访问一些SD卡

- AHB-高速总线,AHB上挂载的都是一些访问速度快的模块,因为要大批量的传输数据

- APB-慢速总线,挂载的模块传输数据量比较小,传输速度慢

- System Controller系统控制器,上电,时钟,复位

- 一个Soc中的模块很多,CPU的工作频率较高,所以时钟域跑的比较快;SPI,UART本身对接的外部接口的变化率比较低,使用CPU的频率去跑,频率大,功耗大,会造成浪费;对于速率要求不高的模块可以降低频率,降低能耗,使用低速总线

- RSA,USB模块有自己的时钟频率

- 不同模块有不同的时钟频率,不同模块之间会有一些交互,所以要解决CDC

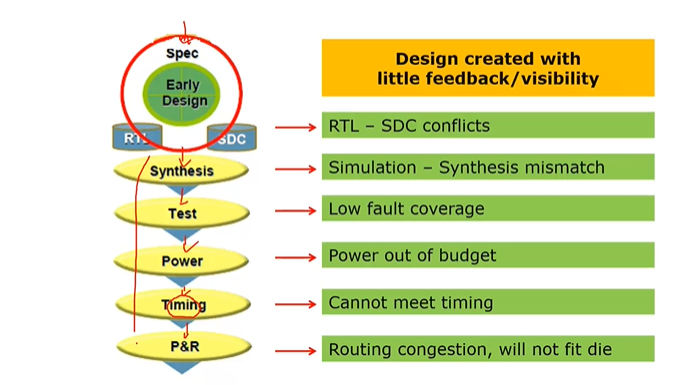

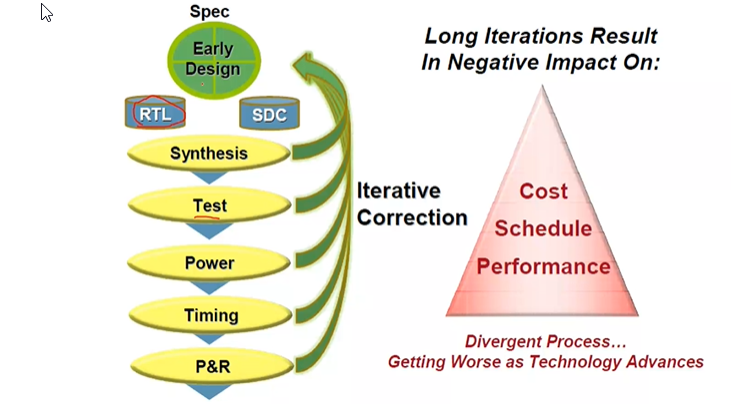

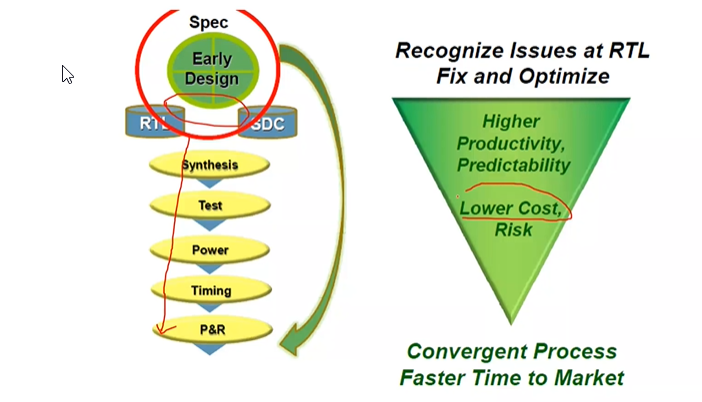

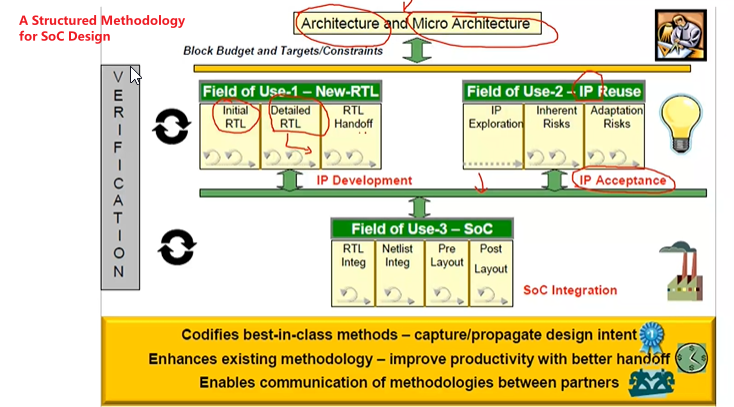

Soc Design Problem

很多问题都需要进行修改RTL或者是Spec,发现问题的时间点越接近前段,成本越低,有没有一种方式可以在写RTL的时候,就可以检查这些问题

SpyGlass 可以在前期检查问题,效果肯定没有实际的pr,timing,power检查准确

不同的IP集成在一起会出现跨时钟域的问题

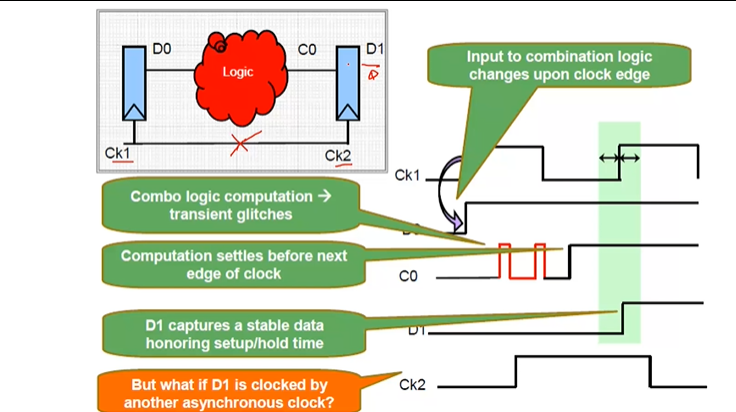

Principle of Synchronous Design

- 上面的设计使用了两个clock,出现跨时钟域的设计,clk1直接连到clk2上就不合理;D0到C0中间经过组合逻辑,会加剧亚稳态的形成

- D0信号是稳定的,经过组合逻辑之后可能在C0会出现毛刺,因为是异步电路,clk2可以在c0端任意时间点内进行采样,这时就有可能会采样到亚稳态

- 如果clk1和clk2是相同的时钟,那么只要保证C0处信号满足在clk2的setup time和hold time就可以,不是产生亚稳态

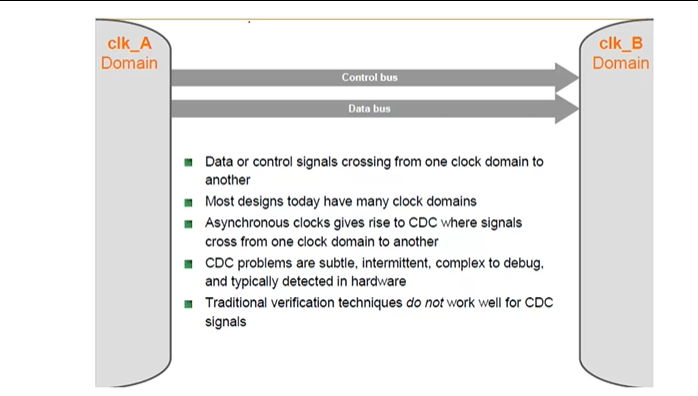

What is a Clock Domain Crossing

- 数据或者控制信号,从一个时钟域跨越到零一个时钟域

- Soc设计有很多时钟域

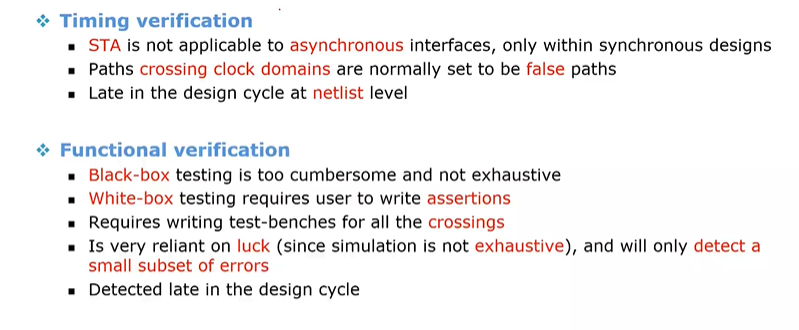

Traditional verification and their Limitation

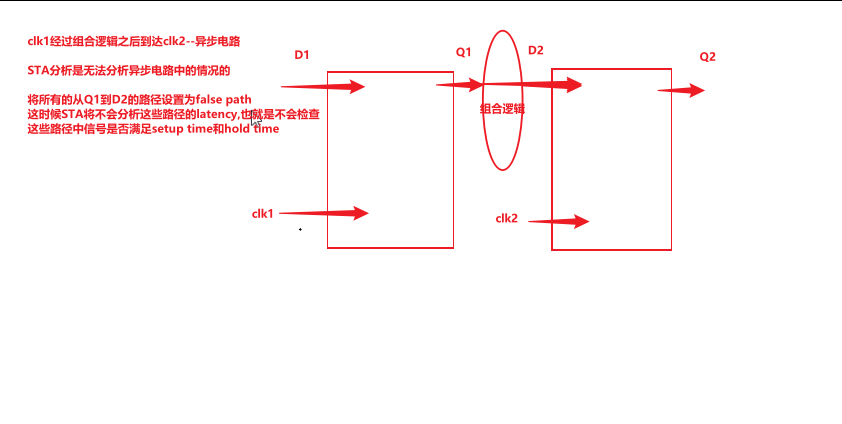

- STA一般进行同步电路的设计进行分析,STA往往是在netlist生成之后进行的时序分析,但是这个时间点晚于RTLcoding时间节点很长时间,出现的时机也不太合适

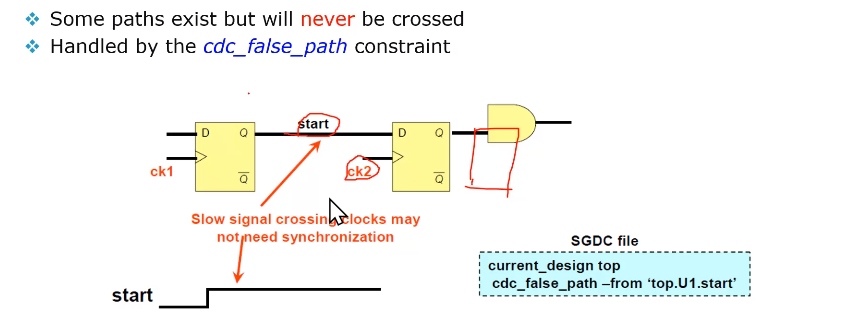

- false path

- 黑盒测试-不关心内部的实现,只关心接口和功能;白盒测试,即关心接口也关心内部的结构,会深入到模块内部进行验证

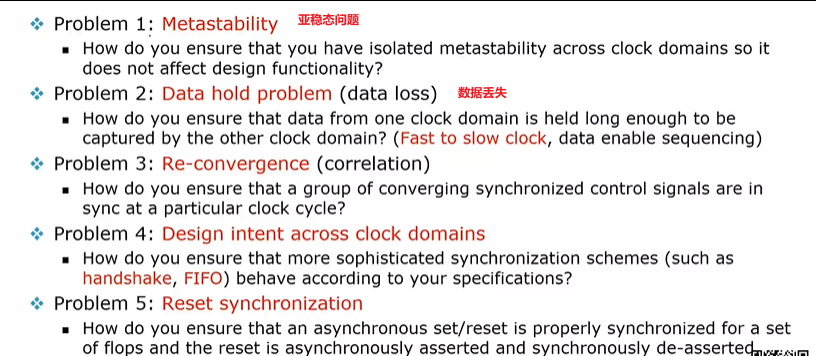

Types of CDC Problems

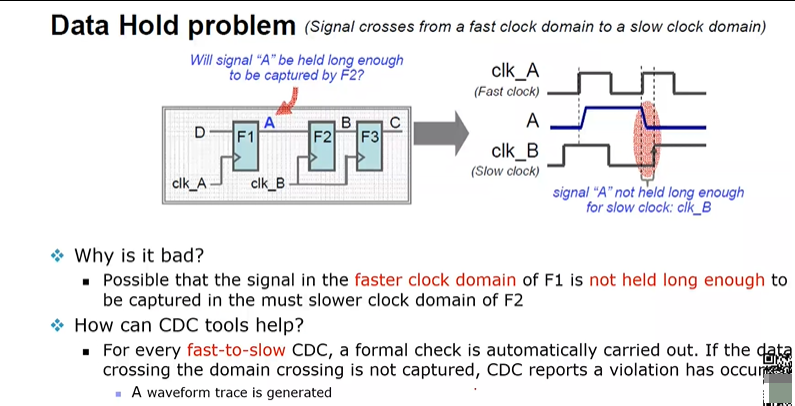

- data hold问题产生数据丢失,就是一个时钟域频率很快(1G),另一个时钟域信号很慢(1M),信号由快时钟域到慢时钟域传递的时候,在时钟上升沿,可能采集不到快时钟的数据

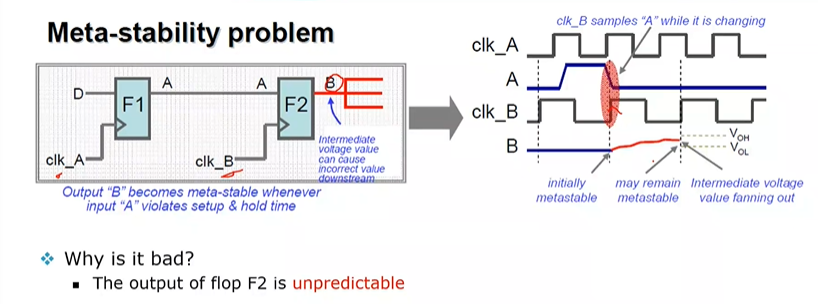

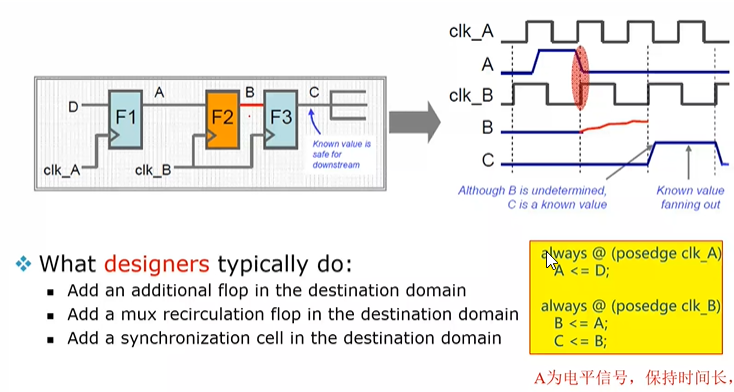

亚稳态问题

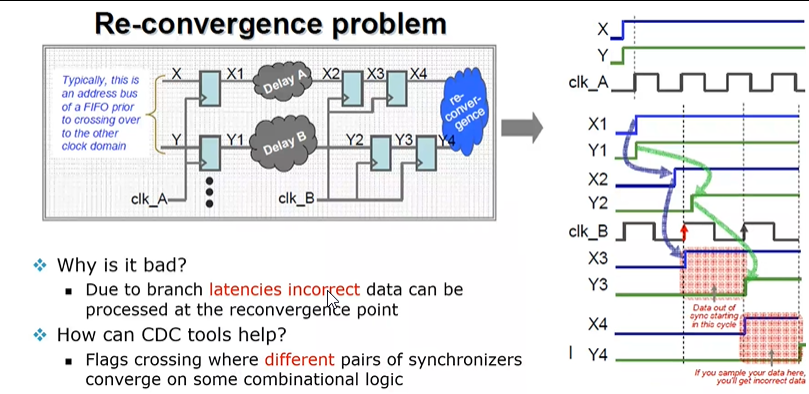

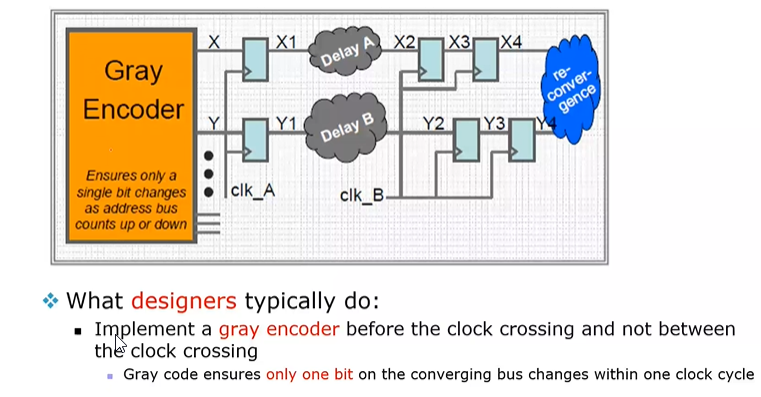

重汇聚问题

- 两个信号分别经过同步器之后,因为同步器导致的latency问题,也会产生亚稳态,CDC工具可以进行检测和解决

- FIFO的地址操作都是加1的操作,使用格雷码进行编码,相邻两个数之间只更改1bit,即使是因为latency的影响,也不会产生新的状态,latency只影响同步时间的早晚

Data hold问题

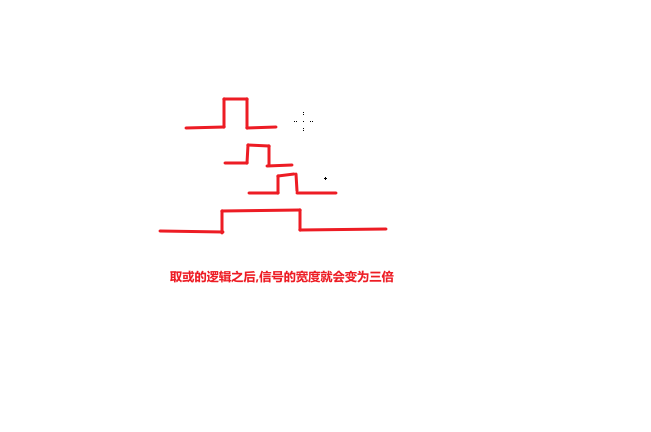

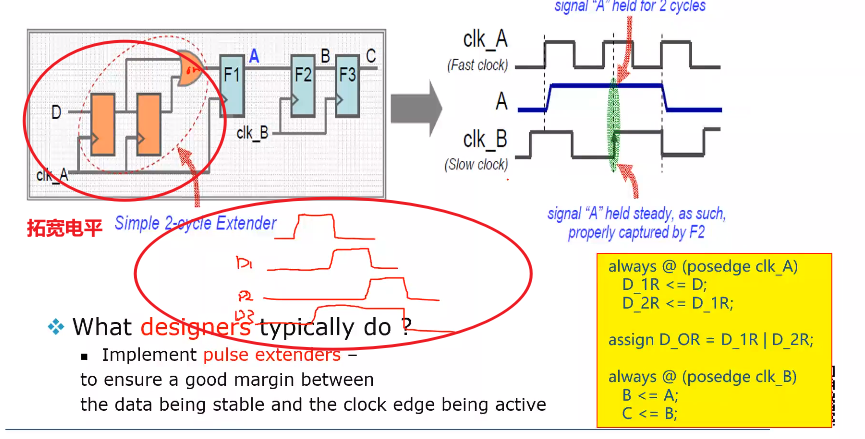

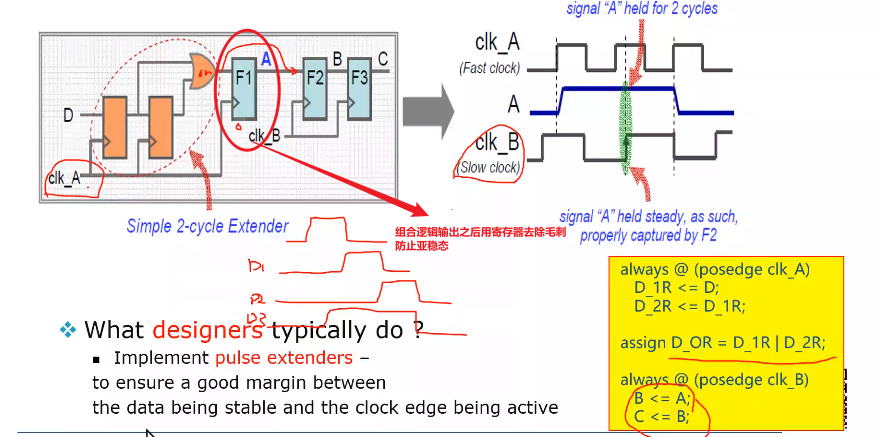

时钟从快时钟域传递到慢时钟域,由于快时钟域信号窄,可能导致数据丢失

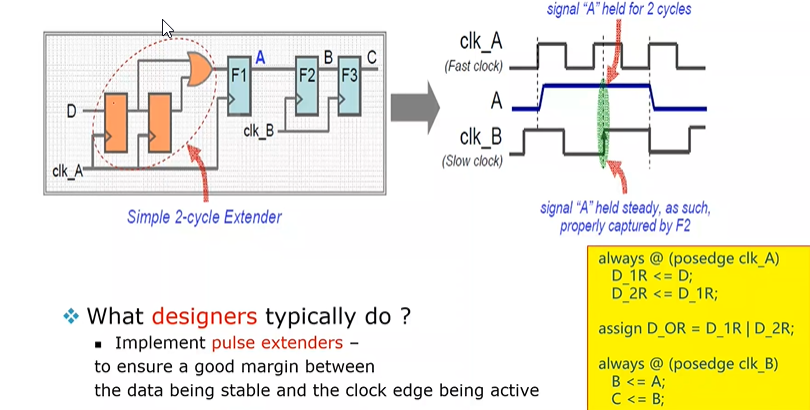

当clkA采样clkB的时候,clkB可能已经为0了,解决方式就是对于快的时钟域进行一个展宽

实现方式:将快时钟经过两个同步寄存器进行打拍之后,使用一个或门将第一级寄存器输出的信号和第二级寄存器输出的信号连接起来,信号拓宽之后,就可以被捕捉到

F1的作用:信号经过组合逻辑之后会出现毛刺现象,为了让信号更加干净,使用一级寄存器将其过滤掉

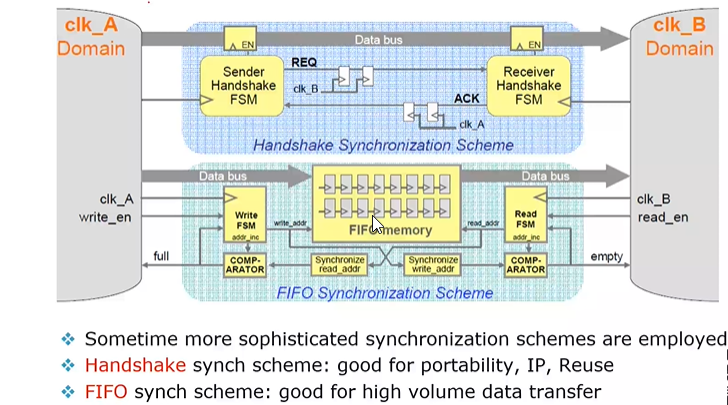

Design Intent(handshake,FIFO)

- 如果传递数据总线data-bus,传递数据,传递的数据之间不是加一和减一的关系,可以使用两种解决方式握手或者是异步FIFO

- 握手:首先数据不经过处理,原数据传递过去,传递的是enable信号;REQ拉高表示data准备好了(数据稳定了),将REQ经过两级打拍器传递到接收端,接收端接收到REQ之后,就可以进行采样数据了;接收端拿到数据之后,还要告诉发送端已经拿到了数据(ACK),发送端拿到ACK信号之后,就可以进行下一组数据的传输

- 握手传递的是1bit信号,优点是面积小,缺点是传递效率不高,传递速度慢

- 异步FIFO:将数据写到FIFO中,将读写指针进行一个同步;优点是性能比较高,缺点是面积较大

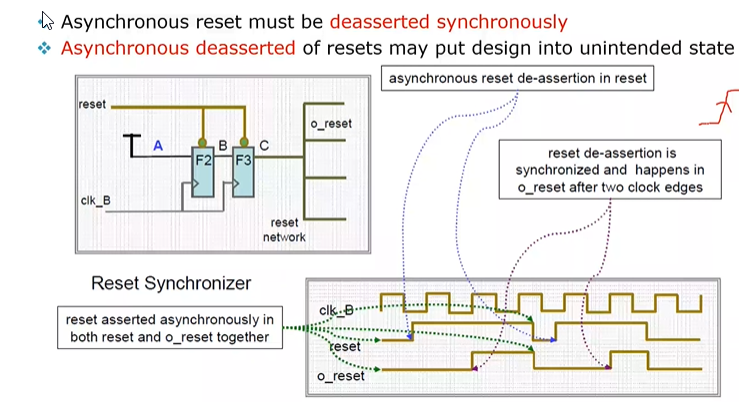

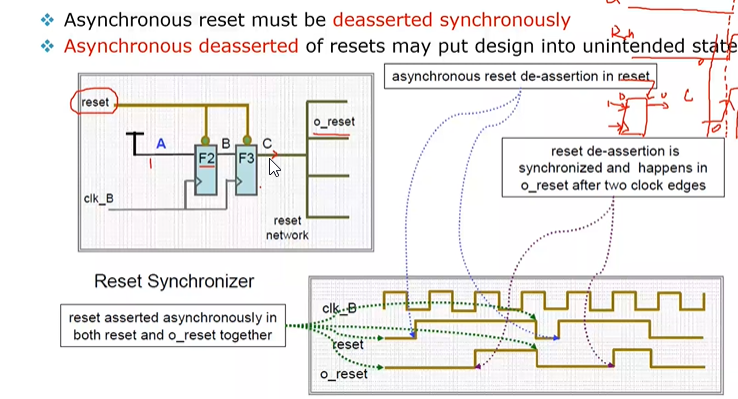

Reset Synchronization

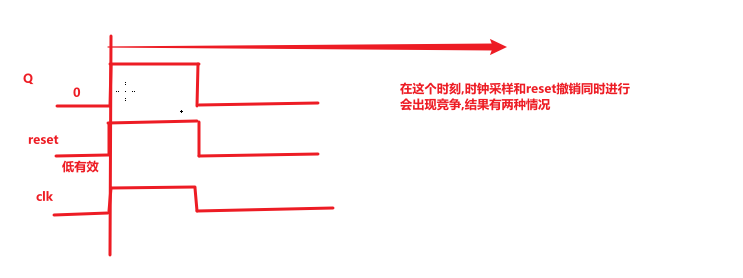

比如时钟是上升沿有效的时钟,假设时钟要去采样一个值,寄存器的输入是1,如果复位信号是低电平有效;在某个时刻,复位信号和时钟同时从0到1跳变,会出现竞争;复位先撤销,时钟先采样再进行复位,Q为1,复位信号撤销的比较晚,就是先复位后采样,Q端为0,出现两种不同的结果(在一个时间点内同时发生,会出现亚稳态)

时钟上升沿之前,复位的撤销需要保持稳定,时钟有效沿之后的一段时间,时钟的复位也需要保持一段时间,类似于setup time和hold time

异步复位:时钟有效沿和reset复位信号是没有关系的

异步复位信号转变为同步复位:就是将reset信号和时钟产生一个相位关系,使用两级寄存器进行同步

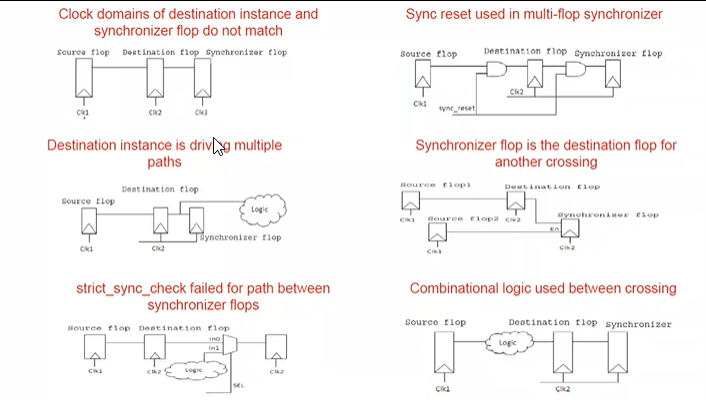

一些问题

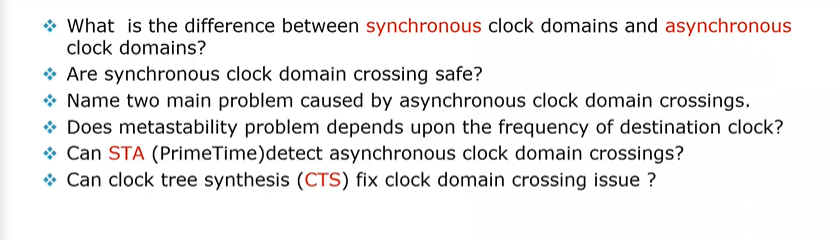

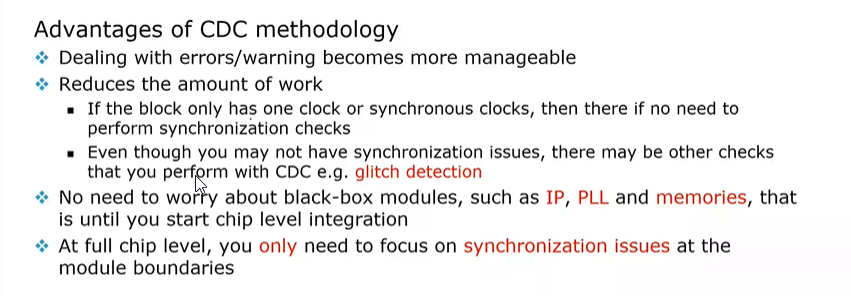

- 同步时钟域(可能不是一个时钟,但是是同源的时钟,频率和相位是有一定关系的)和异步时钟域(时钟频率和相位是没有关系的)

- 同步跨时钟域不一定是安全的,100MHz与50MHz时钟域跨时钟域,会造成数据丢失

- 列举两个CDC问题

- 亚稳态问题是和时钟频率有关的

- STA检查不到CDC问题

- CTS(clock tree sysnthesis)是PR之间的一个过程,是不能解决跨时钟域问题的

- 三个时钟域有问题

- 发射时钟域不能经过组合逻辑,加大亚稳态风险

- 两个时钟域之间重汇聚问题

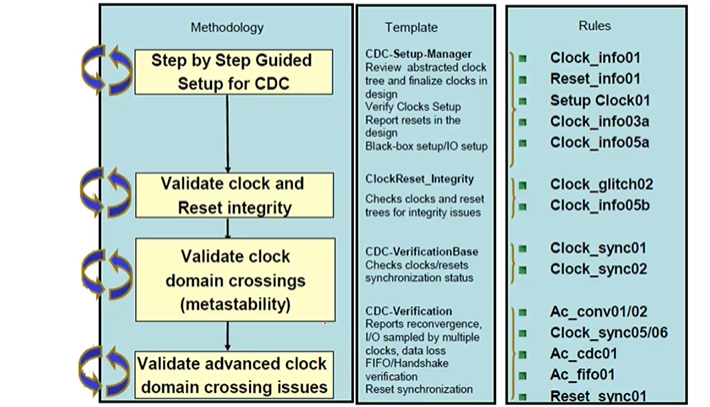

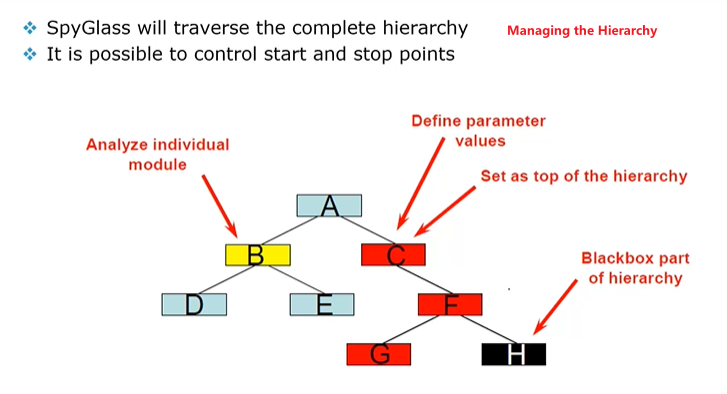

CDC Tool Flow

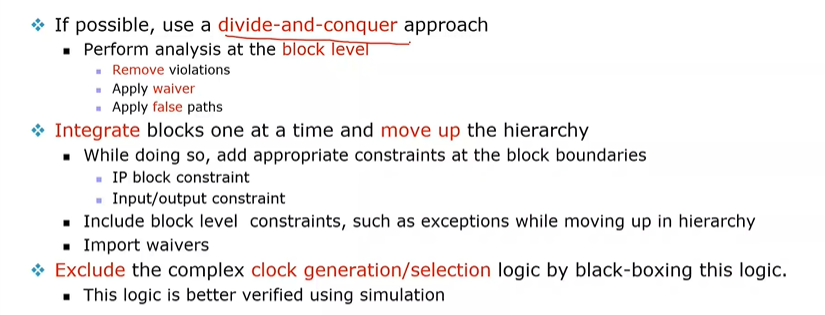

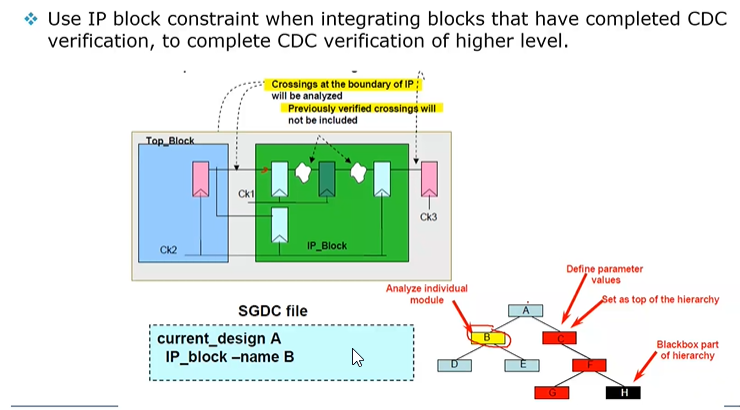

CDC Recommanded Methodology

分治策略,将大模块分为几个小的子模块,先对子模块进行检查

Clock Domain Crossing的更多相关文章

- 跨时钟域设计【一】——Slow to fast clock domain

跨时钟域设计是FPGA设计中经常遇到的问题,特别是对Trigger信号进行同步设计,往往需要把慢时钟域的Trigger信号同步到快时钟域下,下面是我工作中用到的慢时钟域到快时钟域的Verilog HD ...

- 跨时钟域设计【二】——Fast to slow clock domain

跨时钟域设计中,对快时钟域的Trigger信号同步到慢时钟域,可以采用上面的电路实现,Verilog HDL设计如下: // Trigger signal sync, Fast clock dom ...

- AMBA interconnector PL301(一)

HPM(High-Performance Matrix)是一个自生成的AMBA3 bus subsystem. 由一个AXI bus matrix,Frequency Conversion Compo ...

- 7系列FPGA的时钟资源——UG472

时钟架构总览 7系的FPGA使用了专用的全局(Global)和区域(Regional)IO和时钟资源来管理设计中各种的时钟需求.Clock Management Tiles(CMT)提供了时钟合成(C ...

- CDC工具使用

最近一直在搞CDC (clock domain crossing) 方面的事情,现在就CDC的一些知识点进行总结. 做CDC检查使用的是0in工具. 本来要 写一些关于 CDC的 知识点,临时有事,要 ...

- CDC之Metastability

1 CDC A clock domain crossing occurs whenever data is transferred from a flop driven by one clock t ...

- EDA简介

Electronic design automation (EDA), also referred to as electronic computer-aided design (ECAD),[1] ...

- Spyglass CDC工具使用(五)

最近一直在搞CDC (clock domain crossing) 方面的事情,现在就CDC的一些知识点进行总结. 做CDC检查使用的是Spyglass工具.以下内容转载自:Spyglass之CDC检 ...

- Spyglass CDC工具使用(四)

最近一直在搞CDC (clock domain crossing) 方面的事情,现在就CDC的一些知识点进行总结. 做CDC检查使用的是Spyglass工具.以下内容转载自:Spyglass之CDC检 ...

- Spyglass CDC工具使用(三)

最近一直在搞CDC (clock domain crossing) 方面的事情,现在就CDC的一些知识点进行总结. 做CDC检查使用的是Spyglass工具.以下内容转载自:Spyglass之CDC检 ...

随机推荐

- Windows系统修复(System Update Readiness Tool、SFC模式、DISM命令)可解决系统更新问题。

安装System Update Readiness Tool 提供此更新是因为在 Windows servicing store 中发现了不一致,这可能会影响将来成功安装更新.service pack ...

- zabbix-agent报错记录

Too many parameters 由于agent版本差异监控项的参数不一样 , 解决方法升级agent版本 Cannot obtain filesystem information: [2] N ...

- 升级高版本springboot2.6.x:org/springframework/boot/context/properties/ConfigurationBeanFactoryMetadata

升级springboot高版本2.6.x 项目使用到了springcloud的oauth2依赖,直接升级springboot项目版本为最新 2.6.8(2022年6月16日)将会报以下错误: org/ ...

- 2023-09-10:用go语言编写。作为项目经理,你规划了一份需求的技能清单 req_skills, 并打算从备选人员名单 people 中选出些人组成一个「必要团队」 ( 编号为 i 的备选人员

2023-09-10:用go语言编写.作为项目经理,你规划了一份需求的技能清单 req_skills, 并打算从备选人员名单 people 中选出些人组成一个「必要团队」 ( 编号为 i 的备选人员 ...

- 云图说|初识云数据库GaussDB(for Cassandra)

摘要:不用再为数据不一致苦恼,因为强一致的Cassandra来了,DBA们不用加班修数据了.GaussDB(for Cassandra)是一款基于华为自主研发的计算存储分离架构的分布式云数据库服务,是 ...

- 10倍!BoostKit鲲鹏全局缓存3大创新技术助力Ceph性能提升

摘要:本文从四个方面阐述了BoostKit鲲鹏全局缓存技术,该技术针对Ceph开源存储方案存在的痛点,采用三大创新技术,有效的提高了Ceph的性能,最高可以将Ceph性能提升10倍. 本文分享自华为云 ...

- Scrum Master需要具备哪些能力和经验

摘要:ScrumMaster对于产品负责人和开发团队来说,履行的是教练的职责,帮助团队和组织其他成员发展具有组织特色的.高效的Scrum方法,贯彻执行敏捷思想,激励团队持续提升,并不懈追求卓越的表现. ...

- 华为云联合HarmonyOS重磅发布智联生活行业加速器

摘要:华为云DevRun智联生活行业加速器,为产业链上下游企业提供技术支持.生态建设.商业变现等多方面的资源扶持,共同打造智联生活新未来. 据IDC的报告,2021年上半年中国智能家居设备市场出货量约 ...

- GIS常用npm包:GeoJSON文件合并与元素过滤\属性过滤\图形合并

GeoJSON文件合并 普通的geoJSON文件合并,只需geojson-merge插件就够了,https://www.npmjs.com/package/@mapbox/geojson-merge ...

- Google 发布:DevOps 2022现状报告

在过去的八年中,全球超过 33,000 名专业人士参与了Accelerate State of DevOps 调查,使其成为同类研究中规模最大.运行时间最长的一项.Accelerate State o ...