FPGA 原语之一位全加器

FPGA原语之一位全加器

1、实验原理

一位全加器,三个输入,两个输出。进位输出Cout=AB+BC+CA,本位输出S=A异或B异或C。实验中采用三个与门、一个三输入或门(另外一个是两个或门,功能一致)、一个三输入异或门实现该简单功能。

2、实验操作

实验设计还是比较简单的,直接看代码即可:

module test2(

input clk,

input rt_n, input [3:0] key_c,

output [3:0] key_r, output [11:0] led

); wire k1,k2,k3,k4; assign k1=key_c[0];

assign k2=key_c[1];

assign k3=key_c[2];

assign k4=key_c[3]; assign key_r=4'b0; xor xor1(led[0],k1,k2,k3);

and and1(led[11],k1,k2);

and and2(led[10],k2,k3);

and and3(led[9],k3,k1);

or or1(led[8],led[11],led[10]);

or or2(led[2],led[8],led[9]);

or or3(led[3],led[9],led[10],led[11]); endmodule

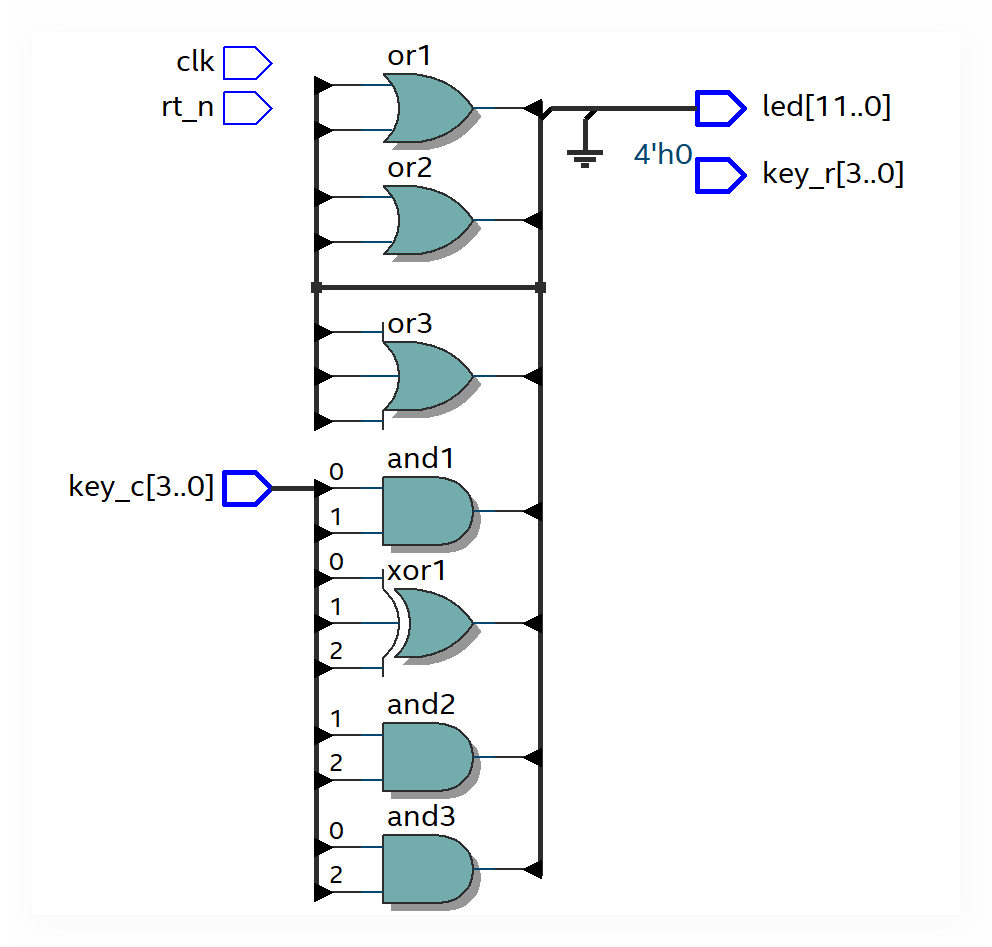

就是直接调用,输出结果直接显示在led上,也就没有区分led,下次可能需要注意一下。生成的RTL视图看不出具体的电路结构,只能看到调用的器件和总线。

3、实验结果

RTL视图

器件的数量和连线基本正确。板级验证就是按相应的输入即可得到具体的输出。这里就不展示了。后面可能验证的就是更加复杂的数字电路。可以将FPGA作为一个可以反复使用的数字电路实验平台。

FPGA 原语之一位全加器的更多相关文章

- 关于FPGA设计16位乘法器的两…

原文地址:关于FPGA设计16位乘法器的两种算法作者:ChrisChan 部分原代码如下: 用特权的右移算法虽复杂点,但节省不少LEs,如下图: 用左移算法尽管浅显易懂,但因每次都会从最右端移位,会占 ...

- FPGA代码一位半加器入门-第2篇

1. 代码比较简单,总结起来是用逻辑运算替代了数学运算加减,应该是因为这样的逻辑资源耗费的少.S是A+B的个位,CO是A+B的进位. module half_adder(A,B,S,CO); inpu ...

- 基于Verilog HDL的超前进位全加器设计

通常我们所使用的加法器一般是串行进位,将从输入的ci逐位进位地传递到最高位的进位输出co,由于电路是有延迟的,这样的长途旅行是需要时间的,所以为了加快加法器的运算,引入了超前进位全加器. 全加器的两个 ...

- 【FPGA学习】Verilog之加法器

在fpga工程应用设计中,随处可见加法器,乘法器等等.现在将一些常用模块和心得体会先记录下来,以便日后使用. 一位半加器: module halfadder(cout,sum,a,b); output ...

- Scheme实现数字电路仿真(2)——原语

版权申明:本文为博主窗户(Colin Cai)原创,欢迎转帖.如要转贴,必须注明原文网址 http://www.cnblogs.com/Colin-Cai/p/12045295.html 作者:窗户 ...

- Verilog学习笔记简单功能实现(二)...............全加器

先以一位全加器为例:Xi.Yi代表两个加数,Cin是地位进位信号,Cout是向高位的进位信号.列表有: Xi Yi Cin Sum Cout 0 0 0 0 0 0 0 1 1 0 ...

- 2.计算机组成-数字逻辑电路 门电路与半加器 异或运算半加器 全加器组成 全加器结构 反馈电路 振荡器 存储 D T 触发器 循环移位 计数器 寄存器 传输门电路 译码器 晶体管 sram rom 微处理 计算机

现代计算机的各个部件到底是如何通过逻辑电路构成的呢 半加器 我们说过了门电路 看似简单的三种门电路却是组成了整个逻辑电路的根基 真值表--其实就是根据输入输出状态枚举罗列出来的所有可能 比如有一台 ...

- verilog之四位全加器的编译及仿真(用开源免费的软件——iverilog+GTKWave)

verilog之四位全加器的编译及仿真(用开源免费的软件——iverilog+GTKWave) 四位全加器的verilog的代码比比皆是,这里上一个比较简单的: /* 4位全加器全加器需要有输入输出, ...

- FPGA之IO信号类型深入理解

在FPGA设计开发中,很多场合会遇到同一根信号既可以是输入信号,又可以是输出信号,即IO类型(Verilog定义成inout). 对于inout型的信号,我们既可以使用FPGA原语来实现,也可以使用V ...

- ModelSim仿真入门

ModelSim仿真入门之一:软件介绍 编写这个教程之前,为了让不同水平阶段的人都能阅读,我尽量做到了零基础入门这个目标,所有的操作步骤都经过缜密的思考,做到了详细再详细的程度. 如果您是FPGA开发 ...

随机推荐

- 【Unity3D】AudioSource组件

1 简介 1)AudioSource 与 AudioListener 简介 AudioSource(音频源)组件用于控制播放 AudioClip(音频片段),能够控制 2D 和 3D(距离越远 ...

- 【Android】Message、Handler、MessageQueue、Looper 详解

1 前言 Handler 即处理器,常用于跨线程通讯:线程A 和线程 B 拥有同一个 handler 对象,在线程 A 中使用 handler 的 sendMessage() 方法发送消息,在线程 ...

- 开年喜报!Walrus成功入选CNCF云原生全景图

近日,数澈软件 Seal (以下简称"Seal")旗下开源应用管理平台 Walrus 成功入选云原生计算基金会全景图(CNCF Landscape)并收录至 "App D ...

- el-upload使用http-request自定义上传和进度条实战

介绍 项目中发现使用默认的el-upload上传动作发送上传请求的时候不会带上请求头,于是想通过自定义请求也就是http-request来自定义上传.实践证明这条路是通的,不过有个小问题就是原本上传的 ...

- 解决:EXP-00003: 未找到段 (0,0) 的存储定义报错

问题说明 DB服务器oracle版本:11.2.0.4.0 最近在客户端用exp命令导出部分表时报错,如题.搜索了一下,找到以下解决方案: 问题原因 Oracle 11g 有一个参数deferred_ ...

- STM32标准库内部Flash读写

STM32标准库FLASH读写 1. STM32内部FLASH介绍 STM32系列一般集成有内部flash,这部分内存可以直接通过指针的形式进行读取.但是由于内部flash一般存储为重要数据或程序运行 ...

- 安卓插耳机也外放扬声器播放音频的java代码

最近遇到一个如何在耳机插入的情况下任然用扬声器播放音频的问题. 用搜索引擎找了一些网上的demo(案例) .发现按照他们的方法成功实现. 插入耳机的时候也可以选择使用扬声器播放音乐,来电铃声就是这么用 ...

- ventoy集成微PE+优启通;vmware虚拟机如何进入PE系统,ventoy启动盘制作。

Ventoy下载地址:Ventoyhttps://www.ventoy.net/cn/index.html 一.Ventoy介绍 Ventoy是一个制作可启动U盘的开源工具.有了Ventoy你就无需反 ...

- offline RL | D4RL:最常用的 offline 数据集之一

pdf:https://arxiv.org/pdf/2004.07219.pdf html:https://ar5iv.labs.arxiv.org/html/2004.07219 GitHub:ht ...

- OPPO 后端面试凉经(附详细参考答案)

这篇文章的问题来源于一个读者之前分享的 OPPO 后端凉经,我对比较典型的一些问题进行了分类并给出了详细的参考答案.希望能对正在参加面试的朋友们能够有点帮助! Java String 为什么是不可变的 ...