k64 datasheet学习笔记52---Universal Asynchronous Receiver/Transmitter (UART)

1.前言

UART实现与外设或CPU的通信

2. UART概述

2.1基本特性

(1)Full-duplex operation

(2)Standard mark/space non-return-to-zero (NRZ) format?

(3)Selectable IrDA 1.4 return-to-zero-inverted (RZI) format with programmable pulse width?

(4)13-bit baud rate selection with /32 fractional divide, based on the module clock frequency

(5)Programmable 8-bit or 9-bit data format

(6)Programmable 1 or 2 stop bits in a data frame.

(7)Separately enabled transmitter and receiver

(8)Programmable transmitter output polarity

(9)Programmable receive input polarity

(10)Up to 16-bit break character transmission.

(11)11-bit break character detection option

(12)Independent FIFO structure for transmit and receive

(13)Two receiver wakeup methods:

Idle line wakeup

Address mark wakeup

(14)Address match feature in the receiver to reduce address mark wakeup ISR overhead?

(15)Ability to select MSB or LSB to be first bit on wire

(16)Hardware flow control support for request to send (RTS) and clear to send (CTS) signals?

(17)Support for ISO 7816 protocol to interface with SIM cards and smart cards

Support for T=0 and T=1 protocols

Automatic retransmission of NACK'd packets with programmable retry threshold

Support for 11 and 12 ETU transfers

Detection of initial packet and automated transfer parameter programming?

Interrupt-driven operation with seven ISO-7816 specific interrupts:

Wait time violated

Character wait time violated

Block wait time violated

Initial frame detected

Transmit error threshold exceeded

Receive error threshold exceeded

Guard time violated

(18)Interrupt-driven operation with 12 flags, not specific to ISO-7816 support

Transmitter data buffer at or below watermark

Transmission complete

Receiver data buffer at or above watermark

Idle receiver input

Receiver data buffer overrun

Receiver data buffer underflow

Transmit data buffer overflow

Noise error

Framing error

Parity error

Active edge on receive pin

LIN break detect

(19)Receiver framing error detection

(20)Hardware parity generation and checking

(21)1/16 bit-time noise detection

(22)DMA interface

2.2 操作模式

- run mode

normal操作模式

- wait mode

UART的操作依赖于C1[UARTSWAI] 域,如果C1[UARTSWAI] 为0则UART正常操作,如果C1[UARTSWAI] 1且CPU在wait mode,UART时钟停止,UART进入低功耗模式

当内部或外部中断唤醒CPU时,会唤醒UART发送或接收

- stop mode

此模式下UART被禁用,当外部中断将CPU退出stop mode时会唤醒UART发送或接收

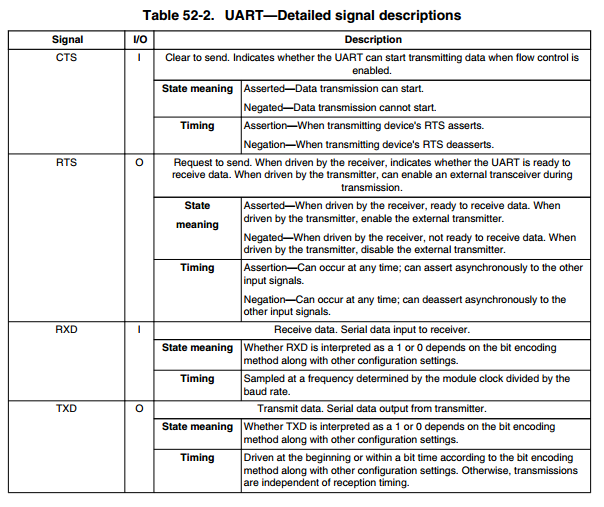

2.3 UART信号描述

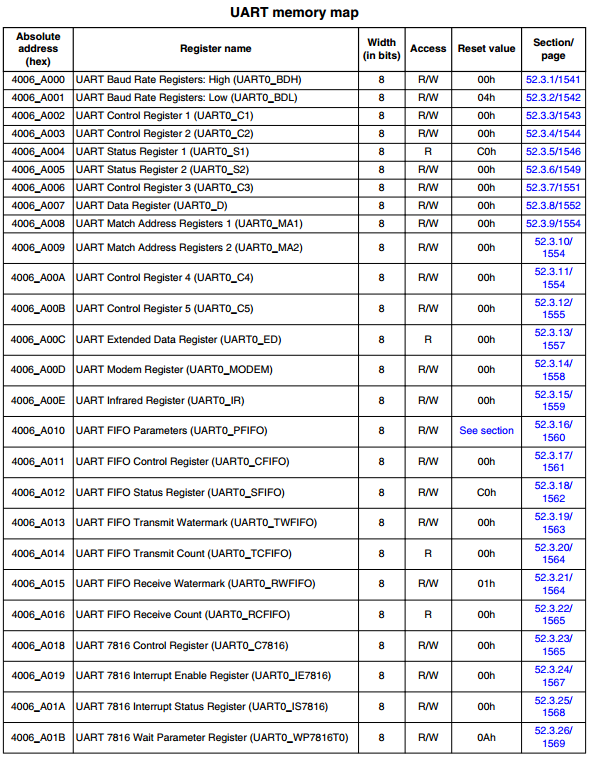

3.Memory map and registers

只支持单字节访问,下面只给出UART0的寄存器:

4.功能描述

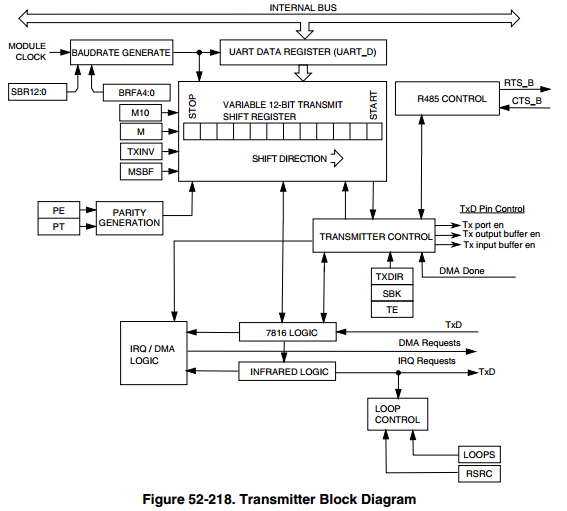

4.1 transmitter

1.支持传输8,9,10数据字符;

2.支持先传输MSB还是LSB可配置;

3.break characters:可以传输break chracters,break chracters包含所有的逻辑0,没有起始、校验位

4.Idle characters: 可以传输idle chracters,idle chracters包含所有的逻辑1,没有起始、校验位

5.Hardware flow control :根据CTS的是否assert来决定是否开启transmitter

6.Transceiver driver enable :??

4.2 receiver

4.3 Baud rate generation

4.4 Data format (non ISO-7816)

4.5 Single-wire operation

4.6 Loop operation

4.7 ISO-7816/smartcard support

4.8 Infrared interface

5.reset

6. System level interrupt sources

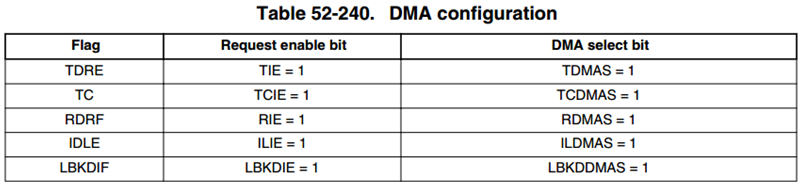

7.DMA operation

在传输时,S1[TDRE] and S1[TC]用来配置为assert一个DMA传输请求;

在接收时,S1[RDRF], S1[IDLE], and S2[LBKDIF]被配置为assert一个DMA传输请求

下面的表显示了DMA请求的相关的flag配置:

当一个flag用来配置为DMA请求,那么如果flag被置位时,与之相连的DMA请求就会assert,直到DMA传输完毕才会deassert DMA请求

8.Application information

k64 datasheet学习笔记52---Universal Asynchronous Receiver/Transmitter (UART)的更多相关文章

- Universal asynchronous receiver transmitter (UART)

UART基本介绍: 通用异步收发器UART他的功能非常强大 我们只使用UART的全双工异步通信功能,使用中断接收数据. UART_RX:串行数据输入. UART_TX:串行数据输出. 硬件支持: 连接 ...

- STM8S——Universal asynchronous receiver transmitter (UART)

UART基本介绍: 通用异步收发器UART他的功能非常强大 我们只使用UART的全双工异步通信功能,使用中断接收数据. UART_RX:串行数据输入. UART_TX:串行数据输出. 硬件支持: 连接 ...

- k64 datasheet学习笔记1---概述

1.前言 k64 datasheet描述了Freescale MCU的特性.架构和编程模型,主要是面向使用MCU的系统架构和软件应用开发人员. 2.模块划分 datasheet主要按功能对模块进行划分 ...

- Universal Asynchronous Receiver/Transmitter

USART簡介與特性 NRZ標準資料格式(Mark/Space) 半雙工/全雙工 Synchronous 同步傳輸 CLOCK SKEW Asynchronous 非同步傳輸 半/全雙工.同步/非同步 ...

- k64 datasheet学习笔记45---10/100-Mbps Ethernet MAC(ENET)之功能描述

1.前言 本文是对K64 datasheet 之ENET部分的功能描述,将对每个部分进行详细说明 2.Ethernet MAC frame formats MAC帧组成格式 (1)7字节前导码:如按最 ...

- k64 datasheet学习笔记3---Chip Configuration之Analog

1.前言 本文主要讲述K64芯片配置,关于模拟部分的内容,主要包括:ADC, CMP, DAC, VREF 2.16bit SAR ADC 从上图可以看出ADC主要挂在外设总线0上,由于ADC的输入引 ...

- k64 datasheet学习笔记21--Direct Memory Access Multiplexer (DMAMUX)

0.前言 本章主要介绍DMA MUX的相关内容 1.简介 1.1 概述 用来路由DMA源到16路DMA通道: 1.2 特性 1.52个外设slot和10个常开slot可以路由到16路DMA通道 2.1 ...

- k64 datasheet学习笔记35---Analog-to-Digital Converter (ADC)

0.前言 本文主要介绍K64的ADC部分的特性,内部架构,信号描述及操作接口等 1.简介 1.1.ADC模块特性 线性逐次逼近算法,达16bit分辨率 达到4对差分和24个单端模拟量输入 输出模式 差 ...

- k64 datasheet学习笔记31---External Bus Interface (FlexBus)

1.前言 FlexBus多功能外部总线接口控制器是一个硬件模块: (1)通过并行总线提供存储器扩展或与外设连接: (2)如下的同步或异步的slave-only设备可以直连到FlexBus总线或者只需增 ...

随机推荐

- Spring_xml和注解混合方式开发

1. spring核心配置文件: <?xml version="1.0" encoding="UTF-8"?> <beans xmlns=&q ...

- nGrinder TestRunner http post json

s nGrinder学习笔记 — post请求 https://blog.csdn.net/meyoung01/article/details/50435881 import HTTPClient.H ...

- Java Web之HTML5

终于学到Java Web这一章节了,首先来了解一下HTML5的一些新知识点吧,我直接贴出HTML5代码看一下: <!DOCTYPE html> <html lang="en ...

- git status -s命令解析

git status -s 以精简的方式显示文件状态. git status 输出的命令很详细,但有些繁琐. 如果用 git status -s 或 git status --short 命令,会得到 ...

- 2018牛客网暑期ACM多校训练营(第九场)A -Circulant Matrix(FWT)

分析 大佬说看样例就像和卷积有关. 把题目化简成a*x=b,这是个xor的FWT. FWT的讲解请看:https://www.cnblogs.com/cjyyb/p/9065615.html 那么要求 ...

- HDU 6375(双端队列 ~)

题意是有至多150000个双端队列,400000次简单操作,直接开会导致内存超限,所以用 STL 中的 map 和 deque ,而读入过大已经在题目中有所说明,直接用已经给出的快速读入即可.要注意的 ...

- Git与GitHub学习笔记(一)如何删除github里面的文件夹?

按照以下步骤即可(本地删除) 1. git pull you git url2. git checkout 3. rm -r dirName4. git add --all5. git commit ...

- IO流--字符流与字节流--File类常用功能

IO流的常用方法: 1: 文件的读取和写入图解: 2:字节流: 读写文件的方法: 一般效率读取: 读取文件: FileInputStream(); 写数据: Fil ...

- windows 使用 php 的exif 问题 Call to undefined function exif_imagetype()

保证 extension=php_mbstring.dll 在 extension=php_exif.dll 之前

- 细说shiro之三:在独立应用中使用shiro

官网:https://shiro.apache.org/ 1. 下载在非Web环境的独立应用中使用Shiro时,只需要shiro-core组件.在Maven项目中的依赖配置如下: <depend ...