USB小白学习之路(12) Cy7c68013A固件之Slave FIFO(转)

Cy7c68013固件之Slave FIFO

转自:http://blog.csdn.net/zengshaoqing/article/details/53053539

选择SlaveFIFO传输方式

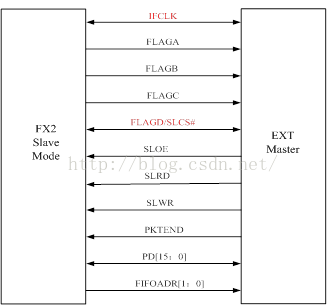

SlaveFIFO传输示意如图1:

图1 Slave FIFO传输示意图

在Slave FIFO方式下,FX2LP内嵌的8051固件的功能只是配置Slave FIFO 相关的寄存器以及控制FX2LP何时工作在Slave FIFO模式下。一旦8051固件将相关的寄存器配置完毕,且使自身工作在SlaveFIFO模式下后,外部逻辑(如FPGA)即可按照SlaveFIFO的传输时序,高速与主机进行通讯,而在通讯过程中不需要8051固件的参与。

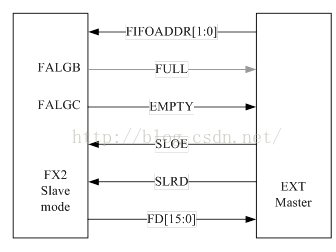

在SlaveFIFO方式下外部逻辑与FX2的连接信号图如图2所示:

图 2 FX2 SlaveFIFO模式端口引脚连接信号

SlaveFIFO传输方式可分为同步和异步两种,由于同步方式对时钟要求严格,故选择异步传输方式。以下为异步SlaveFIFO读写方式:

异步SlaveFIFO读

异步SlaveFIFO读的标准连接图如图3所示:

图 3 异步FIFO读引脚连接

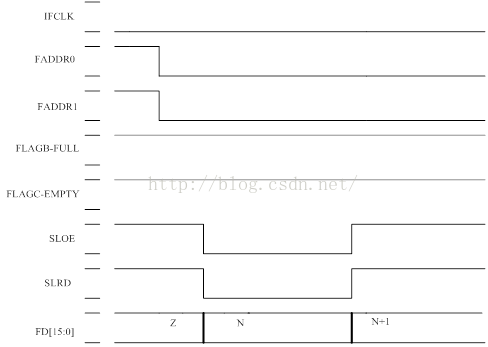

异步Slave FIFO读的标准时序如下:

IDLE:当读事件发生时,进状态1;

状态1:使FIFOADR[1:0]指向OUT FIFO,进状态2;

状态2:如FIFO空,在本状态等待,否则进状态3;

状态3:使SLOE有效,使SLRD有效,从数据线上读数,再使SLRD无效,,以递增FIFO读指针,再使SLOE无效,进状态4;

状态4:如需传输更多的数,进状态2,否则进状态IDLE。

状态跳转示意图如图4:

图 4 异步FIFO读状态跳转

几种情况的时序图示意如图5所示(FULL,EMPTY,SLRD,SLOE均假定低有效):

图 5 异步FIFO读时序

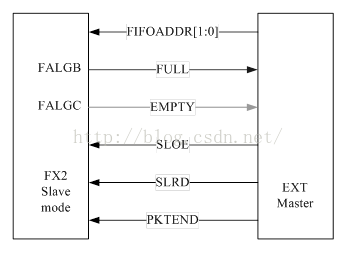

异步Slave FIFO写:

异步Slave FIFO写的标准连接图如图6(其实这个图是有误的,自己看看呗):

图 6 异步FIFO写连接图

异步Slave FIFO写的标准时序如下:

IDLE:当写事件发生时,进状态1;

状态1:使FIFOADR[1:0]指向IN FIFO,进状态2;

状态2:如FIFO满,在本状态等待,否则进状态3;

状态3:驱动数据到数据线上,使SLWR有效,再无效,以使FIFO写指针递增,进状态4;

状态4:如需传输更多的数,进状态2,否则进状态IDLE。

状态跳转示意图如图7(这个图也有错误):

图 7 异步FIFO写状态跳转

几种情况的时序图示意如图8(FULL,EMPTY,SLWR,PKTEND均假定低有效):

图 8 异步FIFO写时序

Slave FIFO模式下常用寄存器

|

IFCONFIG |

接口配置寄存器 |

EPxFIFOPFH/L |

FIFO 可编程PF状态长度 |

||

|

PINFLAGAB |

FLAGx引脚配置 寄存器 |

PORTACFG |

端口A配置 |

||

|

PINFLAGCD |

INPKTEND |

强制结束IN传输寄存器 |

|||

|

FIFORESET |

端点缓冲复位寄存器 |

EPxFLAGIE |

端点FIFO中段 |

||

|

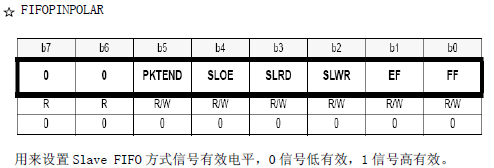

FIFOPINPOLAR |

引脚极性设置寄存器 |

EPxFLAGIRQ |

|||

|

EPxCFG |

端点2/4/6/8配置 |

EPxFIFOBCH:L |

端点FIFO计数 |

||

|

EPxFIFOCFG |

端点FIFO配置 |

EPxFLAGS |

端点状态标志寄存器 |

||

|

EPxAUTOINLENH:L |

端点长度设置 |

EPxFIFOBUF |

端点缓冲寄存器 |

||

编程举例

cy7c68013-56在使用Slave FIFO进行数据传输的时候,默认EP2、EP4作为OUT端点,EP6、EP8作为IN端点。一般要用到FLAGA,FLAGB,FLAGC,FLAGD几个引脚,用于得到端点的状态,寄存器PINFLAGSAB,PINFLAGSCD用于设置这四个引脚的功能。程序举例如下:

PINFLAGSAB =0xe8; // FLAGA - fixed EP2EF(empty flag), FLAGB -fixed EP6FF(full flag)

SYNCDELAY; //FLAGA引脚,EP2空时为0,非空为1,FLAGB引脚,EP6满为0,非满为1。信号有效电平通过FIFOPINPOLAR寄存器设置,0为低有效,1为高有效,默认都为低有效。

PINFLAGSCD =0xac; // FLAGC - fixed EP2FF, FLAGD - fixed EP6EF

SYNCDELAY; //FLAGC引脚,EP2满时为0,非空为1,FLAGD引脚,EP6空为0,非满为1

FIFORESET是用于FIFO状态复位的。复位FIFO如下:

FIFORESET =0x80; // activate NAK-ALL toavoid race conditions

SYNCDELAY; // see TRM section 15.5.4

FIFORESET =0x02; // reset, FIFO 2

SYNCDELAY; //

FIFORESET =0x04; // reset, FIFO 4

SYNCDELAY; //

FIFORESET =0x06; // reset, FIFO 6

SYNCDELAY; //

FIFORESET =0x08; // reset, FIFO 8

SYNCDELAY; //

FIFORESET =0x00; // deactivate NAK-ALL

SYNCDELAY; //

EPxFIFOCFG,用于设置端点的操作方式。

EP2FIFOCFG =0x11; //AUTOOUT="1", WORDWIDE="1"

SYNCDELAY; //自动输出端点,16位数据总线

EP4FIFOCFG =0x11; // AUTOOUT="1",WORDWIDE="1"

SYNCDELAY; //自动输出端点,16位数据总线

EP6FIFOCFG =0x0c; // AUTOIN="1",ZEROLENIN="1", WORDWIDE="1"

SYNCDELAY; //自动输入端点,允许0长度端点,16位数据总线

EP8FIFOCFG =0x0c; // AUTOIN="1",ZEROLENIN="1", WORDWIDE="1"

SYNCDELAY; //自动输入端点,允许0长度端点,16位数据总线

注:其实这里才是最重要的(当然,上面的提到的读写FIFO的状态机也是很不错的):

CY7C68013A的Slave FIFO方式指示引脚的高低有效状态不是固定的,是受寄存器FIFOPINPOLAR的控制的,如图9所示,默认情况下此寄存器的值为0x00:

图 9 FIFIPINPOLAR寄存器

在默认状态下,此寄存器的各位均为0。那就表示信号低有效:

| 位名 | bit = 1‘b1 | bit = 1’b0 |

| SLOE | 禁止读 | 允许读 |

| SLRD | 禁止读 | 允许读 |

| SLWR | 禁止写 | 允许写 |

| EF | FIFO里面有数据,非空 | FIF0 Empty,所有缓冲区均空 |

| FF | FIFO所有的缓冲区还有空间,如果4个缓冲区中的一个缓冲区满,此bit = 1‘b1 | FIFO Full,所有缓冲区均满 |

同理:FIFOPINPOLAR = 0x1F(1'b0001_1111)时的情况,请自行分析。

USB小白学习之路(12) Cy7c68013A固件之Slave FIFO(转)的更多相关文章

- USB小白学习之路(10) CY7C68013A Slave FIFO模式下的标志位(转)

转自良子:http://www.eefocus.com/liangziusb/blog/12-11/288618_bdaf9.html CY7C68013含有4个大端点,可以用来处理数据量较大的传输, ...

- USB小白学习之路(8)FX2LP cy7c68013A——Slave FIFO 与FPGA通信(转)

此博客转自CSDN:http://blog.csdn.net/xx116213/article/details/50535682 这个博客只对自己理解CY7C68013的配置有一定的帮助,对于配置CY ...

- USB小白学习之路(11) Cy7c68013A驱动电路设计注意事项(转)

Cy7c68013A驱动电路设计注意事项 转自:http://group.chinaaet.com/116/79029#0-tsina-1-71467-397232819ff9a47a7b7e80a4 ...

- USB小白学习之路(1) Cypress固件架构解析

Cypress固件架构彻底解析及USB枚举 1. RAM的区别 56pin或者100pin的cy7c68013A,只有内部RAM,不支持外部RAM 128pin的cy7c68013A在pin脚EA=0 ...

- USB小白学习之路(6) IIC EEPROM读取解析

IIC EEPROM读取解析 1. 编译错误处理(这里可以忽略) 在解压包解压了程序后,直接编译,出现如下错误. *** WARNING L14: INCOMPATIBLE MEMORY MODEL ...

- USB小白学习之路(3) 通过自定义请求存取外部RAM

通过自定义请求存取外部RAM 1. 实验简述 此实验是对自定义的供应商特殊命令(vendor specific command bRequest = 0xA3)进行解析,程序中的read me说明如下 ...

- USB小白学习之路(5) HID鼠标程序

HID鼠标程序 1. 特别注意 需要特别注意,各个例程中的设备描述符,配置描述符等各种描述符都是已经配置好了的,我们需要做的只是在例程中将代码修改为自己需要的部分即可,一般情况下是不可以串搭配的. 2 ...

- USB小白学习之路(4)HID键盘程序

HID键盘程序 1. 特别注意 需要特别注意,各个例程中的设备描述符,配置描述符等各种描述符都是已经配置好了的,我们需要做的只是在例程中将代码修改为自己需要的部分即可,一般情况下是不可以串搭配的. 2 ...

- USB小白学习之路(2)端点IN/OUT互换

端点2(out)和端点6(in)的out_in互换 注:这里的out和in都是以host为标准说的,out是host的out,在设备(Cy7c68013)这里其实是输入端口:in是host的in,在设 ...

随机推荐

- ZZJ_淘淘商城项目:day04(淘淘商城03 - 前台系统搭建、实现、内容管理系统实现)

1. 今日大纲 1. 实现商品的编辑 2. 实现商品的规格参数功能 3. 搭建前台系统 4. 实现首页商品类目的显示 2.2.4. 未实现TODO 编辑时图片回显: 思路: 1. 查 ...

- UML-业务规则

样例:

- Django路由层与视图层

表与表之间建关系 图书管理系统为例 书籍表 出版社表 作者表 三个表之间的关系: 考虑表之间的关系:换位思考 1.书籍和出版社是一对多,外键字段建立在书籍表中 2.书籍和作者是多对多, 需要建立第三方 ...

- CI_CD(jenkins)公司实战_未完成版

环境准备 #三台服务器,不同的ip centos 镜像时:CentOS Linux release 7.6.1810 (Core) gitlab-ce 版本是:11.11.3 jenkins ...

- 05 - Tomcat 线程池的配置与优化

添加 Executor 在server.xml中的Service节点里面,增加executor节点,然后配置connector的executor属性,如下: <Executor name=&qu ...

- Codeforces Round #572 (Div. 1) 差E

Codeforces Round #572 (Div. 1) A2 题意:给一棵树,带边权,互不相同且为偶数.每次操作是选两个叶子然后在路径上同时加一个数.初始边权全是0,求一个操作序列使得最终边权与 ...

- StartDT AI Lab | 视觉智能引擎+数据决策引擎——打造商业“智能沙盘”

众所周知,线上商家可以通过淘宝平台的大量前端“埋点”轻松获取商品的加购率.收藏率.转化率.成交额等大量基础信息,甚至商家能够在更精细的层面,获取商品关键字变化或者上新/爆款带来的流量变化数据,更甚者商 ...

- GIL锁和进程/线程池

GIL锁 1.GIL锁 全局解释器锁,就是一个把互斥锁,将并发变成串行,同一时刻只能有一个线程使用共享资源,牺牲效率,保证数据安全,也让程序员避免自己一个个加锁,减轻开发负担 带来的问题 感觉单核处理 ...

- mysql数据库-索引-长期维护

############### 索引介绍 ############## """ 1. 索引介绍 需求: 一般的应用系统,读写比例在10:1左右,而且插入操作和 ...

- Block to|wreck|Range|Reach|span|chase around|amuse|exploit |instructed

English note: Block to 纷涌而至 destroy多指彻底地.毁灭性地破坏,含导致无用,不能或很难再修复的意味. wreck侧重指船只.车辆.房屋等受到严重破坏或完全毁坏,也可指计 ...