STA之OCV

Timing sign-off Corner = library PVT +RC Corner + OCV

针对每个工艺结点,foundry都会给出一张类似的timing sign-off表格,定义了所有需要做timing sign-off的corner(实际需要sign-off的corner还需要乘以工作模式,对于STA,不同的工作模式,用不同的SDC文件予以区别)

uncertainty=clock jitter + Xps setup/hold margin + DPT,其中clock jitter由用户根据所用PLL的精度来确定;Xps由foundry提供,如:30ps for setup, 40ps for hold; DPT一项表示需要加的额外margin用于cover mask misalignment引起的偏差,该值亦由foundary提供,比如5ps for setup, 3ps for hold。

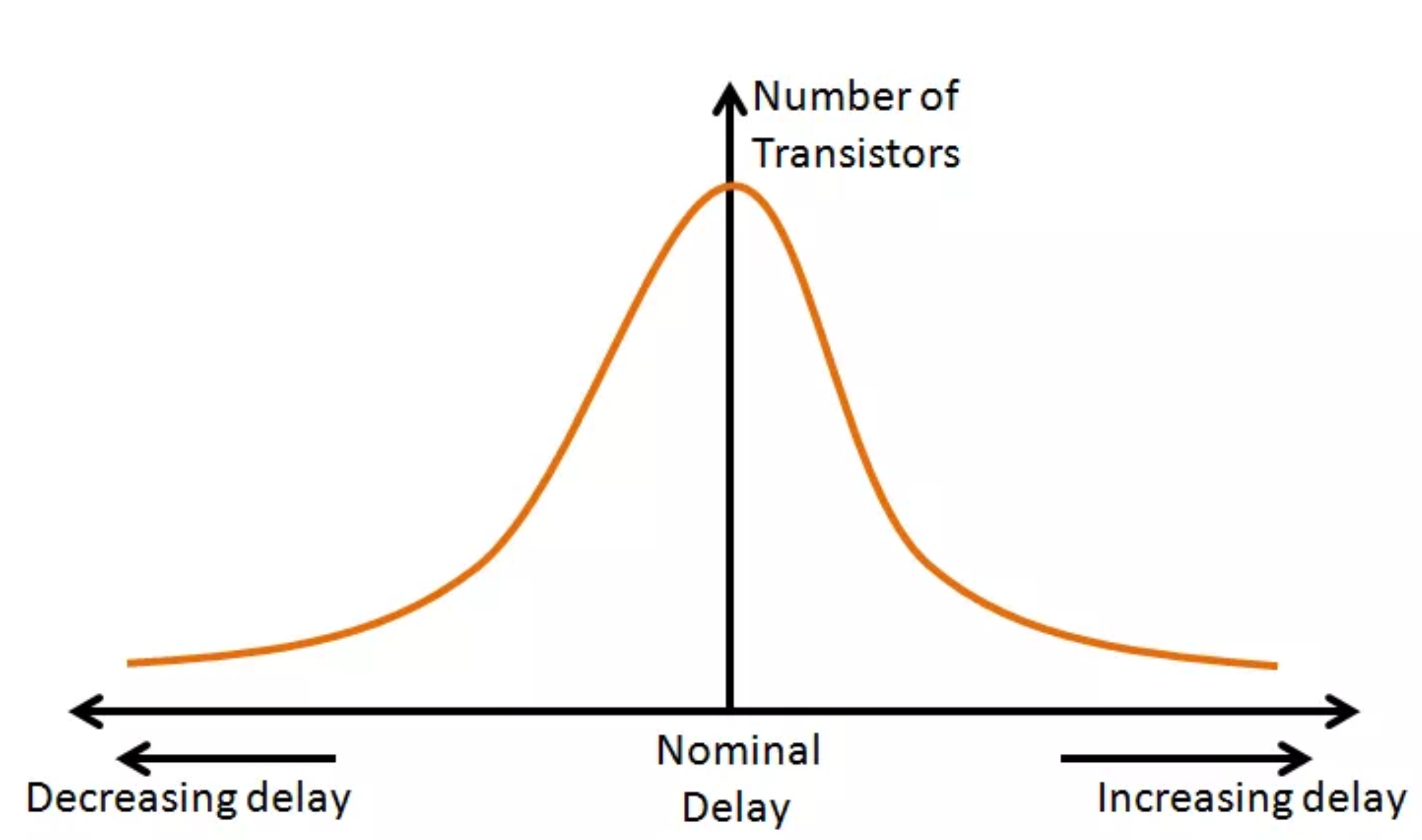

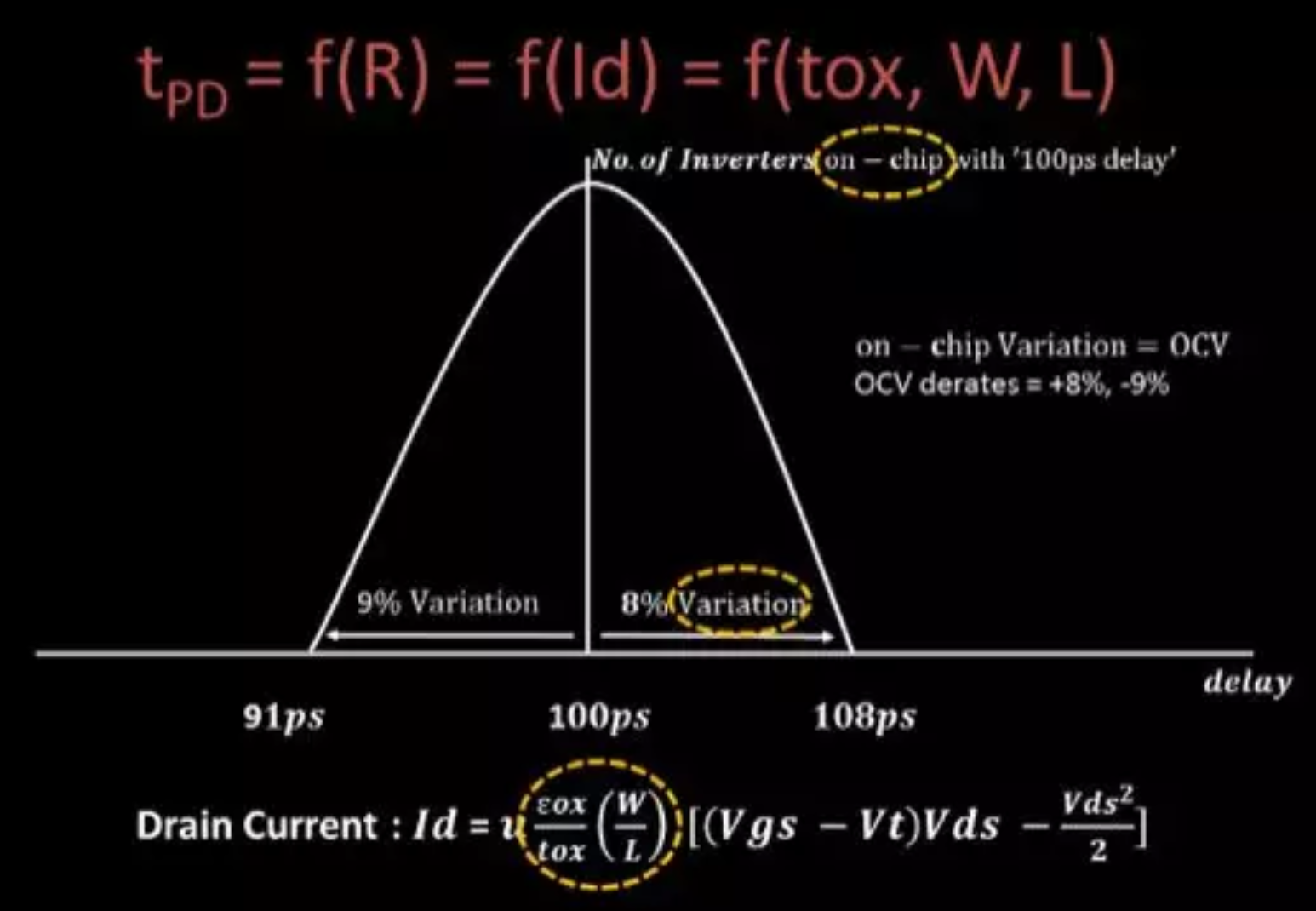

世界上没有两片相同的叶子,半导体世界里没有两只相同的管子。library中的cell delay是在某个固定的PVT(operating condition)下仿真得出的,也就是下图中的Nominal delay,而实际上在芯片内部由于工艺偏差、电压降、温度变化,cell的delay并不是一个固定值,而是一个随机值,遵循高斯分布或门特卡洛分布。

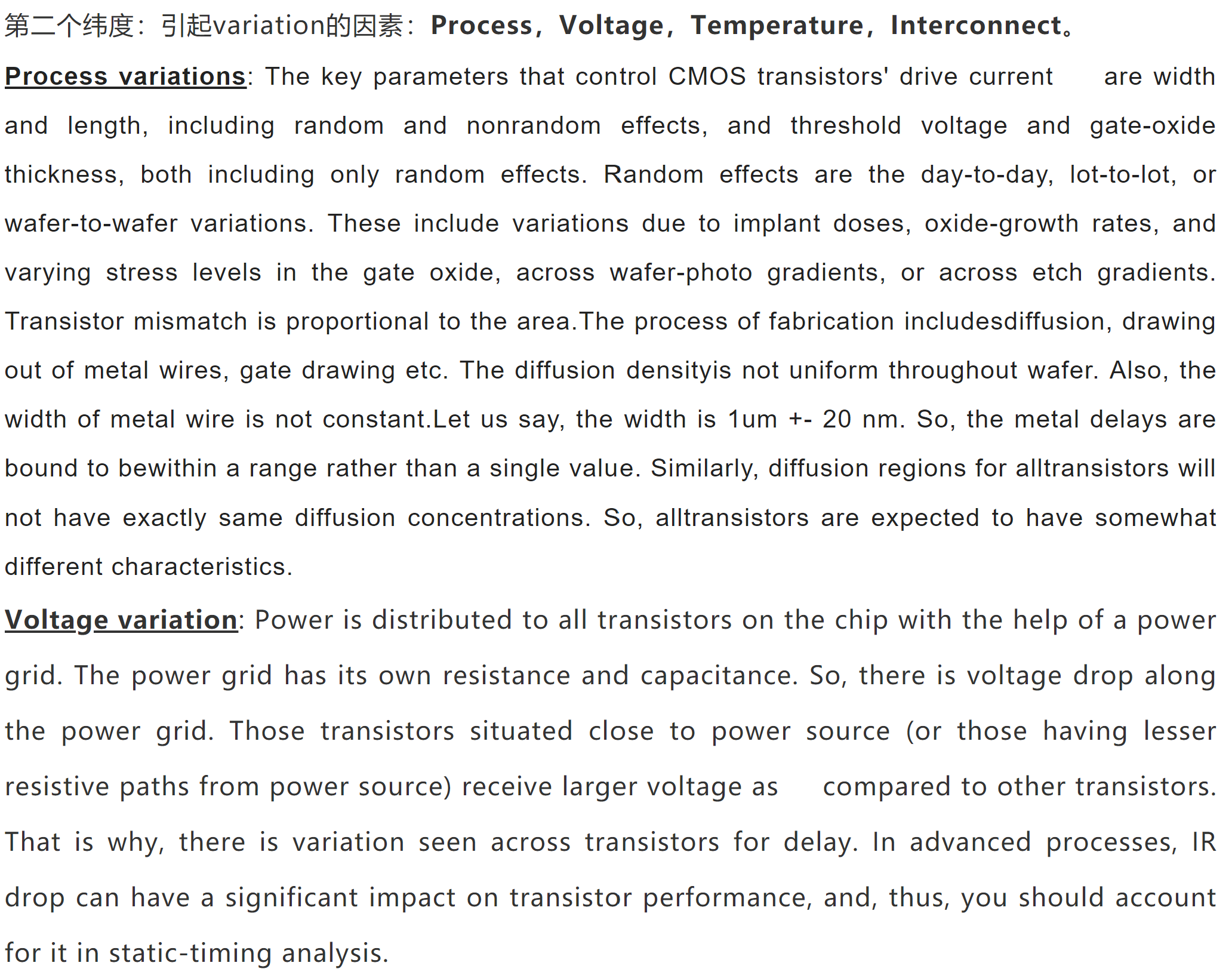

在STA中用OCV来模拟这一『特征』,OCV全称on chip variation,用于描述不同管子间由于工艺偏差、电压降、温度变化引起的delay变化,也用于描述工艺偏差引起的net厚度宽度的变化从而导致net的电容电阻变化。

PVT跟OCV都是用于描述Process、Voltage、Temperature对timing的影响,两者有何区别?

PVT:主要取决于外部因素,在某一固定的工艺点、芯片的工作电压、周围环境温度对芯片性能的影响。更直白的理解:同一颗芯片在不同工作电压、环境温度下的性能表现。

OCV:用于模拟芯片内部不同管子由于工艺偏差、电压降、温度变化引起的性能变化,这种变化更宏观的表现是:不同芯片在相同PVT下的性能表现不同。

在timing sign-off时,为什么要在Nominal delay上加OCV?

因为Nominal delay是在固定PVT下仿真得出的delay,而实际上由于OCV的影响,管子的delay是呈高斯分布或门特卡洛分布,要想保证yield,就必须在timing sign-off时将OCV考虑在内,以保证大部分管子都可以满足时序要求。对每一代工艺,foundry都会做大量测试,针对每个corner找到一组适合的OCV值,这组值可以保证足够高的yield,而如果进一步加紧这个值,并不会更有效的提高yield。在SOCV/POCV里的多少sigma(如:3-sigma)的选取也是出于相同的考虑

Interconnect variation: Another area of on-chip variation is in interconnect height and width, resulting in variation in both resistance and capacitance. Because the delay from interconnect is becoming more dominant as geometries shrink, you should pay attention to accurate modeling of interconnect variations. Two potential sources of this variation are the CMP (chemical-mechanical-planarization) process and the proximity effects in the photolithography and etch processes. Variation in the CMP process results from the difference in hardness between the interconnect material and the dielectric. Ideally, after the designer has etched trenches into the dielectric below an interconnect layer and copper on the wafer, the CMP process removes the unwanted copper, leaving only lines and vias. The copper line is softer than the dielectric material, resulting in "dishing" and erosion, which cause uneven removal of the copper and dielectric. Dishing is a function of line width and density, and erosion is a function of line space and density. Another source of variation in thickness due to CMP is a morerandom variation resulting in a gradient across the wafer. You can see thisgradient in die-to-die variations and even across-die variations for large die.You would ideally model this random, nondeterministic variation statistically.However, if you can obtain process data to model this variation, then you canmodel it deterministically as a function of position on the wafer. In thisscenario, you give an adder or subtracter, depending on the x,y position on thedie, to the RC value. Etch-proximity effects appear as "microloading," whichmeans that the etch process overetches isolated lines. A dual-damascenestructure uses only a single metal-deposition step to simultaneously form themain metal lines and the metal in the vias. That is, the formation of both thetrenches and the vias occurs in one dielectric layer. Overetching results in awider trench and, hence, a wider metal line. Photolithographic effects also cause problems. Diffraction andlocal scattering in photolithography may overexpose densely spaced lines andunderexpose isolated lines. Tiling and metal slotting reduce the variation infeature density and mitigate these effects. Tiling algorithms give differentresults, but a general rule states that a less dense gradient yields smallerline-width variations on the die. Tiling does have its drawbacks, however. Asone of the last integration steps in an SOC-design flow, tiling involvescalculations that the extractor performs using density parameters. Thesecalculations can result in different RC values before and after tiling. Tilingcan also result in small additional delay effects on timing. The final designmay not meet the desired target frequency once you account for tiling. Whetherit does depends largely on the design and the methods you use to meet thetiling requirements.

方法学上概念清晰了之后,EDA工具端的操作就十分简单了,在EDA工具中如何设置OCV?每家工具都有各自不同的命令/变量控制,跟OCV相关的大致可分为四部分,此处以Tempus的命令为例:

全局控制:set_analysis_mode -analysisType onChipVariation

设置OCV:set_timing_derate -cell_delay/net_delay/cell_check -late/early -data/clock (1-d%);其中d%是foundry在sign-off表格中给出的OCV值

Report OCV: report_statistical_timing_derate_factors

Debug timing时在timing report中将derate列显示出来:set_global report_timing_format {instance arc delay slew arrival user_derate}

由于工艺的进步,flat OCV在先进工艺如16,7中已经逐步被AOCV, SOCV/POCV取代,以剔除悲观度。

STA之OCV的更多相关文章

- STA之PVT

在STA星球,用library PVT.RC corner跟OCV来模拟这些不可控的随机因素.在每个工艺结点,通过大量的建模跟实测,针对每个具体的工艺,foundary厂都会提供一张推荐的timing ...

- 论STA | 工艺、工具、分析的本与末

人类从漫长的蒙昧中觉醒之后,不再依靠着奇装异服的巫师通灵来指导生活,巫师进化成了科学家,他们试图对周遭的一切进行概括.分类.抽象,于是有了化学.物理.数学等基科.比如一粒沙,它的化学组成是什么,物理特 ...

- 论STA | SOCV / POCV 之 variation (2)

芯片制造涉及到许多复杂重复的过程,如:光刻.蚀刻.离子注入.扩散.退火.而且都是原子级操作,尽管控制非常严格,但偏差不可避免. 工艺偏差会导致芯片物理参数偏差,如:线宽.沟道掺杂浓度.线厚.临界尺寸. ...

- STA之AOCV

为什么要引入AOCV 为了精确性,为了剔除悲观度.用set_timing_derate来设置OCV,对于一个固定的corner,只能对data/clock, cell/net, late/early分 ...

- 选择目录,选择文件夹的COM组件问题。在可以调用 OLE 之前,必须将当前线程设置为单线程单元(STA)模式。请确保您的 Main 函数带有 STAThreadAttribute 标记。 只有将调试器附加到该进程才会引发此异常。

异常: 在可以调用 OLE 之前,必须将当前线程设置为单线程单元(STA)模式.请确保您的 Main 函数带有 STAThreadAttribute 标记. 只有将调试器附加到该进程才会引发此异常. ...

- 【转】使用SQL Tuning Advisor STA优化SQL

SQL优化器(SQL Tuning Advisor STA)是Oracle10g中推出的帮助DBA优化工具,它的特点是简单.智能,DBA值需要调用函数就可以给出一个性能很差的语句的优化结果.下面介绍一 ...

- 如何用 SQL Tuning Advisor (STA) 优化SQL语句

在Oracle10g之前,优化SQL是个比较费力的技术活,不停的分析执行计划,加hint,分析统计信息等等.在10g中,Oracle推出了自己的SQL优化辅助工具: SQL优化器(SQL Tuning ...

- [BZOJ1131][POI2008] Sta 树的深度

Description 给出一个N个点的树,找出一个点来,以这个点为根的树时,所有点的深度之和最大 Input 给出一个数字N,代表有N个点.N<=1000000 下面N-1条边. Output ...

- 在可以调用 OLE 之前,必须将当前线程设置为单线程单元(STA)模式

在可以调用 OLE 之前,必须将当前线程设置为单线程单元(STA)模式 转载自:http://blog.163.com/smhily_min/blog/static/75206226201092011 ...

随机推荐

- 条件锁Condition

"""设计场景:timo先说一句,亚索再说一句timo: timo队长正在待命yasuo: 面对疾风吧timo: timo整装待发yasuo: 哈杀gay "& ...

- DOM操作节点对象集合

<!DOCTYPE HTML PUBLIC "-//W3C//DTD HTML 4.01//EN" "http://www.w3.org/TR/html4/stri ...

- 04-Java基础语法【IDEA、方法】

重要内容记录: 01.IDE介绍 IDE(Integarted Development Environment)是Java集成开发环境,是一种专门用来提高Java开发效率的软件. 免费的IDE:Ecl ...

- 后台异常 - org.apache.jasper.JasperException

问题描述 org.apache.jasper.JasperException: Unable to compile class for JSP 问题原因 tomcat6不支持jdk1.8版本

- mac环境下,pycharm2018 配置 anaconda。

2018版的pycharm与之前的版本在配置anaconda上流程略有不同.直接上图 1.新建工程,展开会看到系统默认的编译环境名叫virtualenv,是基于python3.5的环境(如果没有安装过 ...

- Oracle查询当前用户和当前用户下的所有表

转载自:http://blog.itpub.net/29485627/viewspace-1246317/ Oracle查询当前用户和当前用户下的所有表 (1)查询当前用户 SQL> show ...

- codeforces 1288E. Messenger Simulator(树状数组)

链接:https://codeforces.com/contest/1288/problem/E 题意:序列p的长度为n,初始序列为1 2 3 4 ...n,然后有m次操作,每次指定序列中一个数移动到 ...

- 调用系统计算器n次

#define _CRT_SECURE_NO_WARNINGS #include<stdio.h> #include<stdlib.h> void main1(){ int n ...

- dp--C - Mysterious Present

C - Mysterious Present Peter decided to wish happy birthday to his friend from Australia and send hi ...

- 使用docker布署wordpress

环境准备 本博客使用docker环境搭建,从而做到布署简单 centos7环境(centos6跑docker要升级内核,也不建议这样做) 在centos7上安装好docker环境docker安装文档 ...