Quartus II 18.x Modelsim仿真设置

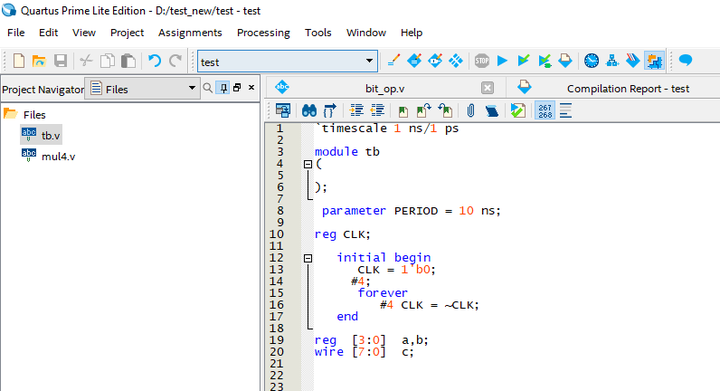

- QuartusII 18.x的界面如下:

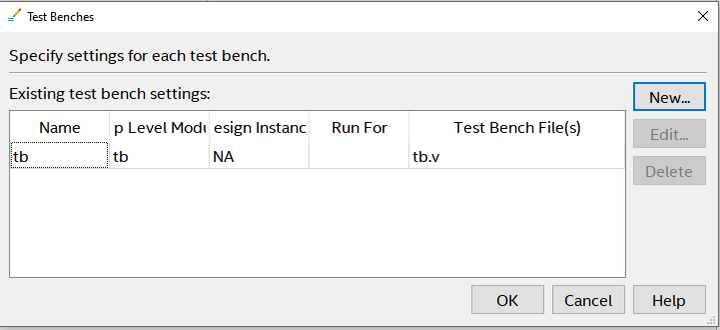

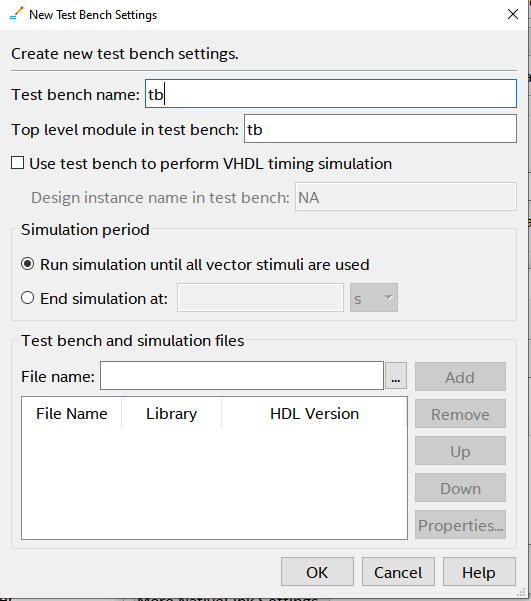

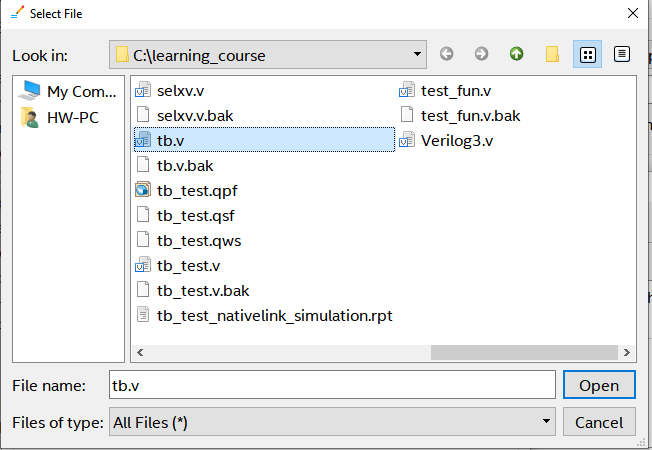

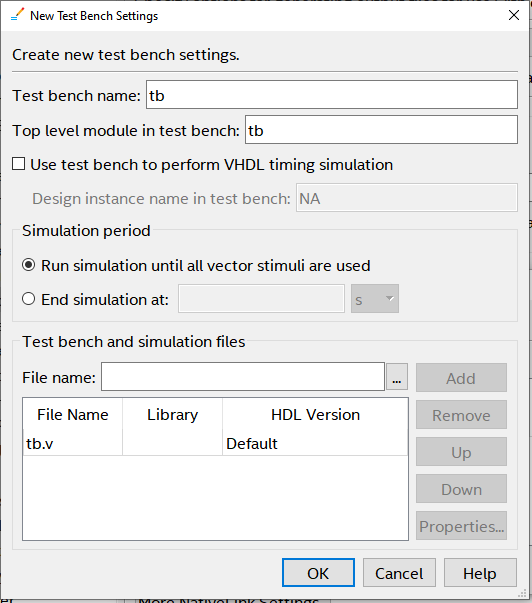

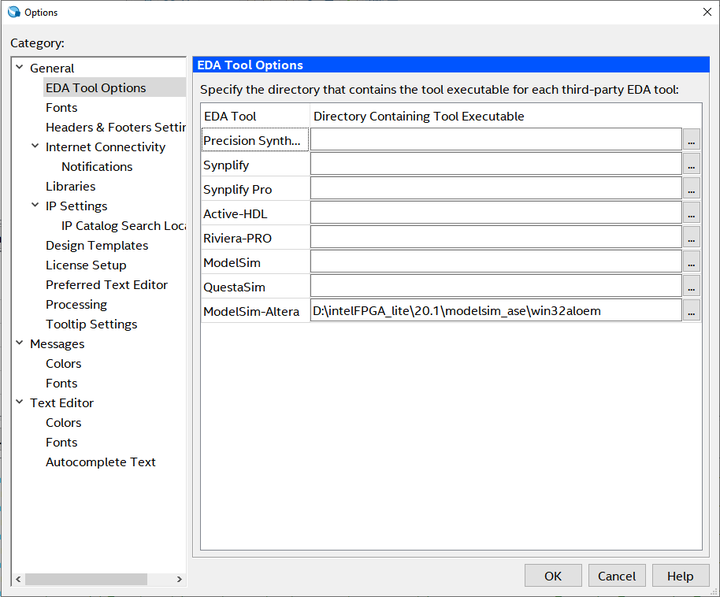

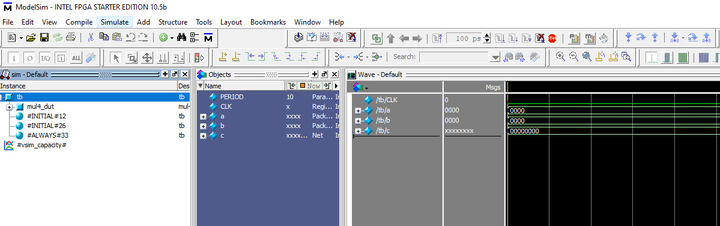

- QuartusII仿真 仿真设置步骤如下:

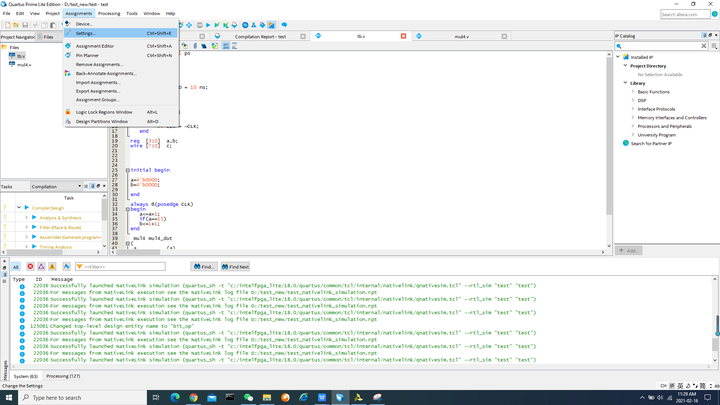

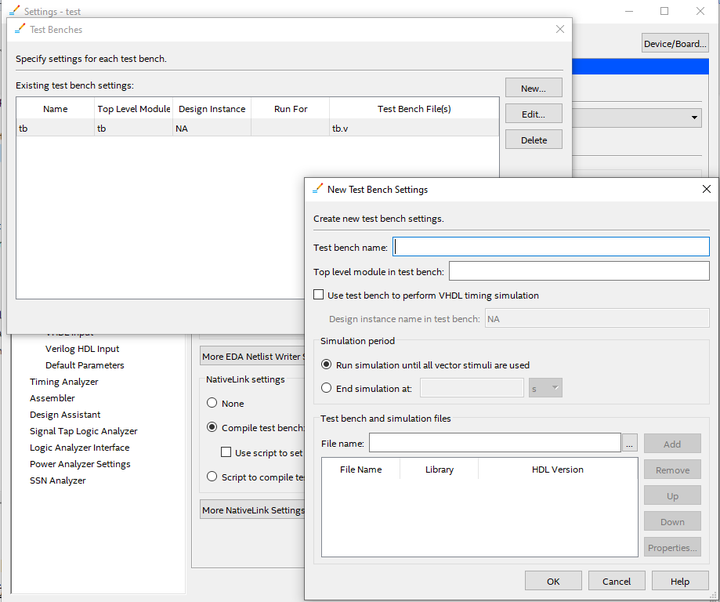

- 在菜单Assignment 下选中Settings…,如下图:

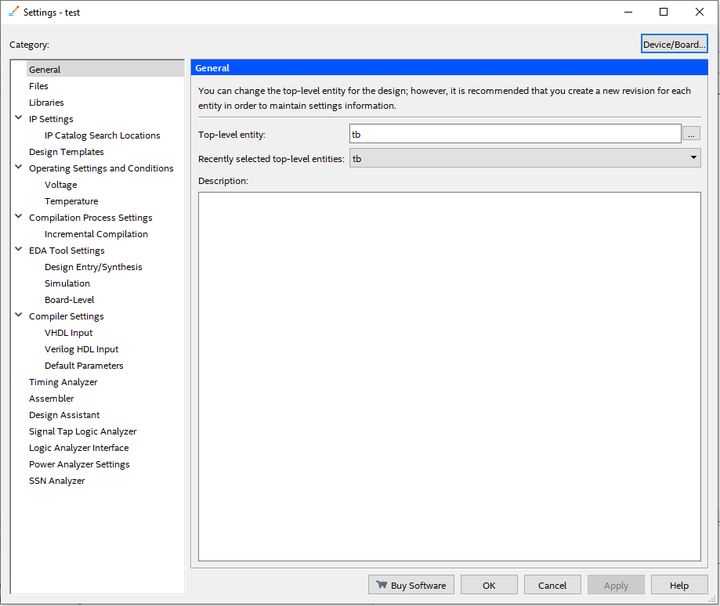

- 打开Settings 对话框

- 在General对话框设置Top-level entity 为tb(testbench 文件)

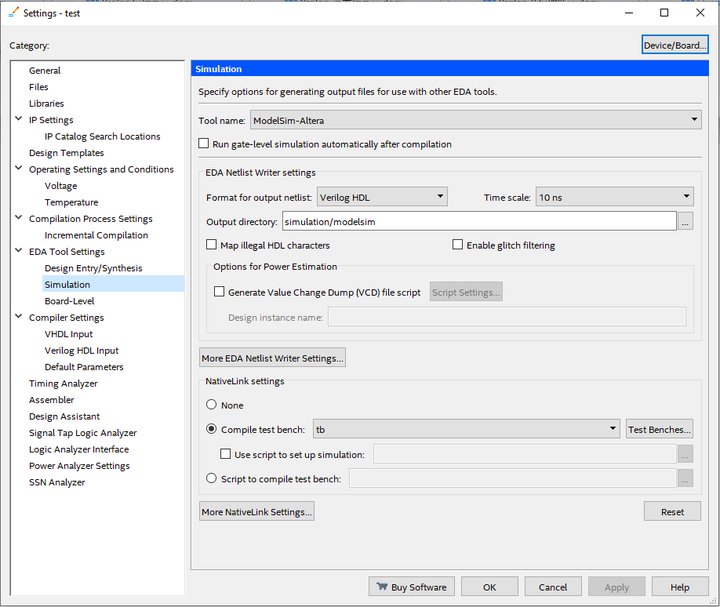

- 在EDA Tools setting 选中 Simulation,如图5

- 在Project Navigator 里选取mul4.v, 鼠标右键单击,Set as top level entity。单击工具栏图标Start Analysis and Elaboration, 如果有语法错误,则修改,直到没有错误为止。

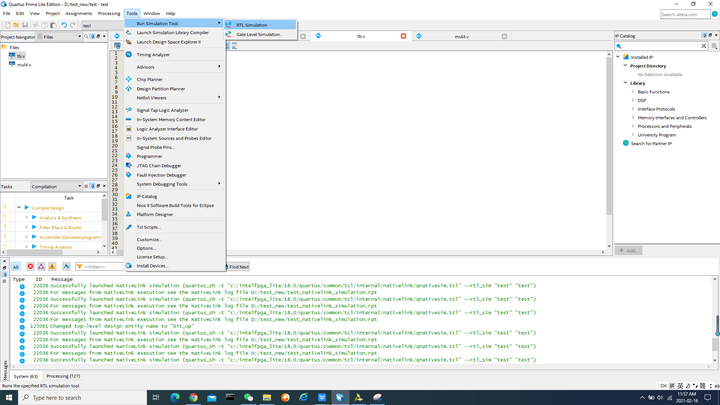

- 以上步骤设定好后,如图12,在主菜单Tools下,点击Run Simulation Tool ->RTL Simulation

Quartus II 18.x Modelsim仿真设置的更多相关文章

- Quartus II——工程建立和常用设置

Quartus ii是针对Altera FPGA的一款EDA软件,在此以一个led闪烁工程来简单说一下基本操作: 一.注意事项 Quartus ii最大的注意事项就一点:工程名称以及工程里面的文件名称 ...

- quartus II输入原理图及仿真步骤

在Quartus II中输入原理图以及实现仿真是学习基本数字电路的好方法.下面以一个基本的D锁存器为例,在quartus II 13.0中一步一步来实现原理图输入以及仿真过程. 1,创建工程 指定工程 ...

- FPGA学习记录 - Quartus II 未使用管脚设置为三态输入

未使用管脚设置为三态输入 Assignments -> Device 或双击器件

- Quartus II 与 Modelsim 联调【转】

Quartus II 9.0版本的时候软件还有自带的仿真工具,现在安装的是11.0以上版本,才发现 Quartus II 11.0以上取消了软件自带的波形仿真工具,因此需要波形仿真就要调用专业的仿真工 ...

- Altera Quartus II 15.0安装

写在前面的话 开始学习之前,我们首先应该选择并安装好自己的开发工具,那么我们用什么软件来编译代码呢?梦翼师兄推荐给大家的是Altera 目前最新的Quartus II 15.0 版本,当然啦,这 ...

- 【转】Quartus II调用modelsim无缝仿真

Quartus II调用modelsim无缝仿真 ★emouse 思·睿博客文章★ 原创文章转载请注明:http://emouse.cnblogs.com 本篇文章为转载,写的不错,最近在学mode ...

- Quartus II调用modelsim无缝仿真

本篇文章为转载,写的不错,最近在学modelsim仿真,网上的教程很乱,把自己认为不错的整理贴出来,后面有机会会写个详细点的. Quartus 中调用modelsim的流程 1. 设定仿真工具 ass ...

- FPGA —— Quartus II 15.0 使用 ModelSim SE-64 2019.2 软件进行仿真

Quartus II 15.0 使用 ModelSim SE-64 2019.2 软件进行仿真 ModelSim 仿真 Verilog HDL 时需要编写一个 TestBench 仿真文件,通过仿真文 ...

- (转)Quartus II和Modelsim的联合仿真(详细)

这篇文章不需要在modelsim中建库.映射.建工程等一些繁琐的步骤,直接使用modelsim中的默认work库.使用quartus+modelsim联合仿真. 首先推荐一篇文章 http://www ...

- 设置 Quartus II 的仿真时间大于 1us

Quartus II 仿真的默认时长是 1us. 设置时钟时看到 End time 想修改时长,把默认的 1us 改成 10us. 然后提示 End time 不合法.(只能设置为 0 到 1us) ...

随机推荐

- Win11右键默认显示更多选项的设置

怎么让Win11右键默认显示更多选项?有很多朋友不喜欢win11系统的右键菜单显示,经常需要多点一次"显示更多选项"才能看到想要的内容,大家想知道如何让win11右键菜单默认显示更 ...

- Spring UnitTest

demo:https://files.cnblogs.com/files/netact/spring01.zip 首先说一下Spring IOC的运行机制,同过xml或者annotation()来将p ...

- vvv动态组件和keep-alive

<!DOCTYPE html><html> <head> <style> </style> <script src="a.j ...

- MySQL之校对集问题

随笔记录方便自己和同路人查阅. #------------------------------------------------我是可耻的分割线--------------------------- ...

- git 与远程仓库关联返回 fatal: remote origin already exists 解决方法

今天领导新建了一个代码仓库,我按照流程一步步推送代码,结果到了关联仓库的时候,返回 fatal: remote origin already exists(远程源已经存在) 下面是解决方法 1.删除远 ...

- vim中的命令行 %! 是啥意思?

:%! command pipes the current file's contents to command's stdin, and replaces the file's contents w ...

- iis express添加网站,并启动

1.查看网站列表 C:\Program Files (x86)\Microsoft Visual Studio 12.0>"C:\Program Files\IIS Express\a ...

- HDFS文件块

知识点补充 HDFS优缺点: 优点 (1)高容错性.节点存放的副本比较多. (2)适合处理大数据. GB.TB.PB级别的数据都可以处理. (3)可以构建在廉价的机器上,通过多副本机制来提高可靠性. ...

- Jquery_001

jQuery 页面加载初始化的方法有3种 ,页面在加载的时候都会执行脚本,应该没什么区别,主要看习惯吧,本人觉得第二种方法最好,比较简洁. 第一种: $(document).ready(functio ...

- JAVA XML转对象

最近遇到XML转对象进行业务操作的问题 这是我需要解析的XML 1,建XML对应自己需要参数的Bean.有的很长很乱,没必要全部建,只建自己需要的就行了 import lombok.Data; imp ...