02-FPGA设计流程介绍——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线——普利斯队长精心奉献

课程目标: 1.了解并学会FPGA开发设计的整体流程

2.设计一个二选一选择器并进行功能仿真、时序仿真以及板级验证

实验平台:芯航线FPGA开发板、杜邦线

实验内容:

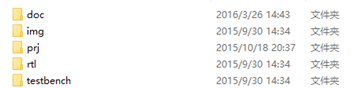

良好的文件夹设置以及工程管理是一个好的FPGA设计的基础,在学习之初就建立俩良好的习惯,会少走一些弯路。因此我们首先在新建的工程文件夹下面,分别建立如图2-1所示的子文件夹。

图2-1 FPGA工程子文件夹

上图中,prj为工程文件存放目录;rtl为verilog可综合代码存放目录;testbench为测试文件的存放目录;img为设计相关图片存放目录;doc为设计相关文档存放目录;ip文件夹存放quartus ii中生成的ip核文件。

建立工程

打开安装好的Quartus II软件,软件启动界面如图2-2所示

图2-2 Quartus II启动界面

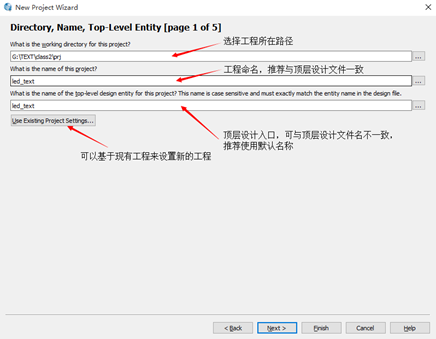

首先在这里单击Creat a New Project来新建一个工程向导。界面如图2-3所示。

图2-3 工程路径设置以及命名

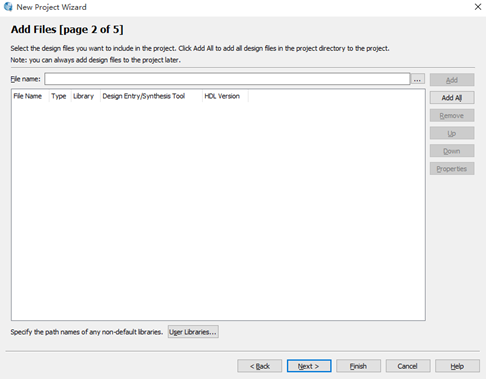

第二步,添加已有设计文件。如没有可直接点击Nxet,本次单击Nxet。

图2-4 工程中添加相关设计文件

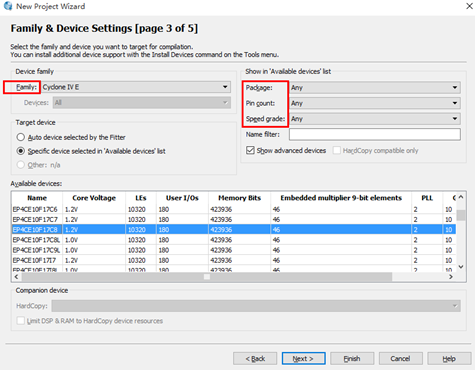

第三步,选择器件。在这里选择芯航线FPGA开发板上的Cyclone IV E系列的EP4CE10F17C8。这里可在右面红色框内可以添加限定条件来减少需要翻看器件的书目。

图2-5 设置工程用器件

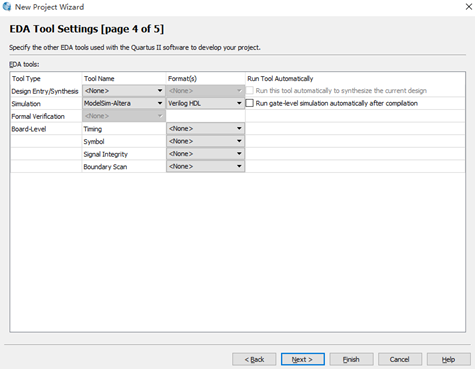

第四步,EDA工具的设定。从上依次是综合工具、仿真工具、形式验证工具以及板级验证工具。可根据实际情况自行设定。在这里根据自己安装情况将仿真工具设置为Modelsim-Altera或者Modelsim,语言选择Verilog HDL。

图2-6 EDA工具设定

第五步,单击Finish完成工程的建立,至此一个FPGA的工程已经建立完毕。

设计输入

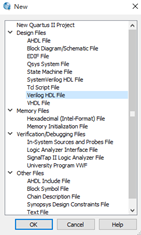

工程建立完成后,需要为工程添加新的设计文件,单击File—New—Verilog HDL File,或者工具栏中的New,弹出图2-7-2的选择框。此处选择Design Files中的Verilog HDL File。

图2-7-1 新建设计文件图2-7-2 新建设计文件选择框

新的文件建立完成,输入以下设计,并已led_text.v命名保存到工程所在的rtl文件下。

|

module led_test(a,b,key_in,led_out); input a;//输入端口A input b;//输入端口B input key_in; //按键输入,实现输入输入通道的选择 output led_out; //led 控制端口 //当key_in == 0 :led_out = a assign led_out = (key_in == 0)? a : b; endmodule |

分析和综合

单击工具栏中的Start Analysis & Synthesis来进行分析和综合。如在设计过程有失误的地方,在分析和综合后会提示Error或者Warning,需针对不同情况进行修改。芯航线汇总了常见的问题以及解决方式,可以参考用户手册并针对性解决。

图2-8 分析和综合

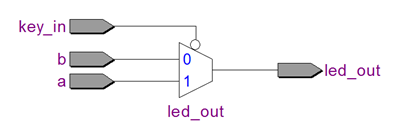

全编译后可以在RTL Viewer中可以看到图2-9所示的硬件逻辑电路。即为一个二选一选择器,符合预期设计。

图2-9 RTL Viewer

功能仿真

为了验证以上逻辑设计是否成功,在直接下载到开发板观察之前需编写激励文件,此处再新建一个.v文件输入以下内容。并以led_test_tb.v保存到工程对应的testbench文件夹下。并再次进行分析和综合查看是否存在语法设计错误。

|

`timescale 1ns/1ps module led_test_tb; //激励信号定义,对应连接到待测试模块的输入端口 reg signal_a; reg signal_b; reg signal_c; //待检测信号定义,对应连接到待测试模块的输出端口 wire led; //例化待测试模块 led_test led_test0( .a(signal_a), .b(signal_b), .key_in(signal_c), .led_out(led) ); //产生激励 initial begin signal_a = 0;signal_b = 0;signal_c = 0; #100;//延时100ns signal_a = 0;signal_b = 0;signal_c = 1; #100; signal_a = 0;signal_b = 1;signal_c = 0; #100; signal_a = 0;signal_b = 1;signal_c = 1; #100; signal_a = 1;signal_b = 0;signal_c = 0; #100; signal_a = 1;signal_b = 0;signal_c = 1; #100; signal_a = 1;signal_b = 1;signal_c = 0; #100; signal_a = 1;signal_b = 1;signal_c = 1; #200; $stop; end endmodule |

设置仿真脚本

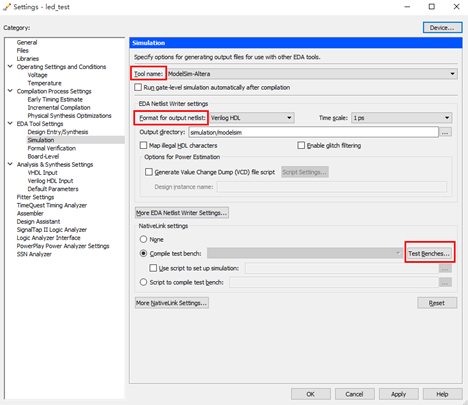

单击标题栏的Assignments—Settings—Simulation,查看仿真工具以及语言是否与之前一致否则进行相应修改。选中Compile test bench单击Test Benches后点击OK。可以看到如图2-10界面。

图2-10-1 仿真脚本设置

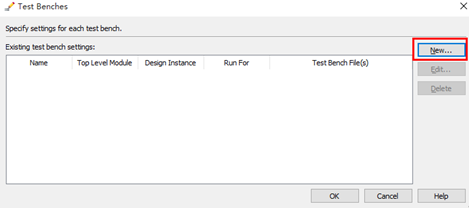

图2-10-2 新建激励

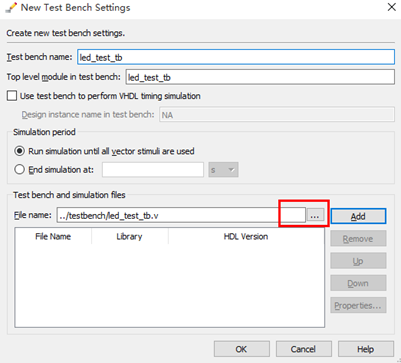

点击New会弹出如图2-11所示的testbench设置文件对话框,找到已经编写好的激励文件,单击Add。在Test bench name中填写对应的激励名称。点击OK后回到主界面

图2-11 测试激励设置

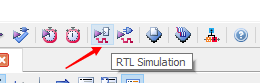

单击Tools—Run Simulation Tool—RTL Simulation或者单击工具栏中的RTL Simulation来进行前仿真也就是常说的功能仿真。

图2-12 开启功能仿真

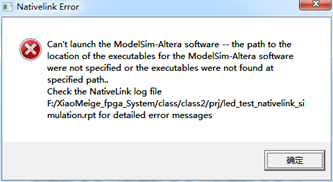

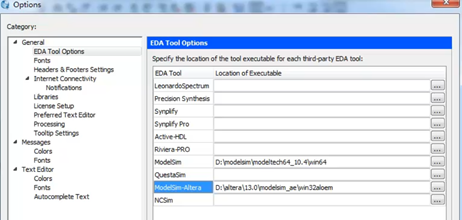

如出现如图2-13对话框,即提示仿真软件路径报错,可在Tools—Options—EDA Tool Options设置对应的仿真软件的路径即可,如图2-14所示。

图2-13 错误信息示例

图2-14 设置EDA工具的链接

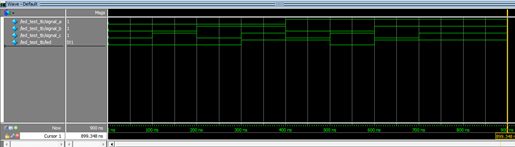

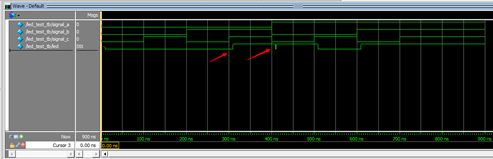

时led_out等于a,当key_in等于1时led_out等于b。即功能仿真通过。

图2-15 功能仿真波形

如没有出现预期波形可针对具体问题具体分析,芯航线也汇总了一部分常见问题及解决办法,此部分详细内容也可以参考用户手册相关内容。

布局布线

点击QII主界面的Start Compilation,进行综合&布局布线。布局布线过程中如遇出错,针对相应情况具体修改。

图2-16 布局布线

时序仿真

点击Tools—Run Simulation Tool—Gate Leval Simulation或者工具栏点击Gate Leval Simulation进行后仿真也就是门级仿真。

图2-17 门级仿真

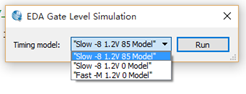

弹出选择时序模型对话框,可针对相应情况具体选择。此时可选择第一个,慢速工作温度为85摄氏度内核供电1.2V的情况进行仿真。

图2-18 仿真模型设置

在Modelsim中可以看到类似图2-19的波形,存在不希望存在的脉冲。且在200ns时的led相对输入信号有一定时间的逻辑延时。

图2-19 时序仿真波形

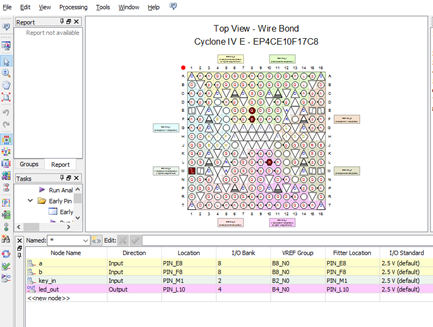

IO分配以及生成配置文件

在标题栏中Assignments—Pin Planner或者直接单击进行IO分配亦或者编写tcl文件,此处需针对不同板卡进行不同的设置。

图2-20 Pin Planner

芯航线开发板的引脚分配可以在附赠资料中查到,最终的配置如图2-21所示。

图2-21 分配好的引脚

在分配好引脚后,仍需进行一次全编译才能使管脚分配生效。

配置FPGA下载

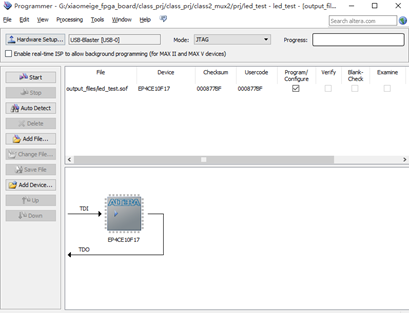

单击工具栏中的Programmer,

图2-22 Programmer

弹出以下对话框,单击Start即可将设计好的逻辑下载到开发板中。通过按键以及两根杜邦线控制E8、F8接入不同的电压值可以观测到led灯具有不同的亮灭效果。

图2-23 下载界面

FPGA也支持多种下载方式,不同下载方式的具体操作可参见开发板附赠中的用户手册。

如在下载过程中出现其他情况,可查询芯航线附赠的用户手册相关章节进行解决,此处不再详述。

至此一个基本的FPGA设计开发流程介绍完毕。

02-FPGA设计流程介绍——小梅哥FPGA设计思想与验证方法视频教程配套文档的更多相关文章

- 09B-独立按键消抖实验02——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线--普利斯队长精心奉献 实验目的: 1.复习按键的设计 2.用模块化设计的方式实现每次按下按键0,4个LED显示状态以二进制加法格式加1,每次按下按键1,4个LED显示状态以二进制加法格式减 ...

- 04-时序逻辑电路设计之计数器——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线--普利斯队长精心奉献 实验目的:以计数器为例学会简单的时序逻辑电路设计 实验平台:芯航线FPGA核心板 实验原理: 时序逻辑电路是指电路任何时刻的稳态输出不仅取决于当前的输入,还与前一时刻输入 ...

- 03-组合逻辑电路设计之译码器——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线——普利斯队长精心奉献 课程目标: 1. 再次熟悉Quartus II工程的建立以及完整的FPGA开发流程 2. 以译码器为例学会简单组合逻辑电路设计 实验平台:无 实验原理: 组合逻辑, ...

- 05-IP核应用之计数器——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线--普利斯顿队长精心奉献 实验目的:了解FPGA的IP核相关知识并以计数器IP核为例学会基本IP使用的流程 实验平台:无 实验原理: IP核(Intellectual Propert ...

- 06-BCD计数器设计与应用——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线--普利斯队长精心奉献 实验目的:1.掌握BCD码的原理.分类以及优缺点 2.设计一个多位的8421码计数器并进行验证 3.学会基本的错误定位以及修改能力 ...

- 10-8位7段数码管驱动实验——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线--普利斯队长精心奉献 实验目的: 1.实现FPGA驱动数码管动态显示: 2.使用In system sources and probes editor工具,输入需要显示在数码管上的的数据, ...

- 09A-独立按键消抖实验01——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线--普利斯队长精心奉献 实验目的: 1.复习状态机的设计思想并以此为基础实现按键消抖 2.单bit异步信号同步化以及边沿检测 3.在激励文件中学会使用随机数发生函数$random 4.仿真模 ...

- 08-FPGA状态机设计实例——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线--普利斯队长精心奉献 实验目的:1.学习状态机的相关概念 2.理解一段式.两段式以及三段式状态机的区别以及优缺点 实验平台:芯航线FPGA核心板 实验原理: 状态机全称是有限状态机(fin ...

- 07-阻塞赋值与非阻塞赋值原理分析——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线--普利斯队长精心奉献 实验目的:掌握阻塞赋值与非阻塞赋值的区别 实验平台:无 实验原理: 阻塞赋值,操作符为"=","阻塞"是指在进程语句( ...

随机推荐

- sbt %%

在依赖库选项中会看到其中有的是 %%,而有的是一个%. 这表示 :“要求sbt寻找用当前你配置的scala版本编译出来的jar包.” 因为scala不同版本编译出来的结果会不兼容.

- 判断pc端还是移动,并给移动加上其它的样式文件方法

所有移动端PC端 按 640 进行排版 body, html { width: %; height: %; overflow: hidden; background-color: #; } bod ...

- asp.net自定义404页面

网上有很多方法,不过大体相同,这只是其中一个方法,亲测有效,记录后面可能会有用 1. 先写好一个404页面 404.aspx在项目根目录下 然后在配置文件中添加 <!-- 注意这个模式,redi ...

- 2016huas暑假集训训练题 G-Who's in the Middle

题目链接:http://acm.hust.edu.cn/vjudge/contest/121192#problem/G 此题大意是给定一个数n 然后有n个数 要求求出其中位数 刚开始以为是按数学中的 ...

- DOM模型有三种

<!-- DOM模型有三种: DOM level 1:将HTML文档封装成对象. DOM level 2:在level 1基础加入新功能,比如解析名称空间. //<html xmlns=& ...

- 全局方法&Number对象

//js端 function println(string){ document.write(string+"<br/>"); } //html端 <script ...

- python随机服务器的双线出口ip发送邮件

#-*- coding:utf-8 -*-import smtplibimport sysimport random import socketfrom email.mime.text import ...

- request

social.Favorites.AddFavorite=function(angel) { a = $.extend(true, { type: "POST", url: &qu ...

- JS 获取 地址栏 参数

法一:正则表达式 /** * 采用正则表达式获取地址栏参数: **/ var GetQueryString = function (name) { var reg = new RegExp(" ...

- php--数组函数array

1.array_combine array_combine是一种函数,通过合并两个数组来创建一个新数组,其中的一个数组是键名,另一个数组的值为键值.如果其中一个数组为空,或者两个数组的元素个数不同,则 ...