verilog抓外部低频输入信号的上升沿和下降沿

版权申明:本文为博主窗户(Colin Cai)原创,欢迎转帖。如要转贴,必须注明原文网址 http://www.cnblogs.com/Colin-Cai/p/7220107.html 作者:窗户 QQ:6679072 E-mail:6679072@qq.com

已经很久很久很久,没有真正在正式工作中设计过数字电路,有的只是在业余的时候玩玩。

想起最早的时候,学习数字电路设计,用的是原理图。习惯于用原理图去思考,后来用VHDL,再后来习惯了verilog那和C语言一样的运算符以及简洁的表达,不再喜欢VHDL的累赘。之所以用HDL,最初的想法仅仅是因为原理图画起来累,理解起来繁琐且不便于修改罢了,脑子里最开始总是不断在真实电路和HDL代码中映射。

现在EDA的技术越来越发达,我一朋友从事IC设计,却从来不理解原理图设计,让我一度匪夷所思,后来想想可能只是因为他没有经历过我们以前那个阶段罢了。

闲话不多说了,回到这个主题,这其实是数字设计中经常遇到的问题。初学者看到的就是,这还不简单,直接把这个信号引入当D触发器的时钟,结果超复杂的异步设计,陷入万劫深渊无法自拔,这还没包括外部信号可能会有干扰而产生毛刺。

首先,我们要先默认,外部输入的信号频率要低过主频,否则无法处理,其次,外部输入的信号是可能会有毛刺的。

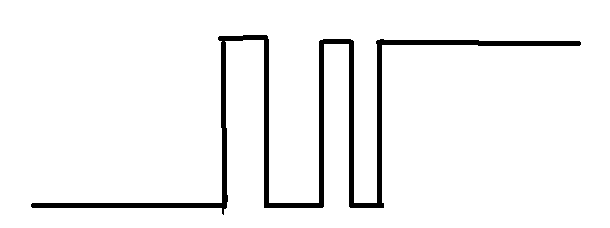

如上所示是一个毛刺,不能当时发生了上升沿。

如上所示,只是上升沿的过程出现了毛刺,不能当成是多个上升沿发生。

那么我们得想办法把毛刺过滤。毛刺发生的情况并不多,于是我们就想,每次系统时钟上升沿(或下降沿)的时候都对外部数字信号采样,当外部真正的电平(也就是去掉毛刺之后)是低电平的时候,采样也绝大多数都是低电平,采到高电平的毛刺是凤毛麟角,高电平也同理。

再进一步我们就会想,如果连续采到n个电平是高电平,那么实际电平就是高电平;反之,如果连续采到n个电平是低电平,那么实际电平就是低电平;如果连续抓的n个电平有高有低,则实际电平就是之前保持的。

如此就得到了过滤毛刺之后的真实信号,然后再用真实信号连续两个系统时钟的值来判断上升沿下降沿。

于是有了如下设计

`timescale 1ns / 1ns

module top

(

nRst,

clk,

in,

en_posedge

);

input nRst, clk, in;

output en_posedge; parameter W=;

reg [W-:]in_reg;

always@(negedge nRst or posedge clk)

if(!nRst)

in_reg <= {W{'b0}};

else

in_reg <= {in_reg[W-:], in}; reg in_filter, in_filter_last;

always@(negedge nRst or posedge clk)

if(!nRst)

in_filter <= 'b0;

else case({&in_reg, |in_reg})

'b00: in_filter <= 1'b0;

'b11: in_filter <= 1'b1;

default: in_filter <= in_filter;

endcase always@(negedge nRst or posedge clk)

if(!nRst)

in_filter_last <= 'b0;

else

in_filter_last <= in_filter; reg en_posedge;

always@(negedge nRst or posedge clk)

if(!nRst)

en_posedge <= 'b0;

else if((!in_filter_last) & in_filter)

en_posedge <= 'b1;

else

en_posedge <= 'b0; endmodule

所描述的电路长这样

再来做一个testbench

`timescale 1ns / 1ns

module tb;

reg nRst, clk, in;

wire en_posedge; top t

(

nRst,

clk,

in,

en_posedge

); initial

forever

begin

clk = ;

#;

clk = ;

#;

end initial

begin

in=;

nRst=;

#;

nRst=;

#;

nRst=;

#;

in=;

#;

in=;

#;

repeat()

begin

in=;

#;

in=;

#;

end

in=;

#;

$stop;

end endmodule

仿真图如下

只认出了一次上升沿。抓取下降沿同理。

再来说说设计中的

parameter W=3;

这里的W代表着,设计可以过滤掉小于W-1个系统时钟周期的毛刺。

另外,in_reg和in_filter、in_filter_last要么全1要么全0,取决于默认情况下(一般是指无通信的时候)外部输入信号是什么电平。

想起以前工程中真的出现过问题,悲哀的教训,后来仔细想了很久,虽然看上去不难实现,但的确是吸取教训之后的设计结果。

verilog抓外部低频输入信号的上升沿和下降沿的更多相关文章

- NRF24L01使用外部中断读取数据的问题

NRF24L01读取数据不能使用中断的方式,原因如下: 首先NRF24L01中断触发时,IRQ引脚会一直保持低电平直到状态寄存器中的中断标志被重新清零. stm32的外部中断触发方式只有上升沿或者下降 ...

- 《FPGA全程进阶---实战演练》第二十一章之 几种常用电平分析及特性

TTL,CMOS以及LVTTL,LVCMOS TTL和CMOS是数字电路中两种常见的逻辑电平,LVTTL和LVCMOS是两者低电平版本.TTL是流控器件,输入电阻小,TTL电平器件速度快,驱动能力大, ...

- 【接口时序】5、QSPI Flash的原理与QSPI时序的Verilog实现

一. 软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件:ISE14.7 3.仿真工具:ModelSim-10.4-SE 4.Matlab版本:Matlab2014b/ ...

- VHDL:信号、端口以及和Verilog的区别

1.信号 信号是描述硬件系统的基本数据对象,它的性质类似于连接线.信号可以作为设计实 体中并行语句模块间的信息交流通道. 信号作为一种数值容器,不但可以容纳当前值,也可以保持历史值(这决定于 ...

- 硬件描述语言Verilog设计经验总结

一.硬件描述语言Verilog 粗略地看Verilog与C语言有许多相似之处.分号用于结束每个语句,注释符也是相同的(/* ... */和// 都是熟悉的),运算符"=="也用来测 ...

- 对Verilog 初学者比较有用的整理(转自它处)

*作者: Ian11122840 时间: 2010-9-27 09:04 ...

- verilog中wire与reg类型的区别

每次写verilog代码时都会考虑把一个变量是设置为wire类型还是reg类型,因此把网上找到的一些关于这方面的资料整理了一下,方便以后查找. wire表示直通,即只要输入有变化,输出马上无条件地反映 ...

- Verilog学习总结

1.多个always语句不能对同一变量赋值. 2.assign语句只能进行阻塞赋值,用来描述组合逻辑. 3.verilog描述方式:结构描述(门级描述和模块调用).数据流描述(assign,wire型 ...

- 不可综合的verilog语句分析

前半部分转自http://www.cnblogs.com/Mrseven/articles/2247657.html,后半部分为自己测试结果. 基础知识:verilog 不可综合语句 (1)所有综合工 ...

随机推荐

- SparseArray,SparseBooleanArray和SparseIntArray

package android.util; import com.android.internal.util.ArrayUtils; /** * SparseArrays 利用integer去管理ob ...

- 虚拟机安装 deepin Linux 注意事项

主要要注意下面几点: 一.虚拟机"客户机操作系统"类型 选择"Windows 7 x64" 选择"客户机操作系统"类型,这个选择十分重要,D ...

- Linux 链接详解(1)

可执行文件的生成过程: hello.c ----预处理---> hello.i ----编译----> hello.s -----汇编-----> hello.o -----链接- ...

- ##3.Keystone 验证服务--openstack

##3.Keystone 验证服务 openstack pike 安装 目录汇总 http://www.cnblogs.com/elvi/p/7613861.html #SQL上创建数据库并授权 #K ...

- Sublime text3 代码格式化插件

使用 Sublime text 3 格式化HTML代码,需要安装插件,具体安装步骤如下: 1. 打开菜单 -> 首选项(Perferences) -> 插件控制(Packpage Cont ...

- Android 7.0 中 ContentProvider 实现原理

欢迎大家前往腾讯云社区,获取更多腾讯海量技术实践干货哦~ 作者:汪毅雄 导语: 本文描述了ContentProvider发布者和调用者这两在Framework层是如何实现的. 作为Android的四大 ...

- mysql 各数据类型的 大小及长度

数字型 类型 大小 范围(有符号) 范围(无符号) 用途 TINYINT 1 字节 (-128,127) (0,255) 小整数值 SMALLINT 2 字节 (-32 768,32 767) (0, ...

- 深入理解javascript函数进阶系列第三篇——函数节流和函数防抖

前面的话 javascript中的函数大多数情况下都是由用户主动调用触发的,除非是函数本身的实现不合理,否则一般不会遇到跟性能相关的问题.但在一些少数情况下,函数的触发不是由用户直接控制的.在这些场景 ...

- pymysql实现MySQL与Python交互

常见MySQL操作 所需模块: pip3 install pymysql 查询(fetchone,fetchmany,fetchall): import pymysql #连接 con = pymys ...

- 【GISer&&Painter】GISer

基于上一篇OpenGL的渲染原理,这两周又陆续接触了一些关于WebGL绘图的一些内容,因为刚入门,很多东西又很晦涩,所以特意花了小半天的时间整理了一下,特此记录. 一 画布和画笔:创建Canvas ...