《FPGA全程进阶---实战演练》第十一章 VGA五彩缤纷

1基础理论部分

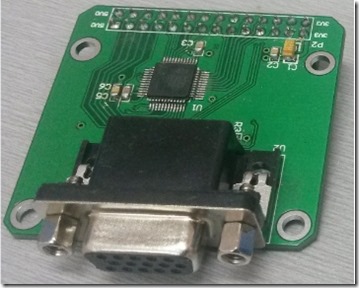

VGA(video graphics array)即视频图形阵列,是IBM在1987年随PS/2一起推出的使用模拟信号的一种视频传输标准。VGA相比与现在的视频传输接口来说已经过时,不过作为最低标准,基本上制造商都会接入此接口,图11.1是常见的VGA接口。

图11.1 VGA接口

对于VGA15个引脚的相关说明,如下图所示。

图11.2 VGA引脚说明

大家做实验的时候,可能会有一个误区,那就是做实验时直接把实验板的VGA接口接到笔记本电脑上,还兴高采烈的等待着显示图像,殊不知笔记本电脑是不能作为普通显示器显示的。

现在的显示器接口已经经过VGA,DVI(数字信号的传输),到现在的HDMI接口标准,实现数字高清影音传输的技术,因此最新的显示器基本上都会支持这几种接口。

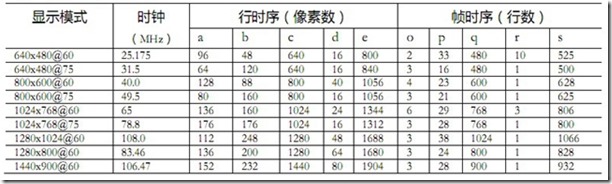

更多的时序标准,请参考http://tinyvga.com/vga-timing

由三原色RGB所组成的颜色种类,由RGB888(24位真彩色),RGB565,RGB444;(本实验所采用的是RGB565),对于带宽有限,图像要求不是特别高,这个RGB565已经可以满足要求了。对于RGB565模型,位的分配,由高到低,分别为R 15..11,G 10..5, B 4..0;

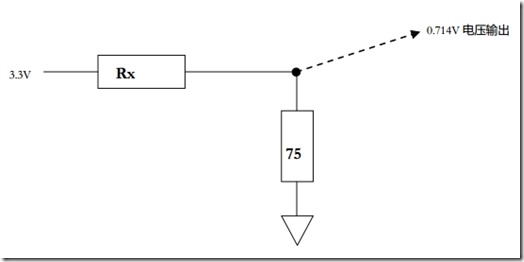

对于VGA的接口模拟电压,为0~0.714V,0代表无色,0.714代表满色,FPGA输出3.3V,所以还必须要经过DAC的转换。这些部分在做板子的时候,会继续补充、基本上现在成熟的方案,采用R-2R或者ADV7123。当然专用芯片成像质量很好。

对于显示器而言,VGA的分辨率越高,意味着显示的图像越清晰,包含信息也越多,画质更加好,图像更加保真。由于人眼的视觉暂留,要想实现显示器的不闪烁,至少需要实现每秒25帧画面的更新。通常显示器的扫描频率都在60帧及以上。

对于显示器而言,有的可以兼容多个分辨率模式,为了实现这种方式,许多显示器具有scaler功能,能够实现不同分辨率的兼容。

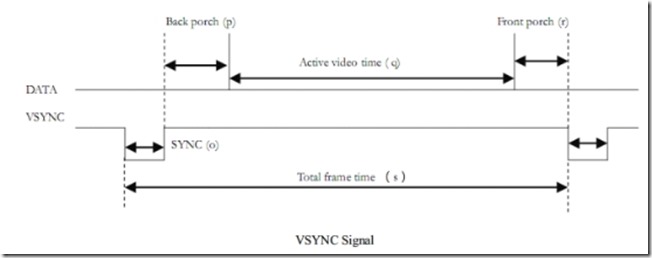

图11.2 场同步信号

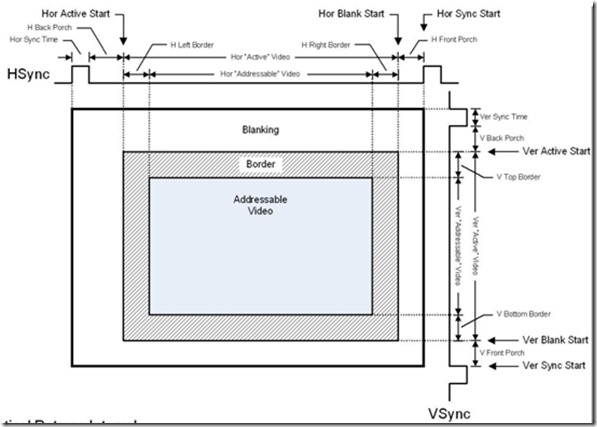

图11.3 行和场信号工作方式

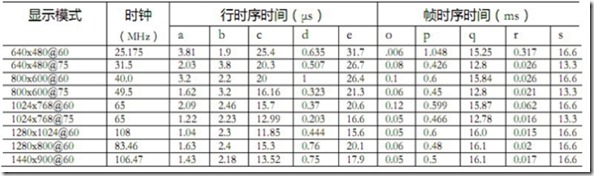

图11.4 常见的刷新时序表

1.2 VGA驱动电路部分

现在主要的用于VGA驱动电路的方案,一个是采用电阻R-2R的形式,一个是采用专用芯片,这两者各有优势。

对于VGA来说,有几路信号比较重要,RED,GREEN, BLUE信号,以及hsync 和vsync信号,其中hsync 和vsync信号可以直接和FPGA的IO口相连,但是rgb信号却不能,它需要0~0.714V模拟信号。

1.2.1 R-2R结构

图11.5 拓扑结构

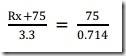

上图是视频DAC拓扑结构模式,根据上述模式计算Rx的值。

那么大概得到Rx = 271.6387Ω;

解出

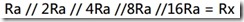

解出 ,所以我们采用Ra = 500Ω,可以选中1K和2K的电阻去串并联实现R-2R模型。这里是采用2K和1K串并联的方式实现5—6—5 ,即16位格式。

,所以我们采用Ra = 500Ω,可以选中1K和2K的电阻去串并联实现R-2R模型。这里是采用2K和1K串并联的方式实现5—6—5 ,即16位格式。

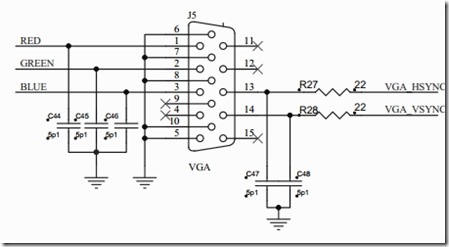

图11.7 VGA接口部分电路

图11.8 R-2R电路

1.2.2 专用芯片结构

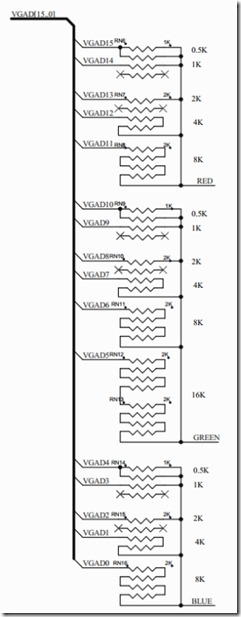

对于专用芯片去用于视频操作的,我们常用ADV7123。此款芯片最大采样率为330MHz,低功耗,3路10位DAC视频转换器。图11.9是原理图部分,图11.10是实物图。

图11.9 ADV7123原理图

图11.10 VGA实物图

2 Verilog代码实现部分

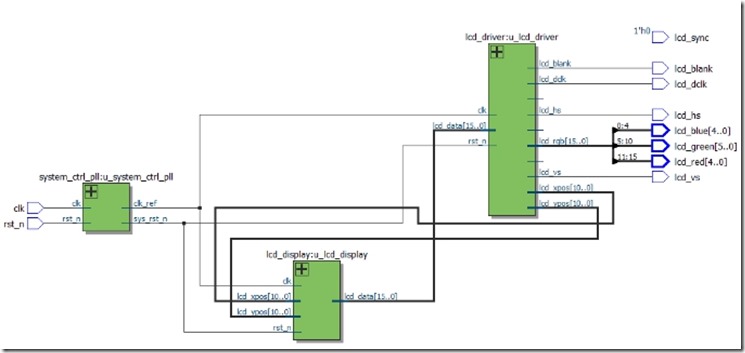

本次实验实现彩条测试功能,板卡载有一颗ADV7123芯片,FPGA驱动该芯片并产生VGA所需要的行和场信号,图11.11是RTL视图。

图11.11 RTL视图

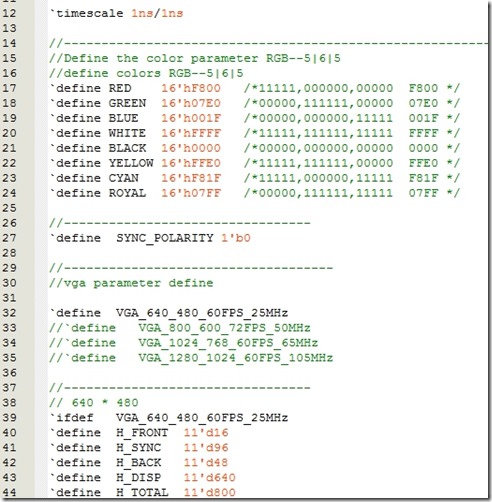

在lcd_para.v文件中定义了彩条各参数和VGA所需要的行和场信号所需要的像素数,这里利用了define和 ifdef指令,注意其用法。

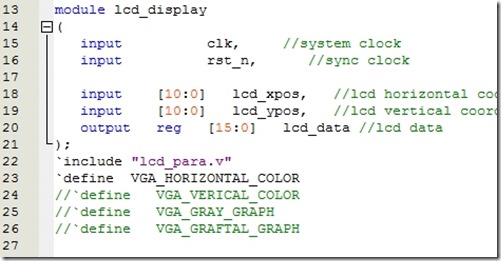

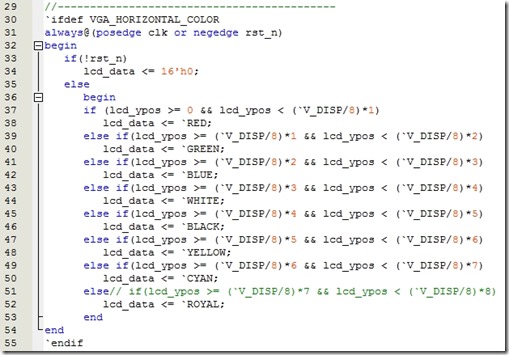

在lcd_display.v中,将lcd_para.v文件进行调用,且在23行到26行有几种测试实验,一种是水平彩条,一种是竖直彩条,灰度图以及纹理图。

上述就是具体每一种测试实验所对应的生成程序。

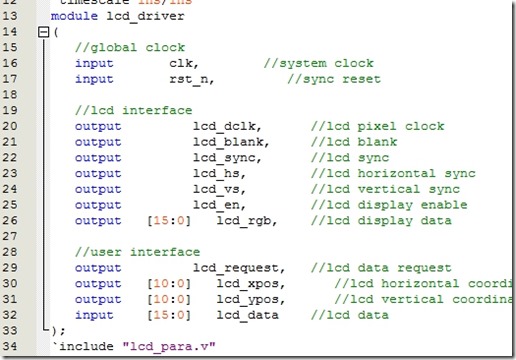

在lcd_driver.v中,生成驱动ADV7123的信号和产生VGA所需要的16位数据,以及在lcd_display.v中所需要的x和y坐标值。

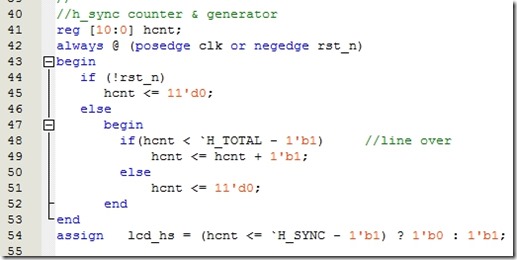

行信号的生成部分。

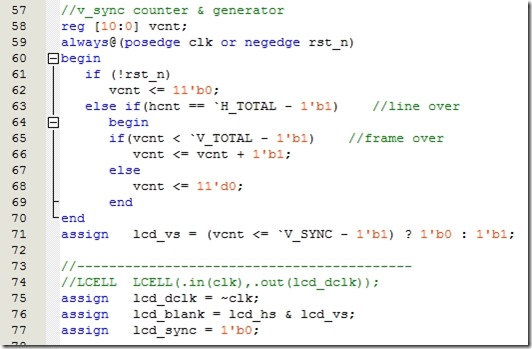

场信号生成部分,75行到77行是AD7123所需要的信号,可以看到驱动是非常简单的。这里75行ADV7123的驱动时钟和主时钟相反,以此来达到在主时钟的上升沿对数据进行采样。

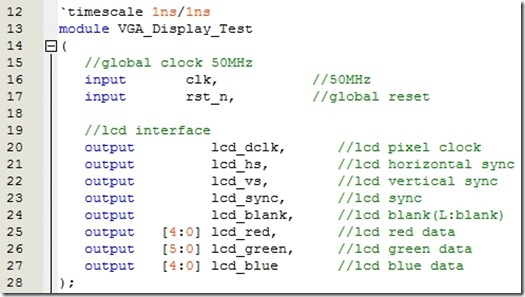

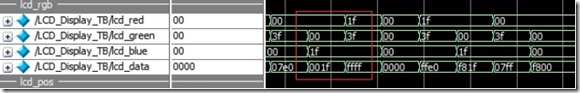

上述是对总的模块进行例化部分,注意25行到27行,由于ADV7123芯片需要RGB的格式为565,所以定义lcd_red,lcd_green,以及lcd_blue。

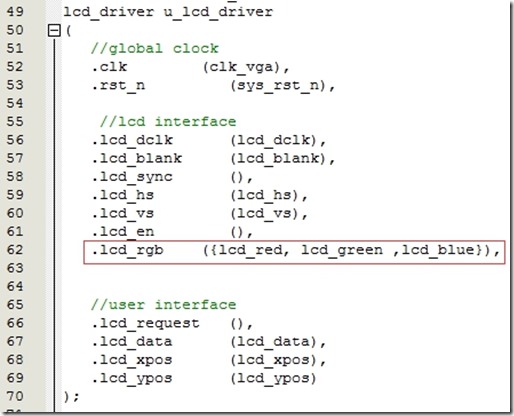

注意62行是对刚才定义的RGB信号的分配,由于lcd_rgb是16位数据,分别将高5位送给lcd_red,将中6位送给lcd_green,将低五位送给lcd_blue。

3 Modelsim仿真部分

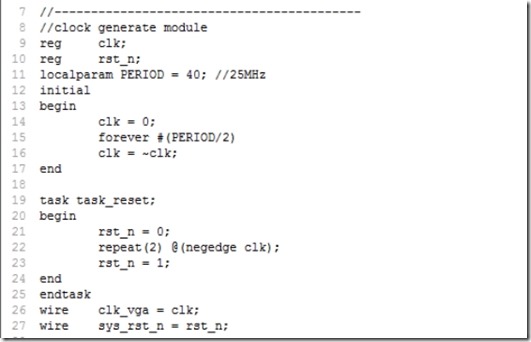

上述是testbench中的时钟模拟信号和复位模拟信号的产生,其中11行是模拟25MHz时钟。

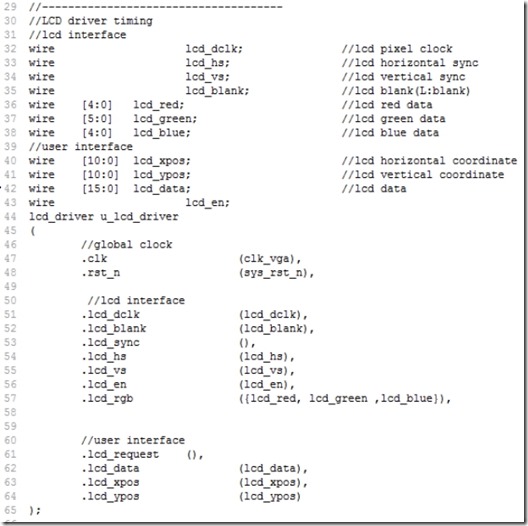

注意上述仿真时调用的模块名,因为我们想观察到各个信号的输出情况,所以只调用重要的两个模块lcd_driver和lcd_display即可,32行到43行是对调用模块的各个输出信号的声明,这里也可以看到,需要观察输出什么样的信号,只需定义为wire类型即可,前提是调用各个模块时,wire定义的变量必须是相对于输出的信号。

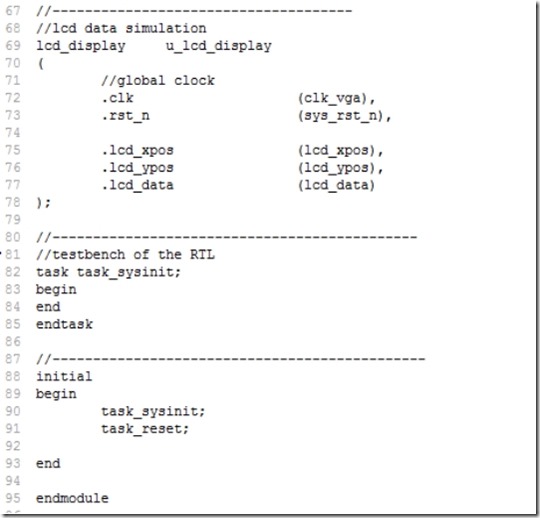

69行到78行是对lcd_display模块进行的例化。82行到85行是对输入信号的初始化,外部输入信号暂时没有,所有没有初始化任何信号。

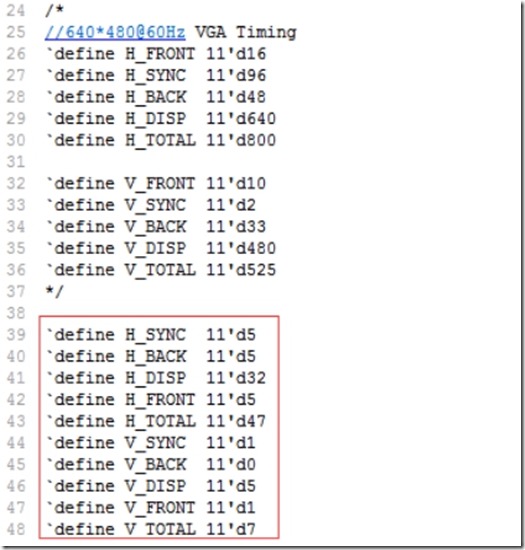

另外为了节省仿真时间在lcd_driver中将各参数适当缩小,以达到缩减仿真时间的目的,如下面所述。

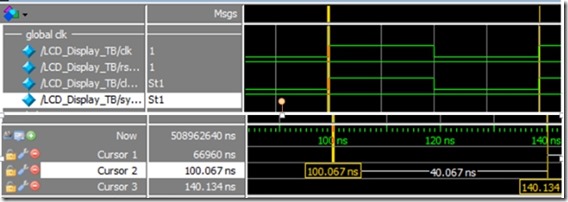

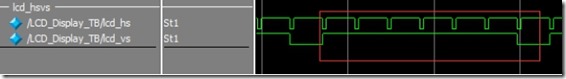

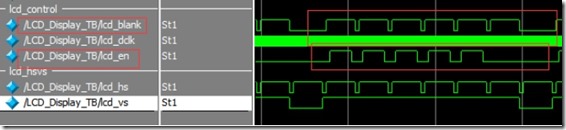

3.1 仿真波形

图11.11是时钟的仿真波形,时钟信号周期40ns,满足25MHz。图11.12是行和场信号的仿真,可以看到6个行信号,1个场信号。这和之前的VGA时序分析是一致的。图11.13是lcd_en信号和lcd_blank信号,这两个信号都和行和场信号有关。图11.14是RGB数据仿真出的波形

图11.11 时钟信号仿真

图11.12 行和场仿真信号

图11.13 使能和空白信号

图11.14 RGB输出的波形

《FPGA全程进阶---实战演练》第十一章 VGA五彩缤纷的更多相关文章

- 《FPGA全程进阶---实战演练》第一章之如何学习FPGA

对于很多初学者,大部分都是急于求成,熟不知越是急于求成,最终越是学无所成,到头来两手空空,要学好FPGA,必须弄懂FPGA本质的一些内容. 1.FPGA内部结构及基本原理 FPGA是可以编程的,必须通 ...

- 《FPGA全程进阶---实战演练》第一章之FPGA介绍

1 什么是FPGA FPGA也即是Field Programmable Gate Array的缩写,翻译成中文就是现场可编程门阵列.FPGA是在PAL.GAL.CPLD等可编程器件的基础上发展起来的新 ...

- 《FPGA全程进阶---实战演练》第二章之焊接板子及调试注意事项

1.若是读者第一次做板子,强烈建议画完PCB板后将PCB图打印出来,然后对照你买的芯片将芯片放置对 应的位置,然后查看所有的封装格式适不适合,否则等你做出板子来后再试,为时晚矣.笔者虽然知道要这么 做 ...

- 《FPGA全程进阶----实战演练》第二章之系统搭建

1 系统方案 对于设计一款硬件平台,首先要确定整体框架,确定各个模块所需要的芯片以及电压分配情况.图2.6是笔者曾经设计的硬件平台系统. 图2.6系统框图 对于选定一个系统方案之后,接下来做的要先去查 ...

- 《FPGA全程进阶---实战演练》第二章之硬件平台的搭建

学习FPGA,多多少少应该要懂得硬件电路的设计,这样不单单增加了自己的技能,而且还能够对FPGA的硬件实现有更好的了解. 1 模块划分 对于一个基本的FPGA硬件平台,常用的几个电路部分:(1)电源电 ...

- 《FPGA全程进阶---实战演练》第九章 计数器要注意

本小节我们来做一个好玩的事情,就是计数器,还记得在做LED自加实验时我们就曾经提到过关于计数器的相关议题,那么这节我们就来讨论讨论. 探讨一下如下的问题:请用verilog记八个数的写法,分析这个可以 ...

- 《FPGA全程进阶---实战演练》第二章之PCB layout注意事项以及投板几点说明

上一篇博客讲述了各个部分的原理图,那么根据原理图画出PCB,其实PCB是一门很大的学问,想要掌握谈何容易.就笔者在画PCB时的一些注意事项做一些说明. 1.电源部分的电源线 ...

- 《FPGA全程进阶---实战演练》第三十二章 Signal Tap II 应用实例

还有几天就要交文章终稿了,三年的研究生生活也快要结束了,时间飞快,岁月如梭,但学习技术的热情仍然不能松懈,不懂的东西太多,需要实时保持奋斗!!过些天会继续更新<FPGA全程进阶---实战演练&g ...

- 《FPGA全程进阶---实战演练》第二十一章 细说低速与高速电路设计之电阻 电容 电感 磁珠

1.1 什么是高速电路 信号的最高频率成分是取决于有效频率,而不是周期频率. 高速电路的定义是根据信号的有效频率来计算的,在现实世界中,任何信号都是由多个频率分量的正弦波叠加而成的.定义各正弦波分 ...

随机推荐

- 深入理解Linux内核-系统调用

系统调用:用户态进程向内核发出的,实现用户态进程调用硬件设备的函数或者中断:优点:使编程更容易,将用户从学习硬件设备的低级编程特性中解放:提高系统到安全性,内核在满足请求之前可以做正确性检查:提高可移 ...

- 细说php(二) 变量和常量

一. 变量的声明 1. php中声明变量的方法: $var = 123; 2. php是弱类型的语言, 变量的类型由存储的值决定 注: Java是强类型语言, 声明变量一定要先指定类型 二. 变量的 ...

- 关于docker容器和镜像的区别

docker的整个生命周期有三部分组成:镜像(image)+容器(container)+仓库(repository): 如下图所示,容器是由镜像实例化而来,这和我们学习的面向对象的概念十分相似,我们可 ...

- Linux设备驱动开发详解

Linux设备驱动开发详解 http://download.csdn.net/detail/wuyouzi067/9581380

- [SQL in Azure] Provisioning a SQL Server Virtual Machine on Azure

http://azure.microsoft.com/en-us/documentation/articles/virtual-machines-provision-sql-server/ Provi ...

- [Windows Azure] Administering your Windows Azure AD tenant

Administering your Windows Azure AD tenant 19 out of 20 rated this helpful - Rate this topic Publish ...

- 在CentOS6.5上安装/启动PostgreSQL

CentOS install PostgreSQL yum install postgresql-server Start PostgreSQL service postgresql initdb # ...

- c++ primer读书笔记之c++11(二)

1 新的STL模板类型,std::initializer_list<T> c++11添加了initializer_list模板类型,用于提供参数是同类型情况的可变长度的参数传递机制,头文件 ...

- 【转】Pycharm创建py文件时自定义头部模板

File->settings->Editor->File and Code Templates->Python Script #!/usr/bin/env python # - ...

- UDP服务器

用c#开发的一个UDP服务器.可以接收UDP的连接请求.给予响应. 代码已经上传至 GitHub,功能还会不断完善. 界面很丑.我很奇怪的是很少(到现在为止,我都没有见到过),所以界面一直做的不够酷炫 ...