SD协议-时序

1.SD Timing

- 时序主要体现在CMD和Response的时序

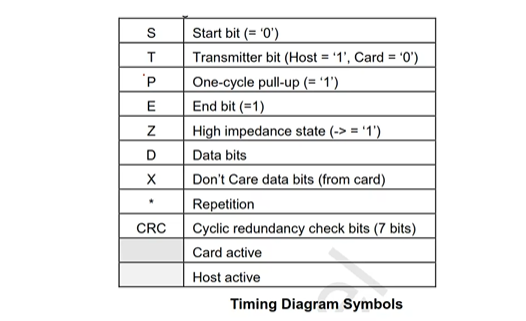

- S - 起始位,一直为0

- T - Transmitter,1表示CMD(发起端是Host),0表示Response(发起端是Card)

- P - pull up(上拉),当总线上所有的SD Host和SD Card都输出高阻态的时候,可以认为是总线没有驱动总线,此时可以给总线挂接一个上拉电阻或者下拉电阻,可以给总线一个固定的电压值,上拉为高电平(1),下拉为低电平(0)

- E - 结束位,一直为1

- Z - 高阻态,表示从总线断开,不驱动总线(作为Slave),SD Host发送命令的时候,SD Host作为Master,SD Card作为Slave,SD Card一定是输出z的

- D - Data

- X - 不需要关心的bit

- CRC - (循环冗余校验)用于数据传输的校验

- 灰色区域表示Card和Host有效

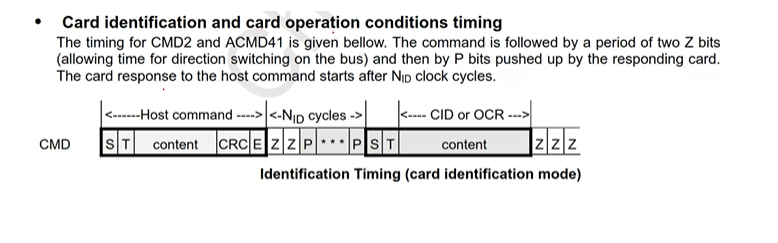

1.1 Card Identification

- P(=1)的个数取决于从Host Command到CID or OCR的时间NID

- 中间的两个Z:用于SD Host驱动总线和SD Card驱动总线的切换,总线控制权切换需要一定的时间

- 电容的充放电需要一定的时间,总线可以等效为一些电容

- 当SD Host发送完最后CMD的一个bit,发送一个Z,此时SD Host和SD Card都不驱动总线,经过两个Z之后,切换总线的控制权,经过一段上拉P,然后SD Card就可以返回数据了

- P是SD Card进行驱动的

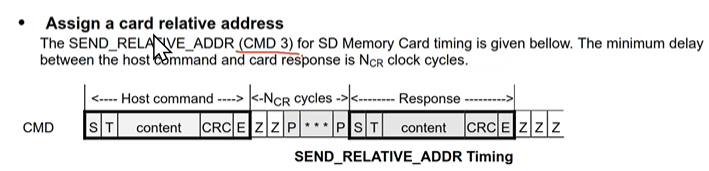

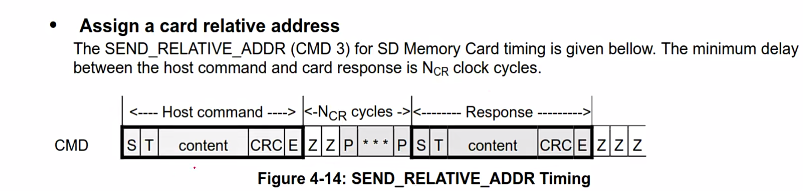

1.2 Assign a Card relative address

- CMD3 - SD Card会发布一个RCA,SD Card会转到data transfer state

- RCA值会附带在content中,SD Host收到content之后,保存RCA值,然后发送其他指令

- 不同指令之间的时间可以是不一样的

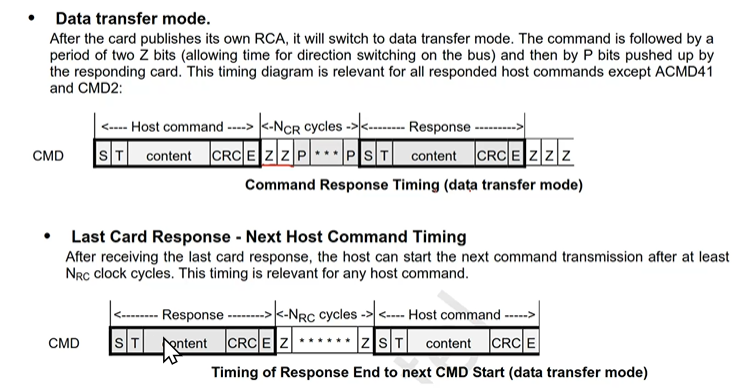

1.3 Data Transfer mode

- 发送完一条指令之后,接收完response之后,需要经过一个NRC之后才能进行发送下一条CMD

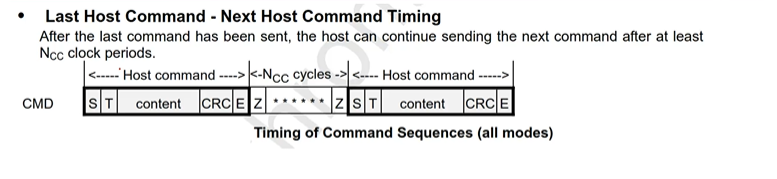

- 前一条CMD没有reponse,后面也可以跟一条CMD,中间要间隔Ncc

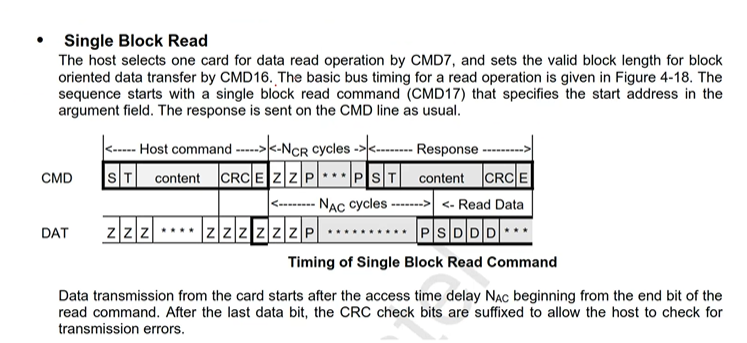

1.4 single block read

- 需要在CMD和Data总线上一起走

- CMD16 - 设置block length

- CMD17 - 经过一个NCR之后返回一个response

- Data可以和response并行返回,需要经过一个NAC时间access time(访问时间),可以返回第一笔数据(start bit)是0;所有的器件的输出都是z的话,总线会被上拉为1,P就是1,如果start bit是1的话,就无法区分这个1是前面的z还是P还是开始的数据1,所以start bit为0,当Data总线检测到start bit为0的时候,就表示SD Card返回response,在start bit下一个周期就可以采用返回的数据

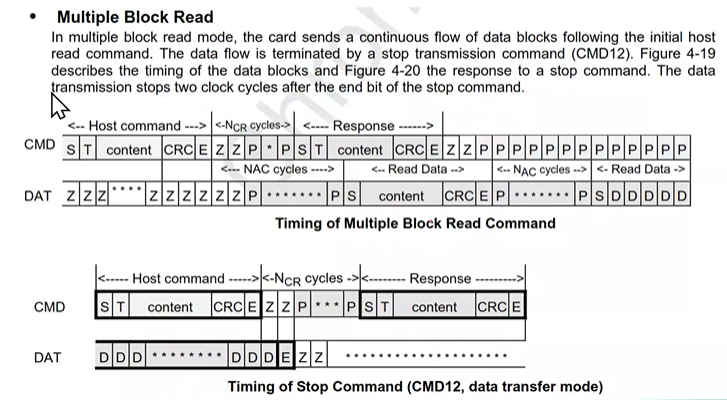

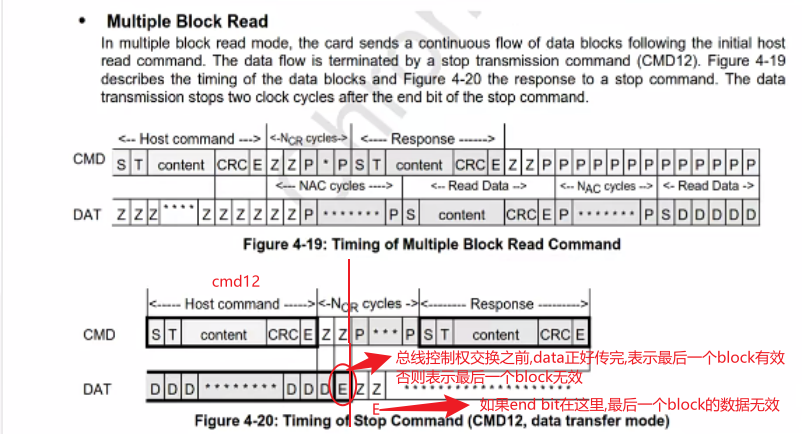

1.5 multiple block read

- single block read - block为512byte,数据多的时候,通过single block read读取效率不高,使用multiple block read

- CMD18 - 发送multiple block read请求

- 接收CMD到接收第一笔数据需要经过NAC的时间,返回start bit,然后返回数据,在返回第一个block数据之后,需要有一段时间的上拉(时间间隔),然后再进行下一个block的数据传输

- 在两次block传输之间的上拉时间NAC,在这段时间内,总线的控制权还在SD Card

- 读数据结束? -- 发送CMD12,告诉SD Card可以停止传输

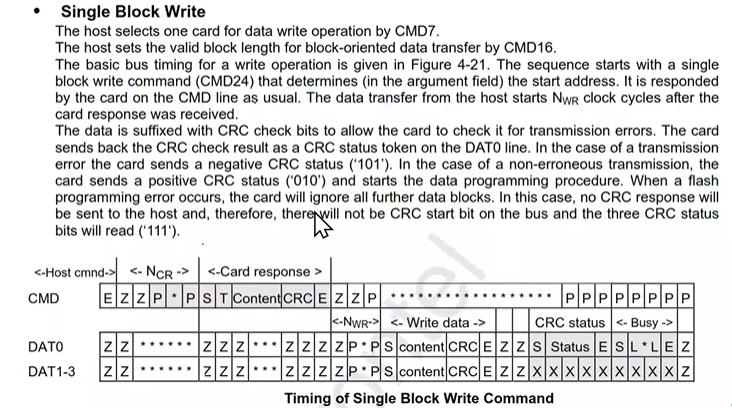

1.6 single block write

- SD Host先发起命令,然后经过NCR时间,接收到卡的response

- 然后经过NWR时间,这段时间是SD Host控制总线,然后可以发送写数据

- 为什么需要SD Card返回response?需要进行判断这个卡是不是能够正常接收命令,如果SD Host发送的命令存在错误或者CRC存在问题,response就是不正当的response,后面就没有必要发送数据了

- 发送完写数据和CRC,SD Card接收完数据之后,会返回CRC的状态,如果数据传输错误返回101,数据传输正确返回010,SD Host接收到错误信息,会重新发送一个请求

- Busy状态 - 写的步骤分为两步,有一个receiving data state,先将数据接受到buffer中,然后进入programming state,将buffer中的数据写入存储颗粒,如果当前buffer满了或者在programming state,会将Busy拉低(将总线Data0拉低),表示当前Card正在忙,不能接收下一笔读写操作,当SD Card写完之后,会将busy状态解除,SD Card发一个end bit,值为1

- Busy解除 - 一连串的0之后有一个1,busy解除之后才能进行下一条命令

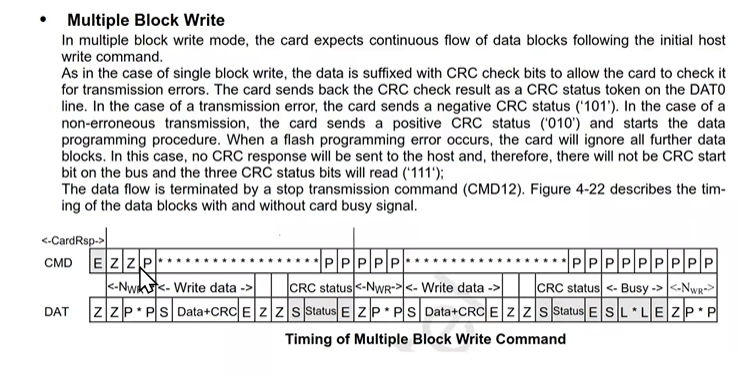

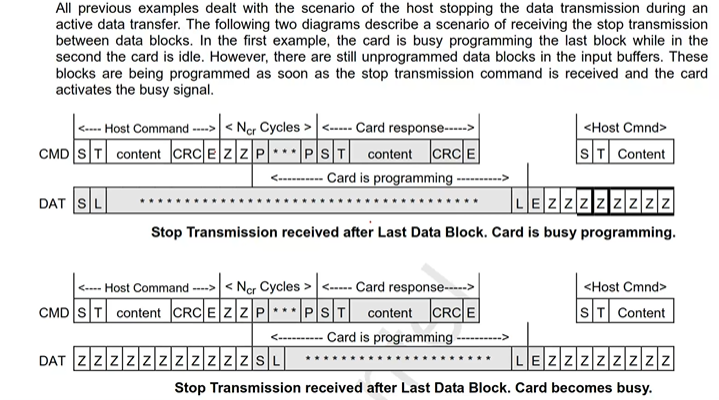

1.7 multiple block write

- 写操作与之前single block write时序一致

- 通过CMD12终止

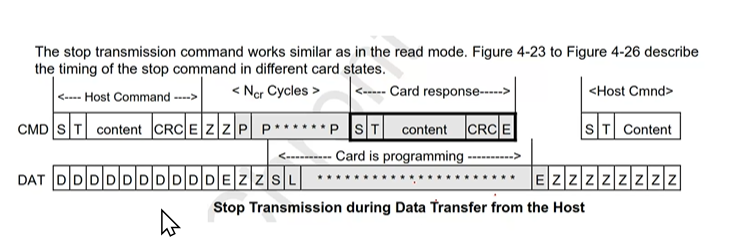

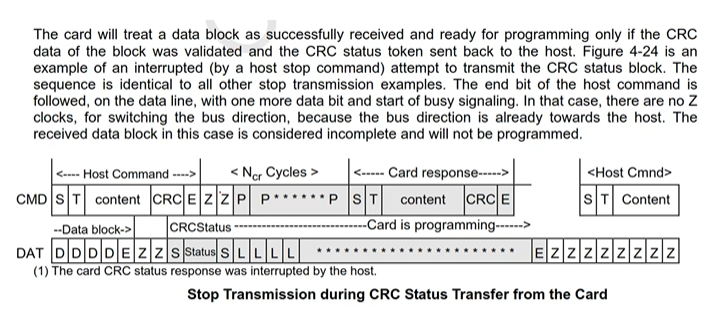

1.8 stop command

- 当前正在写数据,CRC之后,会将Data0拉为0,表示当前卡是busy状态,此时可以发送CMD12

- 在发送CMD12的时候可能存在不同的状态,比如CMD12的end bit正好处于CRC的接收端,如果当前卡正在进行programming,来了一个CMD12,并不会终止当前programming过程

- 如果当前CMD12的end bit处于Data传输过程中,会终止数据存储到SD Card的buffer中

- 在进行SD Card驱动设计的时候,数据发送完成之后才能发送CMD12

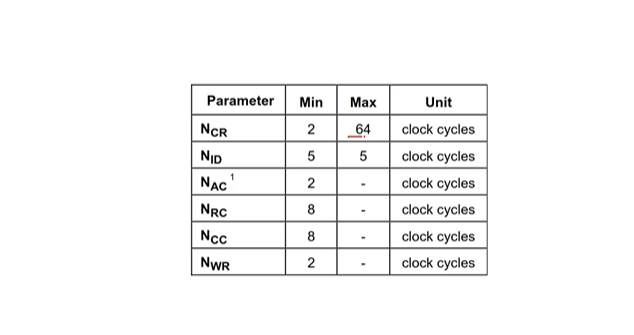

1.9 时序参数

- 在进行设计SD Host的时候,有最大周期数和最小周期数,使用计数器进行计数,如果超过64个cycle没有response,就可以发起下一个CMD

- NAC - access time,读访问时间,没有设置最大周期,但是最好还是设置一个时间,不能无限的进行等待,否则效率不高

- NRC - response 和 command之间

- NCC - command 和 command之间

- NWR - 在SD Host接收到response之后可以发送写数据

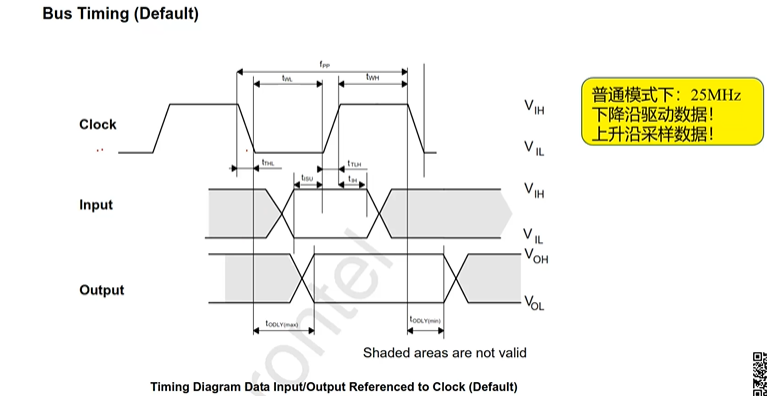

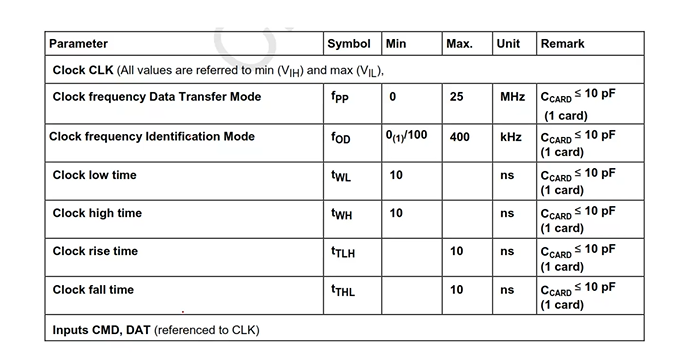

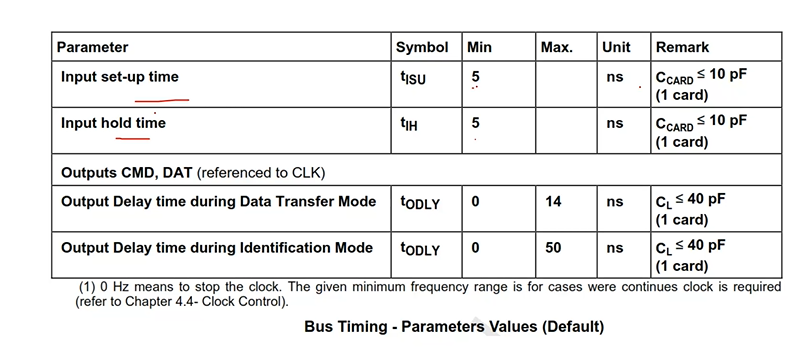

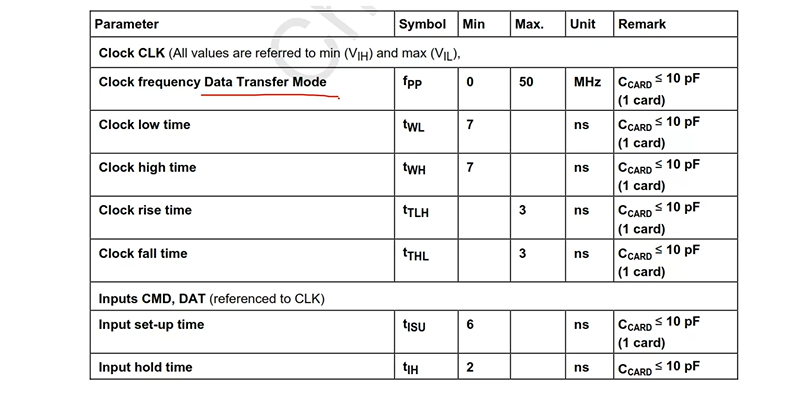

1.10 普通模式

- SD时序有两种模式,一种是普通模式,另外一种是高速模式

- 普通模式的时钟频率在0-25MHz,时钟频率比较低

- 需要在时钟的下降沿驱动数据,SD Card或者SD Host要发送一笔数据或者CMD,需要在时钟的下降沿驱动数据,数据真正在总线上被看到需要一定的时间,原因是设备从0变为1或者从1变为0需要一定的时间(电容的充电或者放电),这个时间与总线的负载和驱动能力有关

- thl - 时钟从高到低的时间

- tlh - 时钟从低到高的时间,时钟的变化不能太缓慢,保证时钟的质量

- twl - 低电平时间

- twh - 高电平时间

- fpp - 时钟周期

- toDLY(max) - 在采样之前数据需要保持稳定,如果数据延时时间过长,在采样的时候数据不稳定,会导致出错

- toDLY(min) - Hold时间,时间不能过小

- 时钟频率最小值是0,最大值是25MHz

- 卡识别模式下,不需要传输数据,只需要传输数据和响应,数据量比较小,频率较低

- 数据传输模式下,传输数据量比较大,频率比较高

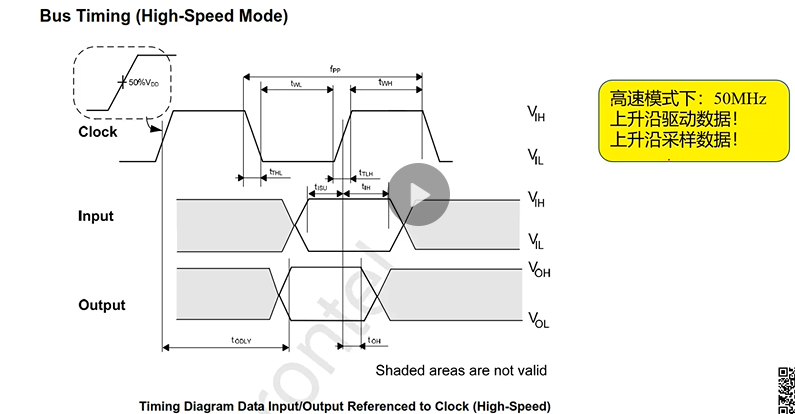

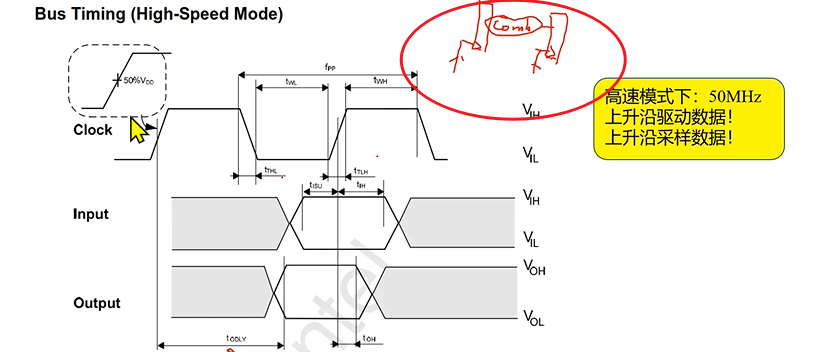

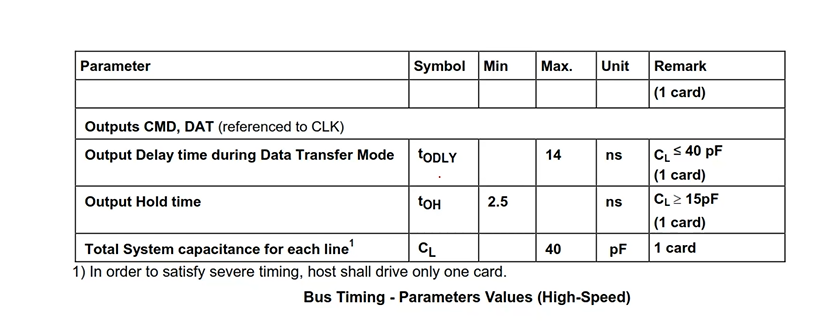

1.11 高速模式

- 上升沿驱动数据,上升沿采样数据

- toDLY - 类似与两个寄存器之间组合逻辑的延时,延时时间过大,在上升沿进行采样的时候,可能会采样到不稳定的值

- toH - 采样完成之后需要稳定的时间

- high speed mode只会对应于data transfer mode下,最大时钟频率是50MHz

- 单卡的负载电容40PF

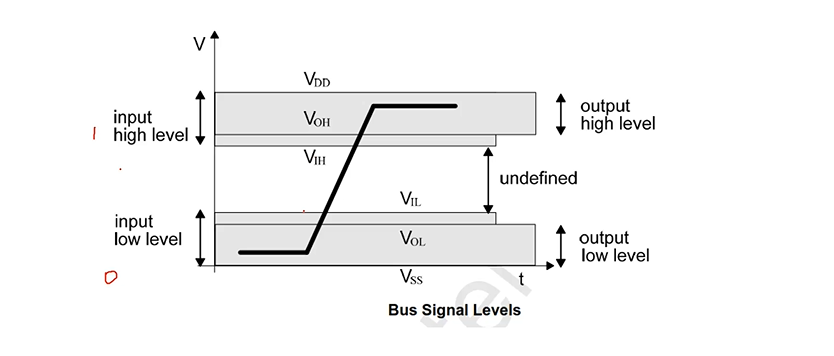

1.12 SD Bus Signal Level

- VoL - Vss -- 输出为0

- VoH - VDD - 输出为1

- Vss - VIL - 输入为0

- VIH - VDD - 输入为1

- "1"和"0"会有一定的容限

SD协议-时序的更多相关文章

- 模拟SPI协议时序

SPI是串行外设接口总线,摩托罗拉公司开发的一种全双工,同步通信总线,有四线制和三线制. 在单片机系统应用中,单片机常常是被用来当做主机(MASTER),外围器件被当做从机(SLAVE). 所以,在以 ...

- 模拟IIC协议时序

IIC是飞利浦公司开发的两线式串行总线,主要应用在单片机和外围电子器件之间的数据通讯. IIC总线优点是节约总线数,稳定,快速,是目前芯片制造上非常流行的一种总线,大多数单片机已经片内集成了IIC总线 ...

- 7816协议时序和采用UART模拟7816时序与智能卡APDU指令协议

7816时序 7816时一个比较早的老通讯时序了,最近项目上需要用UART模拟所以,简单学习时序. 时序比较简单,熟悉UART的一眼看着就像是串口的时序,只是他没有停止位,取而代之的就是保护时间gur ...

- STM32之SD卡

目录 一.SD卡概述 1.定义 2.容量等级 3.SD卡框图 4.SD卡与TF卡的区别 二. SD卡内部结构 1. SD卡内部结构简图 2. 存储阵列结构图 3.Buffer 4.“存储阵列Block ...

- [笔记]SD卡相关资料

ESD静电放电模块 我知道的flash分为两种NOR flash和NAND flash,NOR falsh容量一般为1~16M用于单片机代码存储,NAND flash最小的是8M最大的现在听说有90G ...

- 第36章 SDIO—SD卡读写测试

第36章 SDIO—SD卡读写测试 全套200集视频教程和1000页PDF教程请到秉火论坛下载:www.firebbs.cn 野火视频教程优酷观看网址:http://i.youku.com/f ...

- 第36章 SDIO—SD卡读写测试—零死角玩转STM32-F429系列

第36章 SDIO—SD卡读写测试 全套200集视频教程和1000页PDF教程请到秉火论坛下载:www.firebbs.cn 野火视频教程优酷观看网址:http://i.youku.com/f ...

- 裸机——SD卡

1.首先要对SD卡有个基础知识 (1) SD = nandflash + 主控IC. 主控IC负责了校验和坏块管理,所以SoC只需要依照时序就可以和SD卡上的主控IC进行数据交换等操作. (2) SD ...

- FPGA之SPI SD卡读操作

这几天在FPGA调试与SD通信,读SD卡里的图片,之前接触32时没有去研究过SD卡,不太熟悉操作流程,在网上找了很多资料,也看了几个32开发板的资料,但大多数都讲得不是特别清楚,只能瞎操作了一番,在别 ...

- [FatFs 学习] SD卡总结-SPI模式

SD卡为移动设备提供了安全的,大容量存储解决方法.它本身可以通过两种总线模式和MCU进行数据传输,一种是称为SD BUS的4位串行数据模式,另一种就是大家熟知的4线SPI Bus模式.一些廉价,低端的 ...

随机推荐

- django查询-列延迟加载only()、defer()

这玩意和sqlalchemy的几乎一样. only():只加载给定的列,其他列只有在使用时会发起二次查询 defer():不加载指定的列,刚好和only()相反. 实例: >>> r ...

- 从零玩转Docker之docker-compose-azdocker-compose

title: 从零玩转Docker之docker-compose date: 2023-04-04 17:39:40.699 updated: 2023-04-04 17:52:15.329 url: ...

- Linux-LVM 磁盘扩容

LVM技术详解:视频1.视频2.视频3 安装lvm2后才支持如下命令 yum install -y lvm2 序号 功能 PV物理卷命令 VG卷组命令 LV逻辑卷命令 01 扫描功能 pvscan v ...

- MyBatis 源码解析

本文源码解析针对的是 MyBatis 3.4.4 MyBatis 执行流程 第一阶段 MyBatis 在这个阶段获得 Mapper 的动态代理对象,具体逻辑如下图所示: 其中,Configuratio ...

- 开源:Taurus.DTC 微服务分布式事务框架,支持 .Net 和 .Net Core 双系列版本

前言: 在经过1年多的深思,十几年的框架编写技术沉淀下,花了近一个月的时间,终于又为 .Net 及 .Net Core 的微服务系列框架贡献当中的一个重要组件. 1.开源地址: https://git ...

- 国内AI大模型 VS chatgpt (20)-- H265/H264有何不同,h265有什么优势?

H265/H264有何不同,h265有什么优势? 文心一言: H.264和H.265是两种不同的视频编码标准,它们在压缩质量和带宽需求方面有所不同. H.264是一种高效的视频压缩标准,它的编码单位是 ...

- 26、Flutter中命名路由

Flutter 中的命名路由 main.dart中配置路由 void main() { runApp(MaterialApp( theme: ThemeData( appBarTheme: const ...

- 一文带你掌握OBS的两种常见的鉴权方式

摘要:本文就将带您了解OBS的两种常见的鉴权方式--Header携带签名和URL携带签名. OBS提供了REST(Representational State Transfer)风格API,支持您通过 ...

- 带你掌握Visual Studio Code的格式化程序

摘要:Visual Studio Code 中的所有语言都可以使用其中一种自动格式化程序进行格式化,并且 Python 扩展还支持 linter. 本文分享自华为云社区<Visual Studi ...

- iOS App的打包和上架流程

转载:iOS App的打包和上架流程 - 掘金 1. 创建账号 苹果开发者账号几种开发者账号类型 个人开发者账号 费用:99 美元/年(688.00元) 协作人数:仅限开发者自己 不需要填写公司的 ...