SV interface and Program3

时钟域的理解

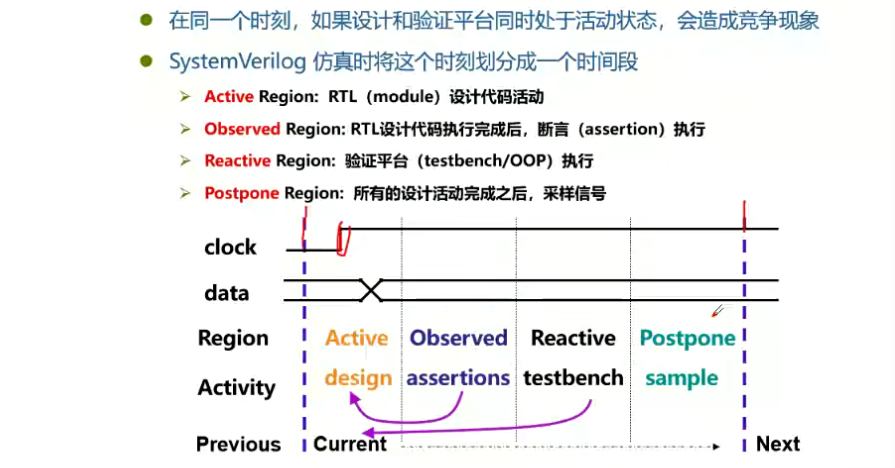

- 在仿真过程中,时钟跳变的一瞬间,CPU将时间域划分为不同的时钟域执行不同的代码

- 信号在芯片中都是金属丝,在进行跳变的时候都是电容的充放电过程,通常使用时钟上升沿进行模拟,而不使用时钟下降沿

// define the interface

interface mem_if(input wire clk);

logic reset; // logic可以作为输入和输出

logic we_sys;

logic cmd_valid_sys;

logic ready_sys;

logic [7:0] data_sys;

logic [7:0] addr_sys;

logic we_mem;

logic ce_mem;

logic [7:0] datao_mem;

logic [7:0] datai_mem;

logic [7:0] addr_mem;

// modport for meomry controller interface

modport ctrl (

input clk,reset,we_sys,cmd_valid_sys,addr_sys,datao_mem,

output we_mem,ce_mem,addr_mem,datai_mem,ready_sys,

ref data_sys

);

//modport for memory model interface

modport meomry (

input clk,reset,we_mem,ce_mem,addr_mem,datai_mem,

output datao_mem

);

// modport for test program

modport test (

input clk,ready_sys,

output reset,we_sys,cmd_valid_sys,addr_sys,

ref data_sys

);

endinterface

// memory model design with interface

// 传入modport接口

module memory_model (mem_if.memory mif);

// memory array

logic [7:0] mem [0:255];

//write logic

always @(posedge mif.clk)

if(mif.ce_mem && mif.we_mem) begin

mem[mif.addr_mem] <= mif.datai_mem;

end

// read logic

always @(posedge mif.clk)

if(mif.ce_mem && ~mif.we_mem) begin

datao_mem <= mem[mif.addr_mem];

end

endmodule

// memory controller design with interface

module memory_ctrl(mem_if.ctrl cif);

typedef enum {IDLE,WRITE,READ,DONE} fsm_t;

fsm_t state;

always @(posedge cif.clk)

if(cif.reset) begin

state <= IDLE;

cif.we_mem <= 0;

cif.ce_mem <= 0;

cif.addr_mem <= 0;

cif.datai_mem <= 0;

cif.data_sys <=0;

end

else begin

case(state)

IDLE: begin

cif.ready_sys <= 1'b0;

if(cif.cmd_valid_sys && cif.we_sys) begin

cif.addr_mem <= cif.addr_sys;

cif.datai_mem <= cif_data_sys;

cif.we_mem <= 1'b1;

cif.ce_mem <= 1'b1;

state <= WRITE;

end

if(cif.cmd_valid_sys && ~cif.we_sys) begin

cif.addr_mem <= cif.addr_sys;

cif.datai_mem <= cif_data_sys;

cif.we_mem <= 1'b0;

cif.ce_mem <= 1'b1;

state <= READ;

end

end

WRITE: begin

cif.ready_sys <= 1'b1;

if(~cif.cmd_valid_sys) begin

cif.addr_mem <= 8'b0;

cif.datai_mem <= 8'b0;

cif.we_mem <= 1'b0;

cif.ce_mem <= 1'b0;

state <= IDLE;

end

end

READ: begin

cif.ready_sys <= 1'b1;

if(~cif.cmd_valid_sys) begin

cif.addr_mem <= 8'b0;

cif.datai_mem <= 8'b0;

cif.we_mem <= 1'b0;

cif.ce_mem <= 1'b0;

cif.ready_sys <= 1'b1;

state <= IDLE;

cif.data_sys <= 8'bz;

end

end

endcase

end

endmodule

program test(mem_if.test tif);

initial begin

tif.reset <= 1;

tif.we_sys <= 0;

tif.cmd_valid_sys <= 0;

tif.addr_sys <= 0;

tif.data_sys <= 8'bz;

#100 tif.reset <= 0;;

for(int i = 0;i<4;i++) begin

@(posedge tif.clk)

tif.we_sys <= 1;

tif.cmd_valid_sys <= 1;

tif.addr_sys <= 1;

tif.data_sys <= $random;

@(posedge tif.clk)

tif.we_sys <= 0;

tif.cmd_valid_sys <= 0;

tif.addr_sys <= 0;

tif.data_sys <= 8'bz;

end

repeat(10) (posedge tif.clk)

// 此模块没有写完....

end

endprogram

module top();

logic clk = 0;

always #10 clk++;

mem_if u_miff(clk);

memory_ctrl u_ctrl(u_miff);

meomry_model u_model(u_miff);

test u_test(u_miff);

endmodule

SV interface and Program3的更多相关文章

- SV中的Interface和Program

Interface:SV中新定义的接口方式,用来简化接口连接,使用时注意在module或program之外定义interface,然后通过'include来添加进工程. interface arb_ ...

- SV学习之interface

普通的模块使用法:注意我们这里只实现了部分功能....不是完全的读写模块.... module mem_core( input logic wen, input logic ren, ...

- Cadence UVM基础视频介绍(UVM SV Basics)

Cadence关于UVM的简单介绍,包括UVM的各个方面.有中文和英文两种版本. UVM SV Basics 1 – Introduction UVM SV Basics 2 – DUT Exampl ...

- Libsvm:脚本(subset.py、grid.py、checkdata.py) | MATLAB/OCTAVE interface | Python interface

1.脚本 This directory includes some useful codes: 1. subset selection tools. (子集抽取工具) subset.py 2. par ...

- Shell_Oracle Erp和其他系统Interface资料传输通过Shell进行控制(案例)

2014-06-26 Created By BaoXinjian

- systemverilog interface

普通的模块使用法:注意我们这里只实现了部分功能....不是完全的读写模块.... module mem_core( input logic wen, input logic ren, ...

- Go语言学习笔记(四)结构体struct & 接口Interface & 反射

加 Golang学习 QQ群共同学习进步成家立业工作 ^-^ 群号:96933959 结构体struct struct 用来自定义复杂数据结构,可以包含多个字段(属性),可以嵌套: go中的struc ...

- SV class

SV中的class通过new来创建实例,new函数可以传递多个参数: packet P1: P1 = new:创建一个P1的对象: P2 = P1:P2也指向同一个对象: P2 = new P1:P ...

- sv命令空间 packge

SV中的module,interface,program,checker,都提供declaration空间,内部定义都local当前的那个scope,相互之间的building block不影响,不识 ...

- SV通过DPI调用C

Verilog与C之间进行程序交互,PLI(Programming Language Interface)经过了TF,ACC,VPI等模式. 使用PLI可以生成延时计算器,来连接和同步多个仿真器,并可 ...

随机推荐

- python操作mongodb基本使用

使用pymongo,具体可以参考官方文档: 语法上基本和原生mongodb是一样的,所以非常容易入手... https://pymongo.readthedocs.io/en/stable/tutor ...

- 数字孪生和VR结合能够为自身带来怎样的改变?

随着科技的不断发展,数字孪生和虚拟现实(VR)这两个前沿技术正在逐渐融合,为各行各业带来了前所未有的改变. 数字孪生技术本身已经可以高度还原现实世界,而VR技术则能通过头戴式设备,让用户沉浸在这个虚拟 ...

- C#如何对List中的Object进行排序

首先定义一个List类,这个类里面包含了Name和Total两个属性变量,下面就是针对这两个变量进行排序. public class Player { public string Name { get ...

- springboot整合mybatis步骤思路

/** * springboot整合mybatis步骤思路 * 依赖导入 * 建表 * 实体类 * mapper配置文件 * mapper接口 * yaml配置 * properties配置数据库连接 ...

- 牛客刷Java记录第四天

第一题,单选题 class Car extends Vehicle { public static void main (String[] args) { new Car(). run(); } pr ...

- --{module_name}_binary_host_mirror和--{module_name}_binary_site

--{module_name}_binary_host_mirror和--{module_name}_binary_site demo // .npmrc文件 sass_binary_site=htt ...

- Odoo16—级联删除

我们在odoo中构建业务系统模块的时候,通常会使用one2many.many2one或many2many将模型进行关联,由此产生的数据也会通过外键发生关联.那么在odoo中删除数据的时候,如何关联删除 ...

- 文心一言 VS 讯飞星火 VS chatgpt (56)-- 算法导论6.3 2题

文心一言 VS 讯飞星火 VS chatgpt (56)-- 算法导论6.3 2题 对于 BUILD-MAX-HEAP 中第 2行的循环控制变量 i 来说,为什么我们要求它是从A.length/2到1 ...

- WinDbg实践--入门篇

WinDbg从字面意思就是Windows+Debug的组合,即Windows平台上的调试工具,可以调试用户模式.内核模式.dump文件等,总之知道它的调试功能非常强大就行了.WinDbg调试命令分 ...

- 快来,这里有23种设计模式的Go语言实现

摘要:设计模式(Design Pattern)是一套被反复使用.多数人知晓的.经过分类编目的.代码设计经验的总结,使用设计模式是为了可重用代码.让代码更容易被他人理解并且保证代码可靠性. 本文分享自华 ...