基于STM32F407MAC与DP83848实现以太网通讯二(DP83848硬件配置以及寄存器)

参考内容:DP83848数据表

一、PHY DP83848功能模块图

DP83848的硬件模块主要为:

MII/RMII/SNI INTERFACES:用于与MAC数据传输的MII/RMII/SNI接口

Transmit BLOCK:数据发送模块,将从外部MAC(例如STM32ETH外设的MAC)接收到的数据,通过DAC模块和AUTO-MDIX发送值外部介质(光纤、水晶头、电缆等)

Rece BLOCK:数据接受模块,外部介质接受的数据通过AUTO-MDIX和ADC传输至Rece BLOCK,再通过MII/RMII接口传输至MAC(例如STM32ETH外设的MAC)

Boundary:调试模块,部分型号不支持,不使用悬空即可。

AUTO-MDIX:自动识别直连或交叉网线并自适应,可通过外部配置禁用。

LED Drivers:LED模块,用于指示工作状态以及工作模式,由外部以及寄存器控制。

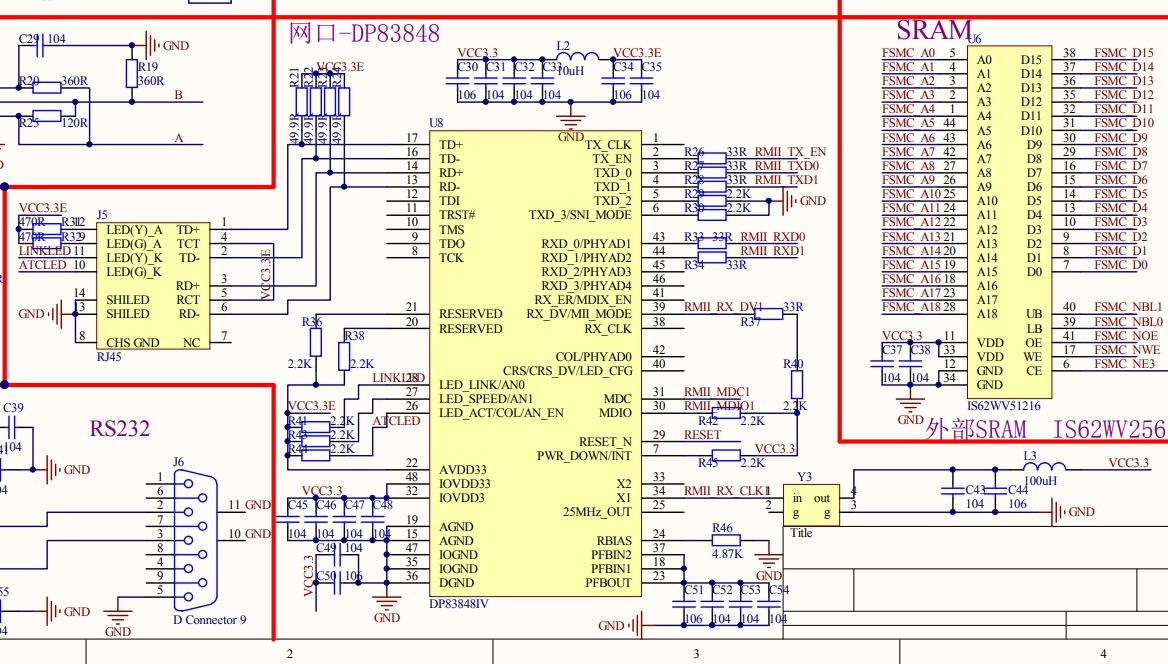

二、DP83848引脚配置(STM32F407ZGT6)

DP83848的所有复用引脚都有内部上拉或者下拉电阻,在配置引脚时,应使用2.2kΩ电阻连接GND或者Vcc配置。在接口选择方面这里选择RMII接口配置,要使用MII接口可参考DP83848参考手册。开发板使用的单片机为STM32F407ZGT6。

RMII接口(7Pin)

TX_EN(2):RMII发送启用,有效高电平输入表示 TXD [1:0] 上存在有效数据。(PG11)

TXD[0:1](3~4):RMII 发送数据,发送数据 RMII 输入引脚,TXD[1:0],此引脚接受同步至 50MHz 基准时钟的数据

TXD0(PG13),TXD1(PG14)

RX_DV(39):RMII同步接收数据有效信号。(PA7)

RXD[0:1](43~44):RMII接收数据信号引脚,与X1同步,50MHz。RXD0(PC4),RXD1(PC5)。

CRS_DV(40):RMII载波侦听/数据有效。(不接)

SMI接口(2Pin)

MDC(31):MDIO串行管理数据输入/输出接口同步时钟,也可以作为异步发送与接收时钟,最大时钟频率25MHz。(PC1)

MDIO(30):双向管理执行/信号接口。需要外置1.5KΩ上拉电阻。(PA2)

时钟接口(2Pin)

X1(34):RMII模式下必须连接50MHz,0.005%(+50ppm)的CMOS振荡源。(使用外部50MHz时钟源Y3)

CLK_OUT(25):由于RMII模式下X1输入50MHz参考时钟,此引脚能够给系统(STM32)提供相应的参考时钟源。(不使用)

LED接口(Pin3)

LED_LINK(28)、LED_SPEED(27)、LED_ACT/COL(26):LED接口的控制模式由PHY Control Register (PHYCR), address 0x19h控制。

Reset和Power Down

Reset_N(29):引脚拉低时间最少1μs,复位PHY芯片。(与单片机Reset复位按键为同意按键)

PWR_DOWN/INT(7):该被引脚拉低为Power Down模式(低功耗),中断模式时此引脚为开漏输出(内部弱上拉)。(拉高)

JTAG接口

TCK(8)、TDI(12)、TDO(9)、TMS(10)、TRST#(11),JTAG测试接口不使用不接。

三、DP83848外部配置选项

PHY地址配置PHY[0:4]:PHYAD0(COL)、PHYAD1(RXD_0)、PHYAD2(RXD_1)、PHYAD3(RXD_2)、PHYAD4(RXD_3)

系统复位,该地址(0<00000>~31<11111>)锁存在PHYCTRL寄存器。

地址0(0x00)时为MII隔离模式,配置隔离模式必须PHYAD0来选择,通过MDIO写入寄存器地址不会将PHY置于隔离模式。

PHYAD0内部为弱上拉电阻,PHYAD[4:1]内部为弱下拉电阻,因此默认的PHY地址为00001(0x01h)。

PHY配置地址示例00011(0x03h)

通讯速率与模式配置AN_EN(LED_ACT/COL)、AN_1(LED_SPEED)、AN_0(LED_LINK)

自动协商:当AN_EN为高电平时,将启用引脚AN_1与AN_0的自动协商功能(通告模式)。当AN_EN为低电平时,将启用引脚AN_1与AN_0的强制模式(Forced Mode)。引脚设定相应的值时通过2.2k电阻连接GND或Vcc。不要将引脚直接连接GND或Vcc,配置值将在硬件复位(Hardware Reset)时锁存在Basic Mode Control Register和e Auto_Negotiation Advertisement Register内。由于引脚内部默认上拉,因此默认值为111。

MII模式配置MII_MODE(RX_DV)、SNI_MODE(TXD_3)

确定MAC接口的工作模式默认状态为MII模式,当只有MII_MODE引脚拉高时为RMII模式(SNI_MODE内部下拉电阻)。(MII_MODE(39)拉高,SNI_MODE(6)拉低选择RMII模式)

LED配置LED_CFG(CRS)

LED_CF内置上拉电阻,默认为模式一,配置PHY Control Register(PHYCR)的LED_CFG[0]与LEDCFG[1]来实现LED模式选择。

Auto-MDIX模式配置MDX_EN(RX_ER)

默认状态使能MDIX,外接一个下拉电阻禁用Auto-MDIX功能。

10M/100Mb/s PMD接口RD-、RD+、TD-、TD+配置

RD-、RD+与TD-、TD+为两对差分输入/输出对,会被自动配置为相应的输入/输出100BASE-TX或10BASE-T信令。在AUTO-MDIX模式下,RD-、RD+可作为发送输出对,TD-、TD+可作为接收输入对。两对差分引脚需要接3.3V的直流偏置。

特殊连接(Special Connections)

RBIAS(24):Bias Resistor Connection需要使用一个4.87kΩ 1%的电阻通过RBIAS连接到GND

PFBOUT(23):Power Feedback Output ,需要将一个10μF(最好是钽电容)与一个0.1μF的并联并且靠近PFBOUT引脚,还需要将此引脚与PFNIN1和PFBIN2相连。

PFBIN1(18)、PFBIN2(37):Power Feedback Input,这两个引脚有PFBOUT供电,使用两个0.1μF的电容分别靠近PFBIN1与PFBIN2连接。

RESERVED(20,21):这些引脚必须使用AVDD33连接的2.2kΩ上拉电阻。

电源引脚配置

开发板上VCC3.3为I/O 3.3V电源,VCC3.3E为模拟3.3V电源,I/O地与模拟地共地。

四、PHY DP83848寄存器

具体寄存器配置参考:DP83848数据表 的寄存器章节-6.6 Memory

基于STM32F407MAC与DP83848实现以太网通讯二(DP83848硬件配置以及寄存器)的更多相关文章

- 搭建基于hyperledger fabric的联盟社区(二) --环境配置

接下来讲一下在本地测试区块链网络的过程.我要部署的是2peer+1orderer架构,所以需要准备三台虚拟机,为了方便起见可以先把一台配置好,然后复制出剩余两台即可.搭建虚拟机我用的是virtualb ...

- STM32F412应用开发笔记之五:结合W5500实现以太网通讯

因实际使用需求我们测试一下网络通讯,在NUCLEO-F412ZG测试板上没有以太网部分,我们选择外接一个W5500的实验板.W5500支持SPI接口通讯,DC3.3V供源.而NUCLEO-F412ZG ...

- 西门子S7系列以太网通讯处理器功能介绍

北京华科远创科技有限研发的远创智控型号ETH-YC模块适用于西门子S7-200/S7-300/S7-400.SMART S7-200.西门子数控840D.840DSL.合信.亿维PLC的PPI/MPI ...

- 西门子S7200/300/400以太网通讯处理器选型分类

北京华科远创科技有限研发的远创智控转以太网模块适用于西门子S7-200/S7-300/S7-400.SMART S7-200.西门子数控840D.840DSL.合信.亿维PLC的PPI/MPI/PRO ...

- 执行 $Gulp 时发生了什么 —— 基于 Gulp 的前端集成解决方案(二)

前言 文章 在windows下安装gulp —— 基于 Gulp 的前端集成解决方案(一) 中,已经完成对 gulp 的安装,由于是window环境,文中特意提到了可以通过安装 gitbash 来代替 ...

- 基于SignalR的消息推送与二维码描登录实现

1 概要说明 使用微信扫描登录相信大家都不会陌生吧,二维码与手机结合产生了不同应用场景,基于二维码的应用更是比较广泛.为了满足ios.android客户端与web短信平台的结合,特开发了基于Singl ...

- 基于webrtc的资源释放问题(二)

基于webrtc的资源释放问题(二) ——建立连接的过程中意外中断 应用背景: 我们在打电话的时候会不会遇到这种情况?打电话的时候未接通之前挂掉了电话,或者在接通之后建立的连接的过程中挂掉电话? 特别 ...

- 基于.net开发chrome核心浏览器【二】

原文:基于.net开发chrome核心浏览器[二] 一: 上一篇的链接: 基于.net开发chrome核心浏览器[一] 二: 相关资源介绍: chrome Frame: 让IE有一颗chrome的心, ...

- 基于FFMPEG的跨平台播放器实现(二)

基于FFMPEG的跨平台播放器实现(二) 上一节讲到了在Android平台下采用FFmpeg+surface组合打造播放器的方法,这一节讲一下Windows平台FFmpeg + D3D.Linux平台 ...

- 基于python的快速傅里叶变换FFT(二)

基于python的快速傅里叶变换FFT(二)本文在上一篇博客的基础上进一步探究正弦函数及其FFT变换. 知识点 FFT变换,其实就是快速离散傅里叶变换,傅立叶变换是数字信号处理领域一种很重要的算法. ...

随机推荐

- batch size设置技巧

1.什么是BatchSize Batch一般被翻译为批量,设置batch_size的目的让模型在训练过程中每次选择批量的数据来进行处理.Batch Size的直观理解就是一次训练所选取的样本数. Ba ...

- python截取字符串(字符串切片)

python中使用[]来截取字符串,语法: 字符串[起始位置:结束位置] 一.起始位置:结束位置 先看几个例子: s = 'python' print(s) #输出 python 直接输出字符串 #从 ...

- DevToys(开发工具) v1.0.2.1

从事开发工作的朋友们千万不要错过了!今天为大家带来的这款软件可以说是开发人员的必备工具,它就是DevToys软件!DevToys中包含了许多强大实用的开发工具,能够帮助用户将程序开发变得更加简单大大降 ...

- .NET Core开发实战(第7课:用Autofac增强容器能力)--学习笔记(下)

07 | 用Autofac增强容器能力:引入面向切面编程(AOP)的能力 如何获取没有命名的服务呢? // Autofac 容器获取实例的方式是一组 Resolve 方法 var service = ...

- Python脚本的输入输出

一.必备知识回顾和补充 1. Hello world回顾 1.输出文本,使用print函数输出文本. 2.让用户输入名字,然后输出带名字的问候语.使用input函数获取用户的输入,使用变量保存输入值. ...

- linux 搭建http文件服务器

1.安装httpd服务 yum -y install httpd 2.修改需要访问的文件路径 vi /etc/httpd/conf/httpd.conf ##默认是/var/www/html目录下的文 ...

- JS Leetcode 74. 搜索二维矩阵题解分析,二分法与坐标轴法

壹 ❀ 引 本题来自Leetcode74. 搜索二维矩阵,虽然难度是中等,但如果站在做出来的角度,你会发现其实并不难,题目描述如下: 编写一个高效的算法来判断 m x n 矩阵中,是否存在一个目标值. ...

- JVM之直接内存与非直接内存

直接内存 直接内存:概指系统内存,而非堆内存,不指定大小时它的大小默认与堆的最大值-Xmx参数值一致. 非直接内存: 也可以称之为堆内存,运行JVM都会预先分配一定内存,我们把JVM管理的这些内存称为 ...

- 实操开源版全栈测试工具RunnerGo安装(一)

Docker版安装文档 一.环境要求 1.1 部署服务器要求 操作系统:任何支持 Docker 的 Linux x86 CPU内存:最低要求 4C8G,推荐 8C16G 网络要求:可访问互联网 ...

- Go语言并发编程(1):对多进程、多线程、协程和并发、并行的理解

一.进程和线程 对操作系统进程和线程以及协程的了解,可以看看我前面的文章: 对进程.线程和协程的理解以及它们的区别:https://www.cnblogs.com/jiujuan/p/16193142 ...