用ModelSim仿真SDRAM操作

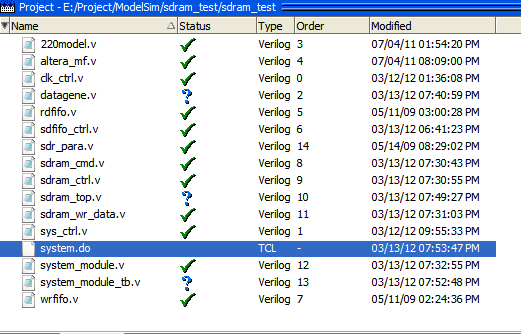

之前写了两篇关于Modelsim仿真的blog,其中模块管脚的命名可能让人觉得有些奇怪,其实不然,之前的两篇内容都是为了仿真SDRAM操作做铺垫的。

由于SDRAM的仿真过程相对比较复杂,也比较繁琐。故可能需要不止一篇blog来完成。

在开始仿真之前,如果对SDRAM原理以及时序不是很了解的朋友,推荐看一下如下这篇文章:

OK,下面正式开始仿真的过程。

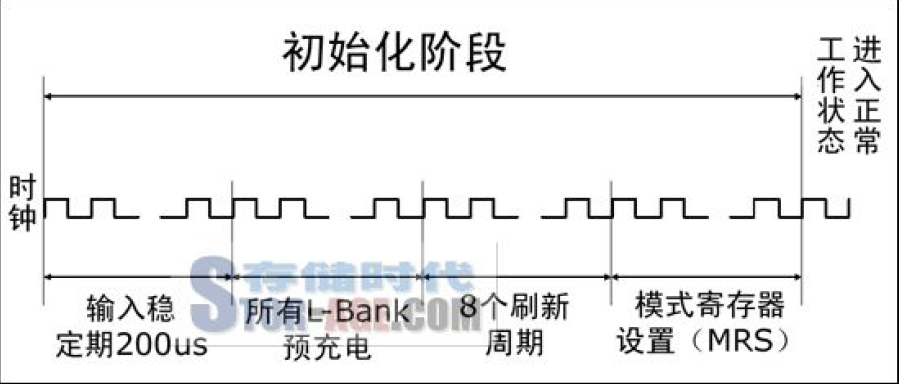

通过看内存技术指南,我们大概可以总结出SDRAM的工作过程:

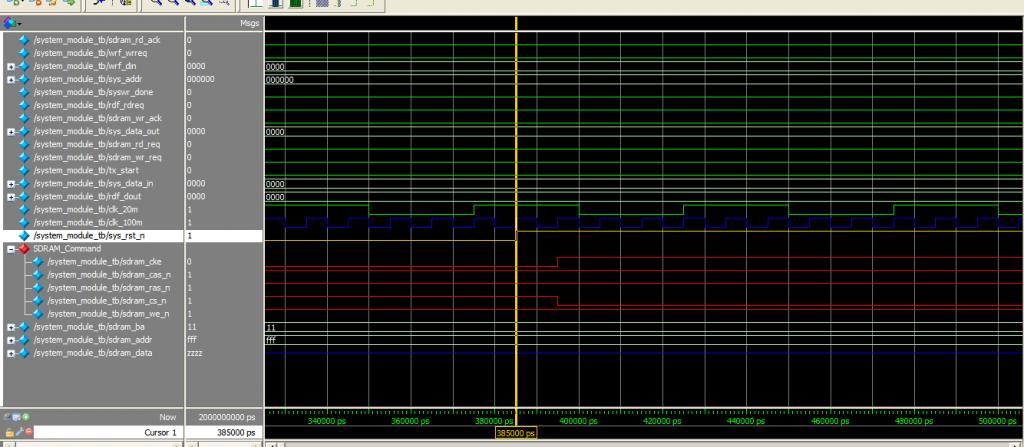

- 上电后进入200us的输入稳定期,空操作(NOP)

- 向SDRAM发送1次(1个时钟周期)预充电(precharge)命令,然后保持N个时钟周期NOP操作(N值可查芯片具体SDRAM芯片手册,与SDRAM工作的时钟频率有关)

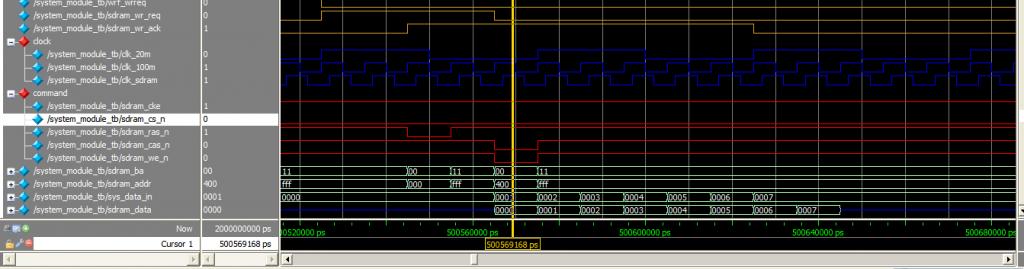

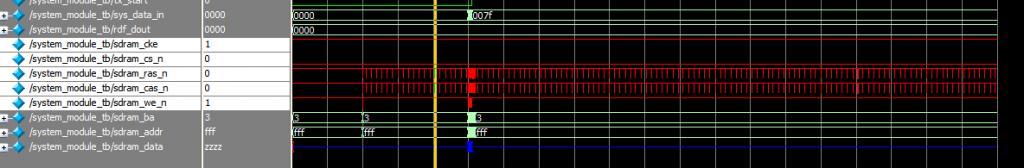

- 向SDRAM发送8次刷新(refresh)命令,具体发送过程后面会介绍

- 设置SDRAM工作模式寄存器

- 初始化完毕,可以开始读写操作

- 操作模式:突发读/突发写

- 潜伏期:两个时钟周期

- 突发传输方式:顺序

- 突发长度:8 (SDRAM芯片:4Block,1M*16bit,共64Mbit)故突发长度8代表每次读或写命令传输的数据量为8*位宽=8*16bit=128bit=16字节 (暂不考虑数据掩码DQM)

| CKE | CS_n | RAS_n | CAS_n | WE_n | |

| 空操作(NOP) | 1 | 0 | 1 | 1 | 1 |

| 预充电(PRE) | 1 | 0 | 0 | 1 | 0 |

| 刷新 | 1 | 0 | 0 | 0 | 1 |

| 行有效 | 1 | 0 | 0 | 1 | 1 |

| 开始读 | 1 | 0 | 1 | 0 | 1 |

| 开始写 | 1 | 0 | 1 | 0 | 0 |

| 模式寄存器设置 | 1 | 0 | 0 | 0 | 0 |

(PS: _n结尾的信号代表低电平有效)

8次刷新操作,对应命令10001,注意每个命令之后都有执行一段时间的NOP操作,这使得SDRAM有时间执行命令。

用ModelSim仿真SDRAM操作的更多相关文章

- ModelSim仿真入门

ModelSim仿真入门之一:软件介绍 编写这个教程之前,为了让不同水平阶段的人都能阅读,我尽量做到了零基础入门这个目标,所有的操作步骤都经过缜密的思考,做到了详细再详细的程度. 如果您是FPGA开发 ...

- cordic算法的verilog实现及modelsim仿真

1. 算法介绍 CORDIC(Coordinate Rotation Digital Computer)算法即坐标旋转数字计算方法,是J.D.Volder1于1959年首次提出,主要用于三角函数.双曲 ...

- 【黑金原创教程】【Modelsim】【第一章】Modelsim仿真的扫盲文

声明:本文为黑金动力社区(http://www.heijin.org)原创教程,如需转载请注明出处,谢谢! 黑金动力社区2013年原创教程连载计划: http://www.cnblogs.com/al ...

- 45.modelsim仿真include文件

modelsim仿真include文件会出现找不到文件的情况,这是因为include文件路径有两种,一种是相对路径,另一种是绝对路径. 相对路径: 如果 ‘include "primitiv ...

- 14.quartus联合modelsim仿真

在quartus调用modelsim仿真过程中,出现了一个错误,如下所示: Check the NativeLink log file I:/Quartus11.0/Myproject/testi_n ...

- 用Modelsim仿真QuartusII综合后网表时库的添加方法(转)

这两天做综合后仿真,发现FPGA器件库又不会加了,无奈上网找方法.说起来不好意思,很早就接触Modelsim这个仿真软件了,可是没有好好琢磨.把这两天找的方法贴出来,再加上自己的理解,以后忘了可以上博 ...

- modelsim 仿真时出现无限迭代(iteration reach limitation)的原因及其解决办法

modelsim 仿真时出现无限迭代(iteration reach limitation) 出现这种故障的原因: 一般都是代码里出现的组合逻辑无限循环或者组合逻辑A产生signal_A,signa ...

- modelsim仿真时让状态机波形显示状态的名字

在使用Verilog编写有限状态机等逻辑的时候,状态机的各个状态通常以参数表示(如IDLE等).当使用ModelSim仿真的时候,状态机变量在wave窗口中以二进制编码的形式显示,如下面所示,这种显示 ...

- ModelSim仿真教程

本文章详细介绍了怎样用ModelSim仿真Verilog,虽然只是很简单的一个二分频器的例子,但却正式小白入门所需要的. 本教程以ModelSim SE 10.4为例 1. 新建工程 file-> ...

随机推荐

- [NYOJ 15] 括号匹配(二)

括号匹配(二) 时间限制:1000 ms | 内存限制:65535 KB 难度:6 描述 给你一个字符串,里面只包含"(",")","[&qu ...

- 一个TextView使用不同的颜色

一个TextView使用不同的颜色: textview中首先需要已经有内容了 public static void ColorFormatTextView(TextView tv,int color, ...

- Servlet能读到JSessionID,读不到其它cookie问题

Servlet的Cookie值保存与获取 今天测试设置和获取Cookie遇到了一点小问题,很奇怪的问题: 把J2ee服务部署在本地 8080端口:访问任何一个服务时,如果客户端没有cookie,则下发 ...

- Linux使用sudo提权时,出现xx 不在 sudoers 文件中。此事将被报告。visudo 命令简单介绍。

在使用 sudo 临时提权时,出现:不在 sudoers 文件中.此事将被报告. 可以使用 visudo命令 来配置/etc/sudoers文件,将目标用户赋予使用sudo命令的能力. visudo命 ...

- SQL Server数据库大型应用解决方案总结【转】

[IT168 技术]随着互联网应用的广泛普及,海量数据的存储和访问成为了系统设计的瓶颈问题.对于一个大型的互联网应用,每天百万级甚至上亿的PV无疑对数据库造成了相当高的负载.对于系统的稳定性和扩展性造 ...

- [Android]在Dagger 2中Activities和Subcomponents的多绑定(翻译)

以下内容为原创,欢迎转载,转载请注明 来自天天博客:http://www.cnblogs.com/tiantianbyconan/p/6266442.html 在Dagger 2中Activities ...

- wuzhicms查找:当前页面使用的哪个文件

要查看这个地址的模版.http://www.wuzhicms.com/item-34-2-1.html 首先,我们的这个地址需要是动态的.而不是生成的静态地址. 打开文件: /www/configs/ ...

- Exception in thread "main" java.lang.ClassNotFoundException: 解决方法

[root@h1 ~]# hadoop jar W1.jar hdfs://h1:9000/hello hdfs://h1:9000/cmd Exception in thread "mai ...

- SignalR Supported Platforms -摘自网络

SignalR is supported under a variety of server and client configurations. In addition, each transpor ...

- H.264 Profile、Level、Encoder三张简图 (fps = AVCodecContext->time_base.den / AVCodecContext->time_base.num)

H.264 Profiles Profiles are sets of capabilities. If your black box only supports the Baseline profi ...