cyc_to_led

Entity: cyc_to_led

- File: cyc_to_led.v

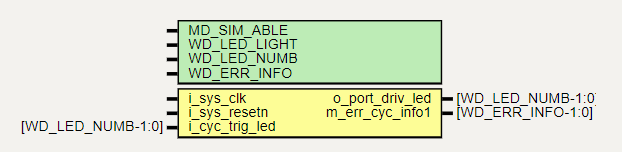

Diagram

Generics

| Generic name | Type | Value | Description |

|---|---|---|---|

| MD_SIM_ABLE | 0 | sim mode enable | |

| WD_LED_LIGHT | 27 | LED light span wdith | |

| WD_LED_NUMB | 3 | led width to true LED | |

| WD_ERR_INFO | 4 | error info note |

Ports

| Port name | Direction | Type | Description |

|---|---|---|---|

| i_sys_clk | input | system signals | |

| i_sys_resetn | input | ||

| i_cyc_trig_led | input | [WD_LED_NUMB-1:0] | trig signal |

| o_port_driv_led | output | [WD_LED_NUMB-1:0] | led port |

| m_err_cyc_info1 | output | [WD_ERR_INFO-1:0] | error info feedback |

Signals

| Name | Type | Description |

|---|---|---|

| r_cyc_trig_led | reg [WD_LED_NUMB-1:0] | cycle signal temp one clock |

| w_cyc_trig_led_pos | wire [WD_LED_NUMB-1:0] | detect cycle signal pos edge |

| r_led_light_cnt | reg [WD_LED_LIGHT-1:0] | counter for every LED driver |

Processes

- unnamed: ( @(posedge i_sys_clk) )

- Type: always

`timescale 1ns / 1ps

/*

Src Code

*/

// *******************************************************************************

// Company: Fpga Publish

// Engineer: FP

//

// Create Date: 2024/01/09 22:54:18

// Design Name:

// Module Name: cyc_to_led

// Project Name:

// Target Devices: ZYNQ7010 | XCZU2CG | Kintex7

// Tool Versions: 2021.1 || 2022.2

// Description:

// *

// Dependencies:

// *

// Revision: 0.01

// Revision 0.01 - File Created

// Additional Comments:

//

// *******************************************************************************

module cyc_to_led #(

//mode

parameter MD_SIM_ABLE = 0, //!sim mode enable

//number

parameter WD_LED_LIGHT = 27, //!LED light span wdith

parameter WD_LED_NUMB = 3, //!led width to true LED

//width

parameter WD_ERR_INFO = 4 //!error info note

)(

//!system signals

input i_sys_clk ,

input i_sys_resetn,

//!trig signal

input [WD_LED_NUMB-1:0] i_cyc_trig_led,

//!led port

output [WD_LED_NUMB-1:0] o_port_driv_led,

//!error info feedback

output [WD_ERR_INFO-1:0] m_err_cyc_info1

);

//========================================================

//function to math and logic

//========================================================

//localparam to converation and calculate

//========================================================

//register and wire to time sequence and combine

// ----------------------------------------------------------

// src signal solve

reg [WD_LED_NUMB-1:0] r_cyc_trig_led; //!cycle signal temp one clock

wire [WD_LED_NUMB-1:0] w_cyc_trig_led_pos;//!detect cycle signal pos edge

// ----------------------------------------------------------

// led cnt

reg [WD_LED_LIGHT-1:0] r_led_light_cnt [0:WD_LED_NUMB-1]; //!counter for every LED driver

//========================================================

//always and assign to drive logic and connect

// ----------------------------------------------------------

// src signal solve

always@(posedge i_sys_clk)

begin

if(!i_sys_resetn) //system reset

begin

r_cyc_trig_led <= 1'b0; //

end

else if(1) //

begin

r_cyc_trig_led <= i_cyc_trig_led; //

end

end

assign w_cyc_trig_led_pos = i_cyc_trig_led & (~r_cyc_trig_led);

// ----------------------------------------------------------

// led cnt

generate genvar i;

for(i = 0; i < WD_LED_NUMB; i = i + 1)

begin:FOR_WD_LED_NUMB

always@(posedge i_sys_clk)

begin

if(!i_sys_resetn) //system reset

begin

r_led_light_cnt[i] <= 1'b0; //

end

else if(w_cyc_trig_led_pos[i]) //every trig will reset counter

begin

r_led_light_cnt[i] <= 1'b0; //

end

else if(r_led_light_cnt[i][WD_LED_LIGHT-1])

begin

r_led_light_cnt[i] <= r_led_light_cnt[i];

end

else

begin

r_led_light_cnt[i] <= r_led_light_cnt[i] + 1'b1;

end

end

assign o_port_driv_led[i] = r_led_light_cnt[i][WD_LED_LIGHT-1];

end

endgenerate

//========================================================

//module and task to build part of system

//========================================================

//expand and plug-in part with version

//========================================================

//ila and vio to debug and monitor

endmodule

/*

补充说明(UTF-8)

- 基于LED监测周期信号

- 主要用于监测周期在ms级别的中断等物理信号

- 本模块暂时进行到源码设计阶段

*/

随机推荐

- Delphi 实现刘谦春晚魔术

看了博友的C# 实现刘谦春晚魔术很好,改成了delphi版的. 1 program Project1; 2 3 {$APPTYPE CONSOLE} 4 {$R *.res} 5 6 uses 7 S ...

- ORA-39087: Directory Name Is Invalid

说明 有时我们在Oracle数据库服务器执行expdp/impdp过程中会碰到这个错误:ORA-39087: Directory Name Is Invalid,意思是我们指定的directory参数 ...

- 苹果AppleMacOs最新Sonoma系统本地训练和推理GPT-SoVITS模型实践

GPT-SoVITS是少有的可以在MacOs系统下训练和推理的TTS项目,虽然在效率上没有办法和N卡设备相提并论,但终归是开发者在MacOs系统构建基于M系列芯片AI生态的第一步. 环境搭建 首先要确 ...

- 实操开源版全栈测试工具RunnerGo安装(二)Linux安装

手动安装(支持Linux.MacOS.Windows) Linux安装步骤 以debian系统为例,其他linux系统参考官方文档:https://docs.docker.com/engine/ins ...

- win32 - wsprintf和wvsprintf

前者很常用, 经常被用来转换为字符串或者拼接字符串. 例子: #include <Windows.h> #include <stdio.h> int main() { int ...

- 硬件开发笔记(十一):Altium Designer软件介绍、安装过程和打开pcb工程测试

前言 前面做高速电路,选择是阿li狗,外围电路由于读者熟悉AD,使用使用ad比较顺手,非高速电路就使用AD了,其实AD也可以做高速电路,由于笔者从13年开始做硬是从AD9开始的,所以开始切入AD做 ...

- PicGo如何设置阿里云图床

打开阿里云官网.注册并且登录.然后产品下拉列表里面通过搜索或者直接找到存储.对象存储OSS 默认你已经激活了,然后进入到控制台里面. 注意事项 Bucket名称需要全英文,不能有大写字母 服务器选国内 ...

- ZYNQ 裸机模式下修改默认uart端口

## 背景 调试ZYNQ 裸机code, 调用 printf()后在UART端口无法看到打印信息输出,查看原理图后发现,板子用的UART 1作为默认串口调试接口,UART 0分配给了RS485使用,因 ...

- signature hdr data: BAD, no. of btyes(9088) out of range 问题排查与解决方案

在使用yum工具安装gcc的时候,报出了signature hdr data: BAD, no. of btyes(9088) out of range 的问题 这是由于centos8中rpm工具存在 ...

- 【Azure App Services】多次操作App Service伸缩实例遇见限制操作记录

问题描述 多次操作App Services,进行实例数的变化.达到限制后遇见报错: 错误的具体描述为: { "status": "Failed", " ...