Vivado中xilinx_BRAM IP核使用

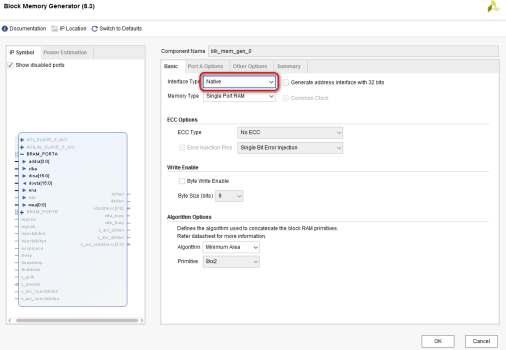

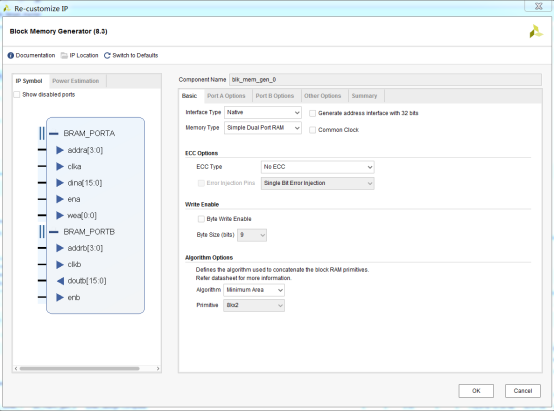

Vivado2017.2 中BRAM版本为 Block Memory Generator Specific Features 8.3

BRAM IP核包括有5种类型:

Single-port RAM 单端口RAM

Simple Dual-port RAM 简单双端口RAM(A写数据B读数据)

True Dual-port RAM 双端口RAM

Single-por ROM 单端口ROM

Dual-port ROM 双端口ROM

BRAM核支持两种总线形式的输入输出:Native or AXI4

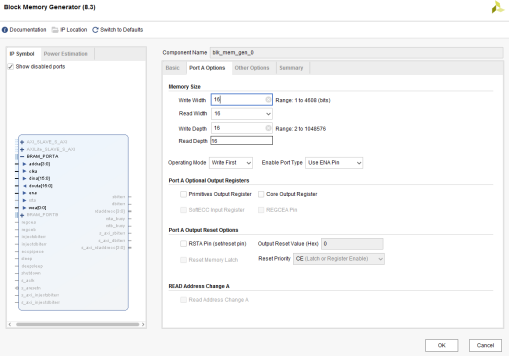

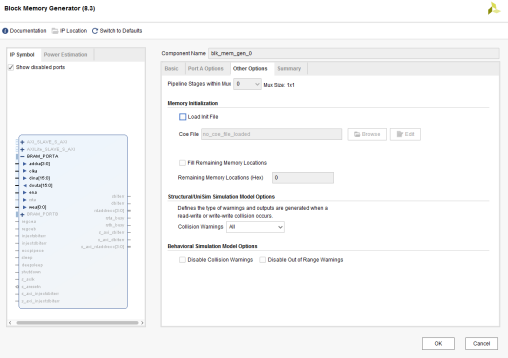

以下图配置为例:Single-port RAM

Testbench 测试代码如下:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2018/11/21 15:52:48

// Design Name:

// Module Name: test_bench_BRAM

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module test_bench_BRAM(

);

reg[15:0] mem1_re[0:15]; //输入数据存储器

integer i;

// blk_mem_gen_0 inputs

reg clka;

reg ena;

reg wea;

reg[3:0] addra;

reg[15:0] dina;

// blk_mem_gen_0 outputs

wire[15:0] douta;

blk_mem_gen_0 blk_mem_gen_m0

(

.clka(clka), //BRAM 输入时钟信号

.ena(ena), //BRAM 时钟使能信号

.wea(wea), //写使能信号

.addra(addra), //地址信号

.dina(dina), //数据输入接口 写入

.douta(douta) //数据输出接口 读出

);

always #5 clka = ~clka;

initial $readmemh("D:/fpga/fft1/stimulus1_24bit.dat",mem1_re); //数据是[1 2 3 4 5 6 7 8 9]

initial begin

clka = 0;

ena = 0;

wea = 0;

addra = 0;

dina = 0;

#150 ena = 1;

begin

for(i=0;i<16;i=i+1) begin

#10 wea <= 1;

addra <= i;

/*if(i == 0) begin

addra <= 0;

end

else if (i == 1) begin

addra <= 1;

end

else if(i == 2) begin

addra <= 2;

end

else if(i == 3) begin

addra <= 3;

end

else begin

wea <= 0;

end*/

dina <= {mem1_re[i]};

if(i == 15) begin

dina <= 0;

wea <= 0;

end

$display("mem_a[%d] = %h", i, mem1_re[i]);

end

end

#40000 $finish;

end

endmodule

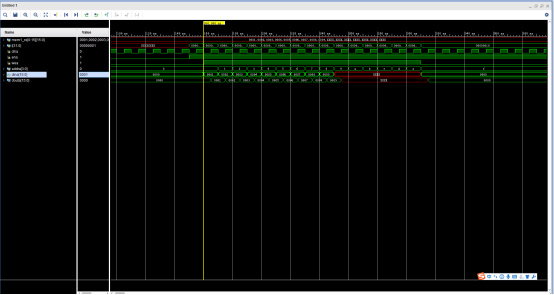

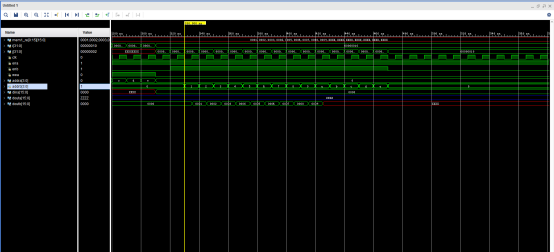

仿真结果如下:

配置为simple dual port ram

Testbench

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2018/11/21 15:52:48

// Design Name:

// Module Name: test_bench_BRAM

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module test_bench_BRAM(

);

reg[15:0] mem1_re[0:15]; //输入数据存储器

integer i;

integer j;

// blk_mem_gen_0 inputs

reg clk;

reg ena;

reg enb;

reg wea;

reg[3:0] addra;

reg[3:0] addrb;

reg[15:0] dina;

// blk_mem_gen_0 outputs

wire[15:0] douta;

wire[15:0] doutb;

/*****单端口 网络配置的IP核

blk_mem_gen_0 blk_mem_gen_m0

(

.clka(clka), //BRAM 输入时钟信号

.ena(ena), //BRAM 时钟使能信号

.wea(wea), //写使能信号

.addra(addra), //地址信号

.dina(dina), //数据输入接口 写入

.douta(douta)

);*******/

/**************简单双端口RAM A进B出**************/

blk_mem_gen_0 blk_mem_gen_m0

(

.clka(clk), //BRAM 输入时钟信号

.ena(ena), //BRAM 时钟使能信号

.wea(wea), //写使能信号

.addra(addra), //地址信号

.dina(dina), //数据输入接口 写入

.clkb(clk), //BRAM 输入时钟信号

.enb(enb), //BRAM 时钟使能信号

.addrb(addrb), //地址信号

.doutb(doutb)

);

always #5 clk = ~clk;

initial $readmemh("D:/fpga/fft1/stimulus1_24bit.dat",mem1_re);

initial begin

clk = 0;

ena = 0;

enb = 0;

wea = 0;

addra = 0;

addrb = 0;

dina = 0;

#150 ena = 1;

begin

for(i=0;i<16;i=i+1) begin

#10 wea <= 1;

addra <= i;

dina <= {mem1_re[i]};

if(i == 15) begin

dina <= 0;

wea <= 0;

addra <= 0;

end

$display("mem_a[%d] = %h", i, mem1_re[i]);

end

for(j=0;j<16;j=j+1) begin

#10 addrb <= j;

enb <= 1;

if( j == 15) begin

enb <= 0;

addrb <= 0;

end

end

end

#40000 $finish;

end

endmodule

测试仿真结果:

Vivado中xilinx_BRAM IP核使用的更多相关文章

- Vivado中xilinx_courdic IP核(求exp指数函数)使用

由于Verilog/Vhdl没有计算exp指数函数的库函数,所以在开发过程中可利用cordic IP核做exp函数即e^x值: 但前提要保证输入范围在(-pi/4—pi/4) 在cordic核中e^x ...

- Vivado 调用自定义IP核

关于Vivado如何创建自定义IP核有大量的参考文章,这里就不多加阐述了,本文目的主要是解决如何在新建工程中引用其它工程已经自定义封装好的IP核,从而实现自定义IP核的灵活复用. 举个例子,我们的目标 ...

- 转:基于 xilinx vivado 的PCIE ip核设置与例程代码详解

连接:https://blog.csdn.net/u014586651/article/details/103826967#comments

- IP核的使用(Vivado中的调用,product guide的查询阅读 ,引脚的设置(位宽,个数,算法等),coe文件的初始化 )

IP核:Intellectual Property core ,即知识产权核.每个IP核可以实现特定功能,我们在设计一个东西时可以直接调用某个IP核来辅助实现功能. 存在形式:HDL语言形式,网表形式 ...

- Xilinx Vivado的使用详细介绍(3):使用IP核

ilinx Vivado的使用详细介绍(3):使用IP核 Author:zhangxianhe IP核(IP Core) Vivado中有很多IP核可以直接使用,例如数学运算(乘法器.除法器.浮点运算 ...

- modelsim 独立仿真vivado的IP核及仿真脚本

Modelsim独立仿真vivado的IP 最近一直在做local dimming项目的FPGA硬件实现,算法的其中一步就是直方图统计,即数字图像的某一灰度级的像素数,这个直方图的源码找了半天才搞到, ...

- IP核之初——FIFO添加以太网MAC头部

本文设计思路源自明德扬至简设计法.在之前的几篇博文中,由于设计比较简单,所有的功能都是用verilogHDL代码编写实现的.我们要学会站在巨人的肩膀上,这时候就该IP核登场了! 说白了,IP核就是别人 ...

- FIFO IP核

转载: 说白了,IP核就是别人做好了的硬件模块,提供完整的用户接口和说明文档,更复杂的还有示例工程,你只要能用好这个IP核,设计已经完成一半了.说起来容易,从冗长的英文文档和网上各个非标准教程中汲取所 ...

- System Generator 生成IP核在Vivado中进行调用

System Generator 生成IP核在Vivado中进行调用 1.首先在Simulink中搭建硬件模型 2.查看仿真结果 3.资源分析与时序分析 4.启动vivado,关联生成的IP核 5.调 ...

随机推荐

- java实现Kafka生产者示例

使用java实现Kafka的生产者 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 3 ...

- Ubunt 安装mysql

apt-get install mysql-client-core-5.6apt-get install mysql-client-5.6apt-get install mysql-server-5. ...

- python汉字转拼音

上代码: #!/usr/bin/env python # -*- coding:utf-8 -*- """ Author:cleverdeng E-mail:clverd ...

- 【转】证书的应用之一 —— TCP&SSL通信实例及协议分析(下)

原文链接 前面两部分分别讲解了如何在.net程序中使用SSL实现安全通信以及SSL的通信过程,并通过抓包工具具体分析了ssl的握手过程,本文通过一个demo来模拟ssl协议,在TCP之上实现自己的安全 ...

- 产品经理都知道MVP,但是它可能不再是产品研发最好的模型了

产品经理都知道MVP,但是它可能不再是产品研发最好的模型了 孟小白Aspire • 2017-09-01 • 汽车交通 要简单.讨喜.完整,不要最小可行性产品.这对创业公司的第一个产品来说很重要. M ...

- 转:winform 安装包(很详细)

winform安装项目.安装包的制作.部署 ① 1,解决方案—添加—新建项目—其他项目类型—安装和部署—安装项目,输入名称Setup,点“确定” 2,添加主输出:单击左侧“应用程序文件夹”,右侧右键— ...

- model.object对象查询过滤、增删改、Q

vm.objects.all()[:10] #获得前10个对象,不支持负索引 vm.objects.get(name='vmname') vm.objects.filter(name='vmname' ...

- asp.net core中DockerFile文件中的COPY

今天在ubuntu系统中使用docker部署asp.net core时遇到了一个问题,docker build 的时候总会在最后一步提示 lstat obj/Docker/publish: no su ...

- MVC中使用EF的技巧集(一)

一.建好数据库后,向项目中添加数据模型. 1.右键点击“Models” 文件夹,选择“添加”,再选择“添加新项”. 2.在“添加新项”窗口,选择左边的“数据”,然后再在右边选择“ADO.NET 实体数 ...

- zabbix日常监控项java(四又分之一)

因zabbix自带监控JMX的模板通用性差的问题,需要我们自己新建一个属于自己的模板,于是本文就出现了.... 大部分都是参考网上其他博主的文档,在此作为梳理.总结:以方便自己日后使用查询.