[转]FPGA入门——basys2开发板的伪随机gold码的生成

本文原创,转载请注明出处:http://www.cnblogs.com/risten/p/4166169.html

1.系统原理

通过频率控制字选择相位步进,产生访问ROM的地址,进而控制DAC的输出波形与频率。整个系统由时钟生成、相位累加、ROM、DAC组成。限于basys2开发板的限制,本次将输出DAC替换为8个led灯显示。

2.系统设计

2.1 时钟生成

1 library IEEE;

2 use IEEE.STD_LOGIC_1164.ALL;

3 use IEEE.STD_LOGIC_ARITH.ALL;

4 use IEEE.STD_LOGIC_UNSIGNED.ALL;

5

6 entity clock_gen is

7 port (

8 clk : IN STD_LOGIC;

9 rst : IN STD_LOGIC;

10 clka : OUT STD_LOGIC

11 );

12 end clock_gen;

13

14 architecture Behavioral of clock_gen is

15 signal cnt : INTEGER;

16 signal clk_reg : STD_LOGIC;

17

18 begin

19 clka<=clk_reg;

20 process(clk,rst)

21 begin

22 if (rst='0') then

23 cnt<=0;

24 clk_reg<='0';

25 elsif (clk'event and clk='1') then

26 if (cnt=250000) then --生成时钟为0.01s

27 cnt<=0;

28 clk_reg<=not clk_reg;

29 else

30 cnt<=cnt+1;

31 end if;

32 end if;

33 end process;

34 end Behavioral;

2.2相位累加(地址生成)

1 library IEEE;

2 use IEEE.STD_LOGIC_1164.ALL;

3 use IEEE.STD_LOGIC_ARITH.ALL;

4 use IEEE.STD_LOGIC_UNSIGNED.ALL;

5

6 entity phase_adder is

7 port(

8 clka : IN STD_LOGIC;

9 rst : IN STD_LOGIC;

10 f_level : IN STD_LOGIC_VECTOR(6 DOWNTO 0);

11 addr : OUT STD_LOGIC_VECTOR(9 DOWNTO 0)

12 );

13 end phase_adder;

14

15 architecture Behavioral of phase_adder is

16 signal cnt : STD_LOGIC_VECTOR(9 DOWNTO 0);

17

18 begin

19 addr<=cnt;

20 process(clka,rst,f_level)

21 begin

22 if (rst='0') then

23 cnt<=(others=>'0');

24 elsif (clka'event and clka='1') then

25 cnt<=cnt+f_level;

26 end if;

27 end process;

28

29 end Behavioral;

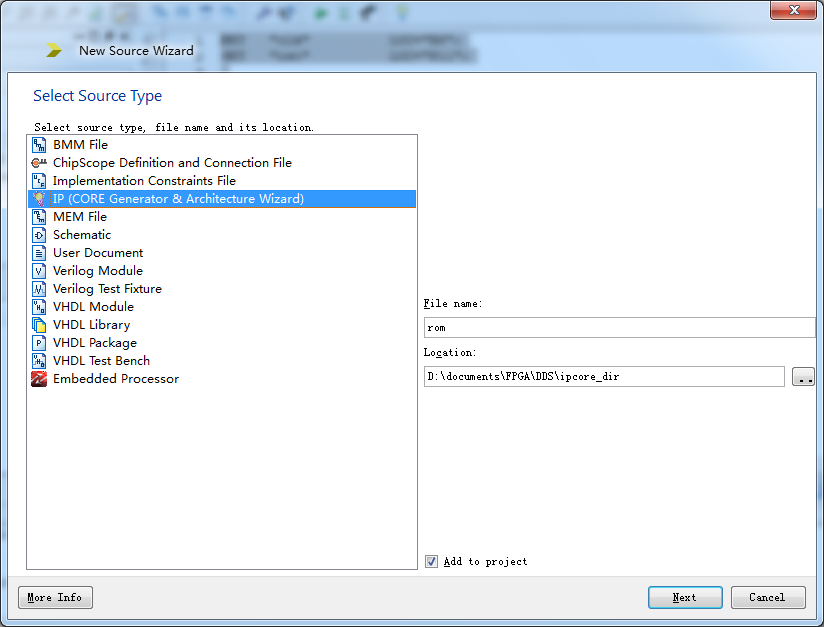

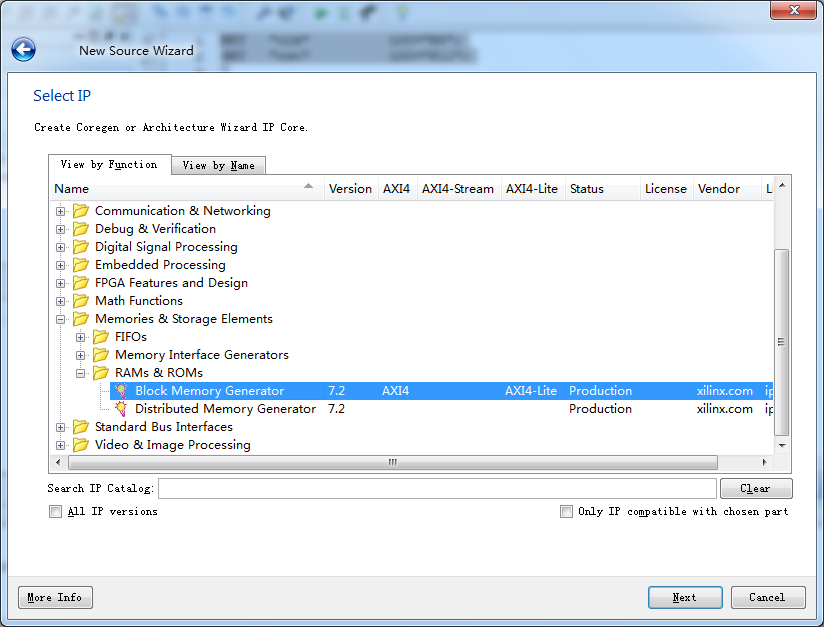

2.3 ROM

新建源文件选择IP核

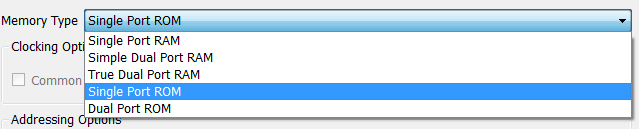

存储类型

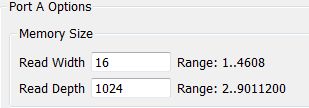

存储大小

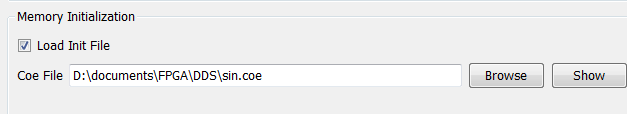

数据初始化

正弦余弦初始化coe文件的生成(使用matlab)

1 clc

2 clear all

3 close all

4 x = linspace(0, 2*pi ,1024); % 在区间[0,2*pi]之间等间隔地取1024个点

5 y_cos = cos(x);

6 y_sin = sin(x);

7 y_cos = y_cos * 2^15;

8 y_sin = y_sin * 2^15;

9 fid = fopen('D:/cos.coe','wt');

10 fprintf(fid, '%5.0f,\n' , y_cos);

11 fclose(fid);

12 fid = fopen('D:/sin.coe','wt');

13 fprintf(fid, '%5.0f,\n' , y_sin);

14 fclose(fid);

用记事本在生成文件开头添加

并把最后的结尾换为 ; 号

存储器选项都设置完毕后点击generate即可。

2.4 LED显示(DAC)

1 library IEEE;

2 use IEEE.STD_LOGIC_1164.ALL;

3 use IEEE.STD_LOGIC_ARITH.ALL;

4 use IEEE.STD_LOGIC_UNSIGNED.ALL;

5 use IEEE.STD_LOGIC_SIGNED.ALL;

6

7 entity led is

8 port (

9 data : IN STD_LOGIC_VECTOR(15 DOWNTO 0);

10 led_seg : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

11 );

12 end led;

13

14 architecture Behavioral of led is

15 begin

16 process(data)

17 begin

18 if (signed(data)<-24576) then

19 led_seg<="10000000";

20 elsif (signed(data)<-16348) then

21 led_seg<="01000000";

22 elsif (signed(data)<-8192) then

23 led_seg<="00100000";

24 elsif (signed(data)<0) then

25 led_seg<="00010000";

26 elsif (signed(data)<8192) then

27 led_seg<="00001000";

28 elsif (signed(data)<16348) then

29 led_seg<="00000100";

30 elsif (signed(data)<24576) then

31 led_seg<="00000010";

32 else

33 led_seg<="00000001";

34 end if;

35 end process;

36

37 end Behavioral;

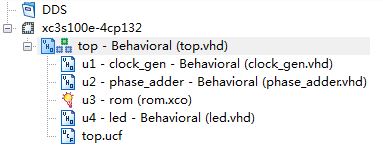

2.5 顶层设计TOP

1 library IEEE;

2 use IEEE.STD_LOGIC_1164.ALL;

3

4 entity top is

5 port (

6 clk : IN STD_LOGIC;

7 rst : IN STD_LOGIC;

8 f_level : IN STD_LOGIC_VECTOR(6 DOWNTO 0);

9 led_seg : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

10 );

11 end top;

12

13 architecture Behavioral of top is

14 COMPONENT clock_gen

15 PORT (

16 clk : IN STD_LOGIC;

17 rst : IN STD_LOGIC;

18 clka : OUT STD_LOGIC

19 );

20 END COMPONENT;

21 COMPONENT phase_adder

22 PORT (

23 clka : IN STD_LOGIC;

24 rst : IN STD_LOGIC;

25 f_level : IN STD_LOGIC_VECTOR(6 DOWNTO 0);

26 addr : OUT STD_LOGIC_VECTOR(9 DOWNTO 0)

27 );

28 END COMPONENT;

29 COMPONENT rom

30 PORT (

31 clka : IN STD_LOGIC;

32 addra : IN STD_LOGIC_VECTOR(9 DOWNTO 0);

33 douta : OUT STD_LOGIC_VECTOR(15 DOWNTO 0)

34 );

35 END COMPONENT;

36 COMPONENT led

37 PORT (

38 data : IN STD_LOGIC_VECTOR(15 DOWNTO 0);

39 led_seg : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

40 );

41 END COMPONENT;

42

43 signal clka : STD_LOGIC;

44 signal addr : STD_LOGIC_VECTOR(9 DOWNTO 0);

45 signal data : STD_LOGIC_VECTOR(15 DOWNTO 0);

46

47 begin

48 u1 : clock_gen PORT MAP (clk,rst,clka);

49 u2 : phase_adder PORT MAP (clka,rst,f_level,addr);

50 u3 : rom PORT MAP (clka,addr,data);

51 u4 : led PORT MAP (data,led_seg);

52

53 end Behavioral;

3. 引脚定义

1 NET "clk" LOC="B8";

2 NET "rst" LOC="P11";

3

4 NET "f_level<0>" LOC="L3";

5 NET "f_level<1>" LOC="K3";

6 NET "f_level<2>" LOC="B4";

7 NET "f_level<3>" LOC="G3";

8 NET "f_level<4>" LOC="F3";

9 NET "f_level<5>" LOC="E2";

10 NET "f_level<6>" LOC="N3";

11

12 NET "led_seg<0>" LOC="M5";

13 NET "led_seg<1>" LOC="M11";

14 NET "led_seg<2>" LOC="P7";

15 NET "led_seg<3>" LOC="P6";

16 NET "led_seg<4>" LOC="N5";

17 NET "led_seg<5>" LOC="N4";

18 NET "led_seg<6>" LOC="P4";

19 NET "led_seg<7>" LOC="G1";

[转]FPGA入门——basys2开发板的伪随机gold码的生成的更多相关文章

- FPGA课设-基于Xilinx Basys2开发板的除法器设计

介绍一下Basys开发板: Basys2 FPGA开发板是一个电路设计实现平台,任何人都可以通过它来搭建一个真正的数字电路.Basys2是围绕着一个Spartan-3E FPGA芯片和一个Atmel ...

- 基于Basys2开发板的简易电子琴和音乐播放器设计

背景:华中科技大学 电测综合实验 主要功能:Basys2开发板外接一个扬声器(或无源蜂鸣器也可)实现电子琴和音乐播放器的功能.其中由于开发板上只有4个按键,所以电子琴功能只做了4个音调,分别对应于4个 ...

- 初学FPGA图像处理,开发板选择建议

我用的是ZYNQ7010的开发板,纯粹是入门学习,对于初学者,使用较多的xlinx入门级的开发板一般是zynq7000系列,淘宝上买的较好的是黑金和米联科,我买的就是黑金的,个人觉得教程很少,学习资料 ...

- [嵌入式开发入门]4412开发板从零建立Linux最小系统

本文转自iTOP-4412开发板实战教程书籍 http://www.topeetboard.com iTOP-4412开发板不仅可以运行Android,还可以运行简单的Linux最小文件系统. 最小L ...

- [FPGA] 1、开发板使用和引脚连接

目录 1.注意事项 2.设备简介 3.引脚分配 注意事项: ① 插拔下载线时必须断电! ② Quartus II 软件和 NIOS 软件的版本必须一致,并安装在同一个目录下面,安装目录不要有中文和空格 ...

- 嵌入式开发之zynq——赛灵思的一款两a9加一fpga芯片的开发板

没办法,回家入职新公司,做通信的,用到这款zynq加ad9163射频架构的开发版,要我做驱动,这可是初次接触zynq,带fpga的集成芯片,心里还是有点惊喜和忧愁,忧愁怎么最快啃下这个硬骨头,好吧上网 ...

- python开发环境配置和python源码打包生成exe可执行文件

Windows下开发环境准备 1.分别安装:python2和python32.安装Python的集成工具:Anaconda3.安装Pycharm Pycharm设置 设置: File->Sett ...

- CrazyBingo mini VIP 2.0 视频开发板 NIOS移植例程(原创)

创建一个NIOS环境 注意事项 前言:(先了解下硬件) 本板卡目前主要适合以下几类人: (1)对FPGA 逻辑开发有强烈的兴趣,并且有一定的HDL基础 (2)计划采用FPGA图像架构,学习并研究图像算 ...

- s3c2140 开发板笔记

文章目录 原理图补充说明 开机串口输出 开发板硬件配置 参考文档 工具下载 代码下载 安装交叉编译器 编译kernel 制作文件系统 配置nfs 配置smb Minimal client-only S ...

随机推荐

- lodash常用

1) Loop for N times // 1. Basic for loop. for(var i = 0; i < 5; i++) { // .... } // 2. Using Arra ...

- Parallel Database for OLTP and OLAP

Parallel Database for OLTP and OLAP Just asurvey article on materials on parallel database products ...

- U-boot for Tiny4412

我的开发板型号: Tiny4412ADK + S700 4GB Flash 1. Build uboot a) 安装好toolchain (arm-linux-gcc-4.5.1-v6-vfp-201 ...

- win10安装 迅雷

下载安装文件所在目录 ,右键,选择以管理员身份运行,输入程序地址,如D:\download\ThunderMini_dl1.5.3.288.exe,回车,这样就出来了程序安装页面,之后就可以就行正常的 ...

- Node之父ry发布新项目deno:下一代Node

https://mp.weixin.qq.com/s/1LcO3EqGV2iRlZ1aIrQeqw

- 借助树莓派模拟Wimonitor并实现WiFi窃听和嗅探

Wimonitor是一款非常优秀的黑客工具,它不仅可以帮渗透测试人员省去配置虚拟机和无线网卡等一系列麻烦事,而且它的Web接口配置起来也非常的方便.实际上,它就是一款TP-Link-MR3020路由器 ...

- Aws Dynamodb数据导出到S3

本节将描写叙述怎样从一个或多个DynamoDB的表导出数据到S3的bucket中.在运行导出之前你须要提前创建好S3的bucket. 注意 假设你还没有使用过AWS Data Pipeline,在运行 ...

- project管理之makefile与自己主动创建makefile文件过程

(风雪之隅 http://www.laruence.com/2009/11/18/1154.html) Linux Makefile自己主动编译和链接使用的环境 想知道到Linux Makefile系 ...

- vue2.0 + vux (四)Home页

1.综合页(首页) Home.vue <!-- 首页 --> <template> <div> <!-- 顶部 标题栏 --> <app-head ...

- iOS 倒计时NSTimer

项目中可能会遇到有些倒计时的地方 比方 手机验证的时候,验证码一般都会有一个时间限制,此时在输入验证码的地方就须要展示一个倒计时 详细实现方式是使用了iOS 自带的 NSTimer 上代码 首先新建 ...