CORTEX-M3中断的现场保护问题

在《Cortex-M3 Devices Generic User Guide.pdf》中介绍了异常入栈和出栈的情况,详见2.3 Exception model。Cortex-M3内核的寄存器如下。

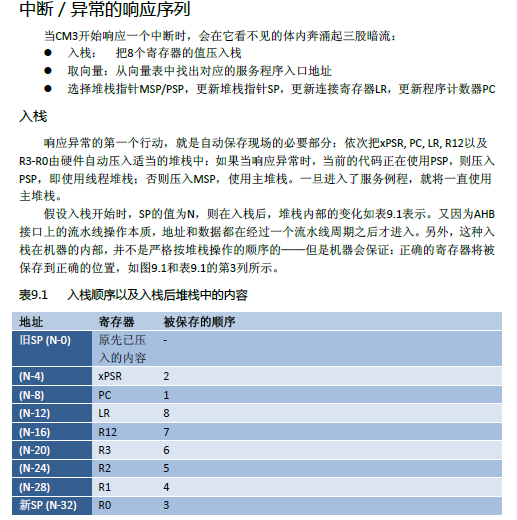

异常发生时,入栈的寄存器是R0~R3+R12+PC+LR+SP。为啥袒护R0‐R3以及R12呢, R4‐R11就是下等公民?(摘自《Cortex-M3权威指南 》第9章)

原来,在ARM上,有一套的C函数调用标准约定(《 C/C++  rocedure Call Standard for the ARM Architecture》,AAPCS, Ref5)。个中原因就在它上面:它使得中断服务例程能用C语言编写,编译器优先使用被入栈的寄存器来保存中间结果(当然,如果程序过大也可能要用到R4‐R11,此时编译器负责生成代码来push它们。但是, ISR应该短小精悍,不要让系统如此操心——译者注)。如果读者再仔细看,会发现R0‐R3, R12是最后被压进去的。这里也有一番良苦用心:为的是可以更容易地使用SP基址来索引寻址,( 以及为了LDM等多重加载指令,因为LDM必须加载地址连续的一串数据)。参数的传递也是受益者:使之可以方便地通过压入栈的R0‐R3取出( 主要为系统软件所利用,多见于SVC与PendSV中的参数传递)。

rocedure Call Standard for the ARM Architecture》,AAPCS, Ref5)。个中原因就在它上面:它使得中断服务例程能用C语言编写,编译器优先使用被入栈的寄存器来保存中间结果(当然,如果程序过大也可能要用到R4‐R11,此时编译器负责生成代码来push它们。但是, ISR应该短小精悍,不要让系统如此操心——译者注)。如果读者再仔细看,会发现R0‐R3, R12是最后被压进去的。这里也有一番良苦用心:为的是可以更容易地使用SP基址来索引寻址,( 以及为了LDM等多重加载指令,因为LDM必须加载地址连续的一串数据)。参数的传递也是受益者:使之可以方便地通过压入栈的R0‐R3取出( 主要为系统软件所利用,多见于SVC与PendSV中的参数传递)。

这就是说,C编译器中断(异常)服务函数封装的这样的需求:当R0~R3+R12不够用时会使用R4‐R11,在使用R4‐R11之前会进行入栈保护;在使用完之后进行出栈恢复现场。

这也为开发人员使用汇编语言编写中断服务函数提供了借鉴。比如,在uC/OS-III移植过程中使用汇编编写任务级/中断级调度器。调度器需要触发Cortex-M3的滴答定时器中断来达到现场保护和任务切换的目的。而这个滴答定时器中断就需要使用汇编编写(详见已经移植好了的os_cpu_a.s)。

对uC/OS-III其他中断即可使用C编译器提供的模板即可:

void xxxxx_xxxHandler(void) ?

{

OSIntEnter();

…… //中断服务函数代码

OSIntExit();

}

分析一下其过程

响应xxxxx_xxxHandler之后,保存现场R0~R3+R12+PC+LR+SP,执行OSIntEnter()和中断服务函数代码(若这期间如果通用寄存器不够用时会使用R4‐R11,使用前会先进行入栈保护,使用后出栈恢复现场),然后会在中断级调度器OSIntExit()中判定是否需要进行任务切换,如果需要则定位好待切换的任务,最后挂起由汇编编写的滴答定时器中断。这会引入“咬尾机制”直接转而去执行滴答定时器中断服务函数。

通过对C编译器封装的中断服务函数模型进行的“背地儿里”的操作,可以预见C编译器对普通函数模型封装的额外操作。至少不会比这个复杂吧....

----

CORTEX-M3中断的现场保护问题的更多相关文章

- ARM Cortex M3系列GPIO口介绍(工作方式探讨)

一.Cortex M3的GPIO口特性 在介绍GPIO口功能前,有必要先说明一下M3的结构框图,这样能够更好理解总线结构和GPIO所处的位置. Cortex M3结构框图 从图中可以看出 ...

- ARM Cortex M3(V7-M架构)硬件启动程序 一

Cortex-m3启动代码分析笔记 启动代码文件名是STM32F10X.S,它的作用先总结下,然后再分析. 启动代码作用一般是: 1)堆和栈的初始化: 2)中断向量表定义: 3)地址重映射及中断向量表 ...

- STM32学习之路入门篇之指令集及cortex——m3的存储系统

STM32学习之路入门篇之指令集及cortex——m3的存储系统 一.汇编语言基础 一).汇编语言:基本语法 1.汇编指令最典型的书写模式: 标号 操作码 操作数1, 操作数2,... ...

- 【ARM-Linux开发】ARM7 ARM9 ARM Cortex M3 M4 有什么区别

ARM7 ARM9 ARM Cortex M3 M4 区别 arm7 arm9 可以类比386和奔腾, 不同代,arm9相比arm7指令集和性能都有所增强,arm7和arm9都有带mmu和无mmu的版 ...

- 【freertos】002-posix模拟器设计与cortex m3异常处理

目录 前言 posix 标准接口层设计 模拟器的系统心跳 模拟器的task底层实质 模拟器的任务切换原理 cortex M3/M4异常处理 双堆栈指针 双操作模式 栈帧 EXC_RETURN 前言 如 ...

- ARM 架构、ARM7、ARM9、STM32、Cortex M3 M4 、51、AVR 之间有什么区别和联系?(转载自知乎)

ARM架构: 由英国ARM公司设计的一系列32位的RISC微处理器架构总称,现有ARMv1~ARMv8种类. ARM7: 一类采用ARMv3或ARMv4架构的,使用冯诺依曼结构的内核. ...

- Implementation of Serial Wire JTAG flash programming in ARM Cortex M3 Processors

Implementation of Serial Wire JTAG flash programming in ARM Cortex M3 Processors The goal of the pro ...

- stm32和cortex M3学习内核简单总结

1.stm32综述 2.寄存器组 3.操作模式和特权级别 4.存储器映射 5.中断和异常 6.其他 Stm32综述 这可以说是我第一款认真学习的单片机了,学完这个就要开启我通往arm9的大门了,接下来 ...

- ARM Cortex M3(V7-M架构)硬件启动程序 二

解析 STM32 的启动过程 解析STM32的启动过程 当前的嵌入式应用程序开发过程里,并且C语言成为了绝大部分场合的最佳选择.如此一来main函数似乎成为了理所当然的起点——因为C程序往往从main ...

随机推荐

- python程序打包exe

http://c.biancheng.net/view/2690.html 用inno setup做成安装包(官网上下载) http://www.jrsoftware.org/isdl.php

- Django组件之modelformset

ModelFormSet 基于modelform 实现的批量处理 前端: <form method="post" action=""> {% csr ...

- (转)Java锁性能提高有哪些机制?

转自:https://forum.idevfun.io/t/topic/235/2 Java 中,Synchronized是通过对象内部的一个叫做监视器锁(monitor)来实现的.但是监视器锁本质又 ...

- 无法访问此网站 ERR_CONTENT_DECODING_FAILED

这个错误挺少见的. 百度了下: 1,说是文件编码格式不正确: 2,说是Nginx的压缩和tomcat的压缩冲突了,关闭gzip压缩: 3,……………… 不管是哪一种情况,都是编码问题,所以逐一排查,根 ...

- java基础(1)----简介

基础语法. 面向对象. 字符串和集合. IO流. 接口. lambda. 方法引用. Stream. 模块化. 一.java的前世今生: J2SE:标准体验版.J2EE:企业版.J2ME:小型版(移动 ...

- 手写butterknife来剖析其原理

基本使用: 对于butterknife库我想基本上都非常熟了,如今在项目中用它也用得非常之频繁了,不过为了学习的完整性,先来简单的回顾一下基本用法,先新建一个工程: 然后给textview增加一个点击 ...

- 0019SpringBoot使用异步任务(多线程)与定时任务

SpringBoot开启异步任务只需要两步配置: 1.在主类上加上注解@EnableAsync开启异步功能 2.在service层的方法上加上注解@Async指定调用方法时是异步的 SpringBoo ...

- <你们都是魔鬼吗>第二次团队作业:团队项目选题

第二次团队作业:团队项目选题 项目 内容 这个作业属于哪个课程 任课教师博客主页链接 这个作业的要求在哪里 作业链接地址 团队名称 你们都是魔鬼吗 作业学习目标 任务1: 团队初选项目可行性自评,使用 ...

- js获取此刻时间或者把日期格式时间转换成字符串格式的时间

getTime(val){ if (val&val instanceof Date){ d = val; }else{ d = new Date(); }; var year = d.getF ...

- postgresql学习笔记--基础篇 -psql工具

--创建用户 CREATE ROLE pguser WITH ENCRYPTED PASSWORD 'pguser'; --创建表空间目录 mkdir -p /database/pg10/pg_tbs ...