关于信号的延迟---verilog

关于信号的延迟---verilog

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: chensimin

//

// Create Date: 2018/02/08 11:39:20

// Design Name:

// Module Name: signal_detect

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

////////////////////////////////////////////////////////////////////////////////// module signal_detect( input wire clk,

input wire rst,

input wire signal_en

//input wire signal

//output wire signal_existence

); reg signal;

always @(posedge clk or posedge rst)

begin

if(rst)

signal <= 'b0;

else if(signal_en)

signal <= 'b1;

else

signal <= 'b0;

end reg signal_delay;

wire signal_rise;

always @(posedge clk or posedge rst)

begin

if(rst)

signal_delay <= 'b0;

else

signal_delay <= signal;

end assign signal_rise = !signal_delay && signal; endmodule /* add_force {/signal_detect/clk} -radix hex {1 0ns} {0 50000ps} -repeat_every 100000ps

add_force {/signal_detect/rst} -radix hex {1 0ns} {0 150ns}

add_force {/signal_detect/signal_en} -radix hex {0 0ns} {1 300ns} {0 400ns} */

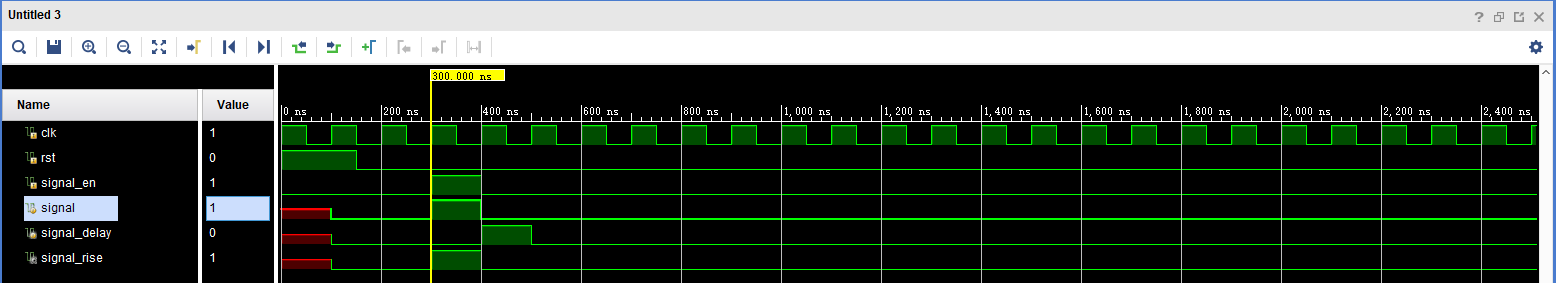

仿真波形:

容易犯下这样一种错误:

module signal_detect(

input wire clk,

input wire rst,

input wire signal

//input wire signal

//output wire signal_existence

);

reg signal_delay;

wire signal_rise;

always @(posedge clk or posedge rst)

begin

if(rst)

signal_delay <= 'b0;

else

signal_delay <= signal;

end

assign signal_rise = !signal_delay && signal;

endmodule

/*

add_force {/signal_detect/clk} -radix hex {1 0ns} {0 50000ps} -repeat_every 100000ps

add_force {/signal_detect/rst} -radix hex {1 0ns} {0 150ns}

add_force {/signal_detect/signal} -radix hex {0 0ns} {1 300ns} {0 400ns}

*/

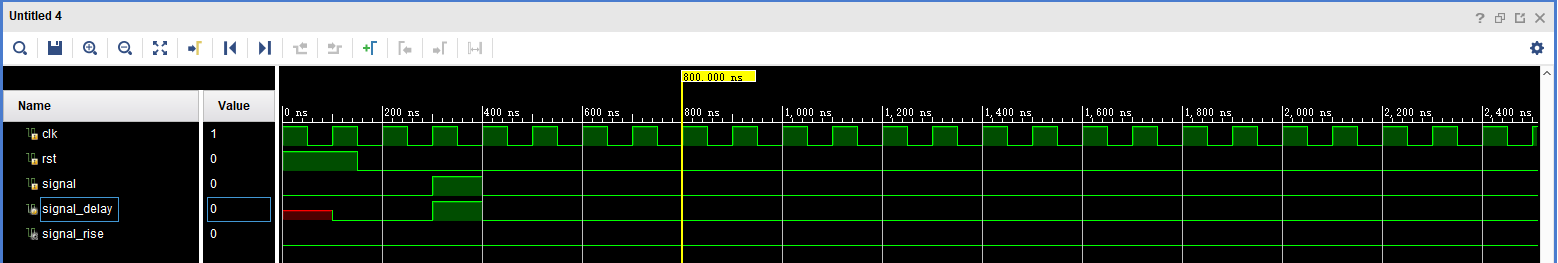

仿真波形:

像这种写法,根本就起不到边沿检测的作用,只是对外部信号进行一次采集。

关于信号的延迟---verilog的更多相关文章

- 信号滤波模块verilog代码---UNLOCK,LOCK状态机方式

信号滤波模块verilog代码 `timescale 1ns / 1ps /////////////////////////////////////////////////////////////// ...

- 【设计经验】1、Verilog中如何规范的处理inout信号

在FPGA的设计过程中,有时候会遇到双向信号(既能作为输出,也能作为输入的信号叫双向信号).比如,IIC总线中的SDA信号就是一个双向信号,QSPI Flash的四线操作的时候四根信号线均为双向信号. ...

- verilog语法实例学习(1)

本文档中通过verilog实例来学习verilog语法.Verilog是一种硬件描述语言,它具有并发性和时序性.并发性是指不同硬件模块的同时操作,时序性是指信号的赋值或操作在时钟的边沿进行.由于作者本 ...

- verilog语法学习目录

verilog语法实例学习(1) Verilog中的注释 Verilog中的信号 标识符 信号的值 Verilog中的数字 Verilog中的参数 verilog语法实例学习(2) 线网类型 变量类型 ...

- FPGA异步时钟系统中信号处理之单比特信号

有些东西当你习以为常而不去深思熟虑的时候,致命的错误就会因此埋下! FPGA开发中难免会遇到跨时钟域处理的问题,而对于单比特信号,我会不假思索的回答:打两拍不久解决了吗?但是事实时,这佯作的 ...

- 06-BCD计数器设计与应用——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线--普利斯队长精心奉献 实验目的:1.掌握BCD码的原理.分类以及优缺点 2.设计一个多位的8421码计数器并进行验证 3.学会基本的错误定位以及修改能力 ...

- 最快让你上手ReactiveCocoa之基础篇

前言 很多blog都说ReactiveCocoa好用,然后各种秀自己如何灵活运用ReactiveCocoa,但是感觉真正缺少的是一篇如何学习ReactiveCocoa的文章,这里介绍一下. 1.Rea ...

- ReactiveCocoa学习

ReactiveCocoa常见类 6.1RACSiganl:信号类,一般表示将来有数据传递,只要有数据改变,信号内部接收到数据,就会马上发出数据. 注意: 信号类(RACSiganl),只是表示当数据 ...

- ReactiveCocoa基础知识内容

本文记录一些关于学习ReactiveCocoa基础知识内容,对于ReactiveCocoa相关的概念如果不了解可以网上搜索:RACSignal有很多方法可以来订阅不同的事件类型,ReactiveCoc ...

随机推荐

- GB2312汉字编码字符集对照表

第01区 +0 +1 +2 +3 +4 +5 +6 +7 +8 +9 +A +B +C +D +E +F A1A0 . . ・ ˉ ˇ ¨ " 々 ― - | - ' ' A1B0 &quo ...

- 适配手机端之 rem

(function() { var psdWidth = 1080, maxRem = 100, ch = document.documentElement.clientHeight || docum ...

- CountDownLatch & CyclicBarrier

CountDownLatch 在完成一组正在其他线程中执行的操作之前,它允许一个或多个线程一直等待.用给它的代数初始化CountDownLatch,且计数器无法被重置.当前计数到达0之前,await方 ...

- 在Microsoft Power BI中创建地图的10种方法

今天,我们来简单聊一聊“地图”. 在我们日常生活中,地图地位已经提升的越来越高,出门聚餐.驾驶.坐车.旅行......应运而生的就是各种Map APP. 作为数据分析师,我们今天不讲生活地图,要跟大家 ...

- 一种绕过PTRACE反调试的办法

Linux 系统gdb等调试器,都是通过ptrace系统调用实现.Android加固中,ptrace自身防止调试器附加是一种常用的反调试手段. 调试时一般需要手工在ptrace处下断点,通过修改ptr ...

- 如何更改Apache的根目录指向

更改Apache的默认网站根目录地址方法如下: 0,先找到主目录下的apache文件,然后进行下面操作 1.找到 DocumentRoot “X:/Apache/htdocs” 将“X:/Apache ...

- Codeforces Round #519

题目链接:传送门 A. Elections (思维+暴力) 思路: 从最小的k开始枚举就好了- -. #include <bits/stdc++.h> using namespace ...

- C# 后台获取前台交互判断

前台传来明细 ,判断是否修改,在把前台 的数据组成新的类保存 public class tt { public string id { get; set; } public string e_id { ...

- 【HDOJ3018】【一笔画问题】【欧拉回路+并查集】

http://acm.hdu.edu.cn/showproblem.php?pid=3018 Ant Trip Time Limit: 2000/1000 MS (Java/Others) Me ...

- linux系统lnmp环境包搬家教程

打包搬家apt-get install zip unzip -yyum install zip unzip -y# debian ubuntu 用apt-get,centos用yumcd /home/ ...