Cortext-A7_i.MX 6ULL——多模式DDR控制器(MMDC)

1、概述

i.MX 6ULL系列芯片的MMDC是一个多模式DDR控制器,支持DDR3/DDR3Lx16和LPDDR2x16的存储类型,MMDC是可配置,高性能,优化的内存控制器。

注:DDR3/DDR3Lx16、LPDDR2x16 ,此处的x16表示芯片位宽,每个传输周期能够提供的数据量(bit)。也就是说明,如果要提供32位的位宽内存存储,需要2颗以上型号的内存进行并联使用。

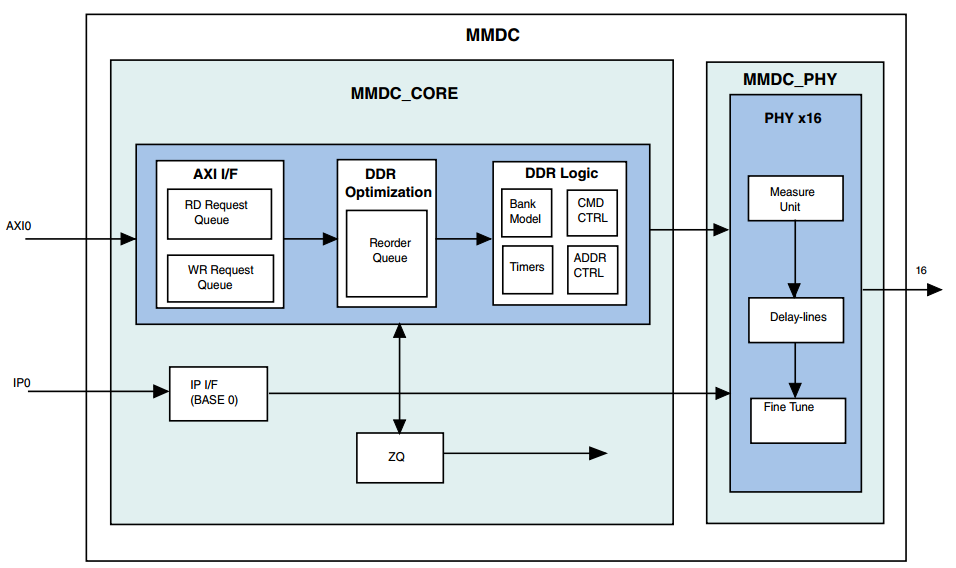

下面是MMDC逻辑框图:

- MMDC由内核(MMDC_CORE)和物理层(MMDC_PHYl)两部分构成。

- 内核负责通过AXI接口,DDR命令发生器,DDR命令优化器,和读写数据通道与系统通信,物理层负责定时调整,它使用特殊校准机制确保数据获取400MHz的时钟频率。

- MMDC的内部配置寄存器通过IP通道进行配置。

DDR标准:

- DDR3L,DDR3x16 LPDDR2x16

- 不支持LPDDR1MDDR 和DDR2

DDR接口:

- 16位数据总线宽度;

- 器件密度-256Mbits-8Gbits,其中列8-12bit,行11-16bit;

- 通过配置CS0,CS1可以达到4Gbyte地址空间;

- DDR3支持的突发长度为8;

- LPDDR2支持的突发长度为4;

DDR性能:

- 400MHz核心频率,800MHz数据频率

- 支持实时优先级,支持不同优先级的重新排序机制:实时,延时敏感,正常优先级

- 页面碰撞错过优化

- 连续读写访问优化

- 支持深度读写请求队列,支持bank预测

- 支持bank交叉

- ddr3模式下(突发长度)的非对齐换行访问情况下的特殊优化

AXI接口:

- 运行在400MHz,支持传输8/16/64 bits(单一访问和突发)

- 支持最大突发长度为16

- 支持16bits AXI ID

DDR通用设置:

- 可配置时序参数

- 可配置刷新周期

- 支持页边界交叉

- 支持LPDDR2 MRW和MRR指令

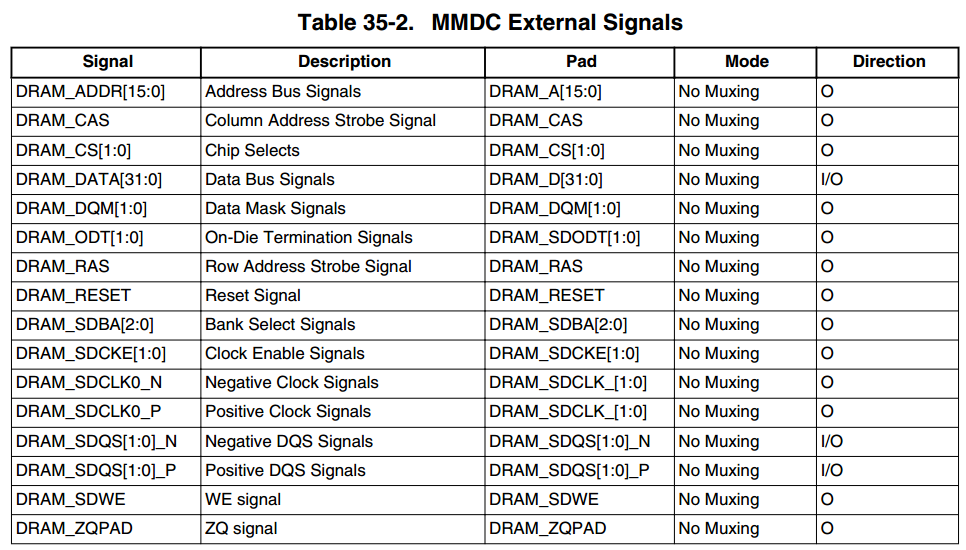

2、外部接口信号

3、时钟源

时钟设置参考CCM(clock controller module)模块

4、功能性说明

4.1 读/写数据流

4.2 MMDC初始化

4.3 配置MMDC寄存器

4.4 MMDC地址空间

4.5 LPDDR2与DDR3引脚复用映射

4.6 节能和时钟切换模式

4.7 复位

4.8 刷新计划

4.9 用于DDR的突发长度选项

4.10 独家访问处理

4.11 AXI错误处理

5、性能

5.1 仲裁和重新排序机制

5.2 预测机制

5.3 针对DDR3访问的特殊优化

6、MMDC 调试

7、 MMDC 剖析

8、LPDDR2刷新率更新和定时减量

9、DLL切换

10、ODT配置

11、校准过程

12、MMDC 内存映射/寄存器定义

参考资料:

https://blog.csdn.net/u011124985/article/details/81140819

IMX6ULLRM.pdf——恩智浦提供下载

https://baike.baidu.com/item/%E5%86%85%E5%AD%98%E6%9D%A1

Cortext-A7_i.MX 6ULL——多模式DDR控制器(MMDC)的更多相关文章

- mig_7series DDR控制器的配置

mig_7series DDR控制器的配置

- ThinkPHP3开发模式,控制器操作,配置文件,框架语法

ThinkPHP的开发模式 tp框架有两种使用模式:开发模式(调试模式),一种是生产模式(运行模式) define('APP_DEBUG', true); //调试模式 define('APP_DE ...

- thinkphp3.2笔记(1)目录,控制器及url模式,地址解析

一.目录 Application : tp默认的应用代码存储的目录 Public : Tp 默认的存储静态资源的目录,img,css,js ThinkPHP : Tp 框架的源代码 ...

- 编写SDR SDRAM页突发模式控制器的注意点

网上有很多的SDR SDRAM控制器的代码,但都是基于burst1/2/4/8模式下的,这种模式下传输高速的相机数据还是有点拮据的,所以花了几天把这些模式改造成了页突发模式.我的这个控制器模型是这样的 ...

- zedboard如何从PL端控制DDR读写(五)

有了前面的一堆铺垫.现在终于开始正式准备读写DDR了,开发环境:VIVADO2014.2 + SDK. 一.首先要想在PL端通过AXI去控制DDR,我们必须要有一个AXI master,由于是测试,就 ...

- 痞子衡嵌入式:飞思卡尔i.MX RT系列MCU特性介绍(1)- 概览

大家好,我是痞子衡,是正经搞技术的痞子.今天痞子衡给大家介绍的是飞思卡尔i.MX RT系列MCU的基本特性. ARM Cortex-M微控制器芯片厂商向来竞争激烈,具体可参看我的另一篇文章<第一 ...

- DDR电源硬件设计要点

一.DDR电源简介 1. 电源 DDR的电源可以分为三类: a.主电源VDD和VDDQ,主电源的要求是VDDQ=VDD,VDDQ是给IO buffer供电的电源,VDD是给但是一般的使用中都是把VDD ...

- 基于MIG IP核的DDR3控制器(一)

最近学习了DDR3控制器的使用,也用着DDR完成了一些简单工作,想着以后一段可能只用封装过后的IP核,可能会忘记DDR3控制器的一些内容,想着把这个DDR控制器的编写过程记录下来,便于我自己以后查看吧 ...

- 痞子衡嵌入式:飞思卡尔i.MX RTyyyy系列MCU特性那些事(1)- 概览

大家好,我是痞子衡,是正经搞技术的痞子.今天痞子衡给大家介绍的是飞思卡尔i.MX RTyyyy系列MCU的基本特性. ARM Cortex-M微控制器芯片厂商向来竞争激烈,具体可参看我的另一篇文章&l ...

随机推荐

- jenkins grunt 自动构建流程

1. grunt生成的压缩文件不建议上传到svn,src里的源码和grunt,npm的配置文件保存在svn里就够了2. grunt有watch任务,src里的文件改变了可以自动执行任务,比如压缩,3. ...

- 什么是jquery

框架就是一个半成品,不能直接使用,需要加工处理后才可使用

- Models中字段的参数

(1)null 如果为True,Django 将用NULL 来在数据库中存储空值. 默认值是 False. (1)blank 如果为True,该字段允许不填.默认为False. 要注意,这与 null ...

- Numpy一文全了解

1,Numpy是一个python包,它是一个由多维数组对象和处理数组的例程集合组成的库. 2. Numpy的操作:(1)数组的算数和逻辑运算 :(2)傅里叶变换和用于图形操作 (3)与线性代数有 ...

- step_by_step_CSRF/ XSRF_问题描述

接触Asp.net boilerplate 一段时间,一次同事将他的代码添加到zero项目模板中,他将路由配置成他的页面,目的是要让zero项目登录成功之后跳转到他的页面,可是通过fiddler监视请 ...

- python的bit_length方法

bit_length方法作用是得到指定数值的二进制的长度数.宽度数 举例: age=1 v=age.bit_length() print(v) 返回结果: 1 #数值1对应的二进制是1,长度1位 ...

- MySQL如何解决1209错误

1209 - The MySQL server is running with the--read-only option so it cannot execute this sta ...

- MMU二级页表

https://blog.csdn.net/forDreamYue/article/details/78887035

- Python基础-python流程控制之循环结构(五)

循环结构 循环结构可以减少源程序重复书写的代码量,用来描述重复执行某段算法的问题. Python中循环结构分为两类,分别是 while 和 for .. in. 一.while循环 格式1: whil ...

- Spring 文件上传MultipartFile 执行流程分析

在了解Spring 文件上传执行流程之前,我们必须知道两点: 1.Spring 文件上传是基于common-fileUpload 组件的,所以,文件上传必须引入此包 2.Spring 文件上传需要在X ...