RTL级低功耗设计

重点:门控时钟和操作数隔离

1.并行与流水的选择

并行与流水都是用面积换速度,但是有时可以降低功耗

并行处理常用于数字信号处理部分,采用并行处理,也已降低系统工作频率从而降低功耗

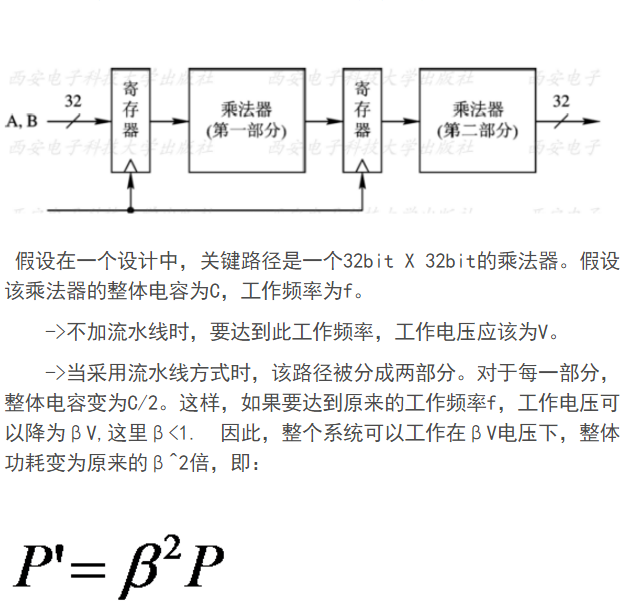

用两个乘法器取代原设计中的一个乘法器,时钟频率会降低,系统整体功耗也会降低。

流水线技术是将一个较长的组合路径分为M级流水线。路径长度缩短为原始路径长度的1/M。这样一个时钟周期内充/放电短融变为C/M。如果在加入流水线之后,时钟速度不变,则一个周期能只需要对C/M进行充/放电。因此在相同的速度要求下,可以采用较低的电源电压来驱动系统,系统的整体功耗可能会降低

2.资源共享与状态编码

利用数据编码来降低开关活动(例如,用格雷码比用二进制码翻转更少,功耗更低)

3.操作数隔离(operand isolation,简称OI)

可以通过EDA工具来实现

1.如果在某一段时间内,数据通路的输出是无用的,则将它的输入置成个固定值,这样,数据通路部分没有翻转.功耗就会降低.不过这种做法会增加面积,影响到DFT

2.在使用compile命令进行综合时,如果手动指定的IO物体满足前面的三点:

1.OI物体是算术运算器或层次组合单元。

2.OI物体的输出是选择性地使用。

3.运算器必须有非零的翻转率。

那么综合器就会进行操作数隔离。

3.实现操作数隔离需要插入相应的隔离逻辑,比如与门或者或门之类的。

4.门控时钟(注意和使能时钟的区别,门控时钟降低功耗,而使能时钟不能降低功耗)

注意。使用的是锁存器。

这种方式消除了EN与CLK组合产生的毛刺对门控时钟的影响。该方法的原理在于:锁存器在CLK为低时透明。这样,EN 信号上的毛刺仅出现在CLK的低电平处,EN1与CLK进行与操作,可以将这部分毛刺消除掉。这样,GCLK上就没有毛刺了。

这里粘一下锁存器和DFF的区别

锁存器:电平敏感;DFF:边沿敏感

if和case不全的时候很同意产生latch

区别:

1、latch由电平触发,非同步控制。在使能信号有效时latch相当于通路,在使能信号无效时latch保持输出状态。DFF由时钟沿触发,同步控制。

2、latch容易产生毛刺(glitch),DFF则不易产生毛刺。

3、如果使用门电路来搭建latch和DFF,则latch消耗的门资源比DFF要少,这是latch比DFF优越的地方。所以,在ASIC中使用 latch的集成度比DFF高,但在FPGA中正好相反,因为FPGA中没有标准的latch单元,但有DFF单元,一个LATCH需要多个LE才能实现。

4、latch将静态时序分析变得极为复杂。

一般的设计规则是:在绝大多数设计中避免产生latch。它会让您设计的时序完蛋,并且它的隐蔽性很强,非老手不能查出。latch最大的危害在于不能过滤毛刺。这对于下一级电路是极其危险的。所以,只要能用D触发器的地方,就不用latch。

有些地方没有时钟,也只能用latch了。比如现在用一个clk接到latch的使能端(假设是高电平使能),这样需要的setup时间,就是数据在时钟的下降沿之前需要的时间,但是如果是一个DFF,那么setup时间就是在时钟的上升沿需要的时间。这就说明如果数据晚于控制信号的情况下,只能用 latch,这种情况就是,前面所提到的latch timing borrow。基本上相当于借了一个高电平时间。也就是说,latch借的时间也是有限的。

latch优缺点:

latch的好处:

因为使用latch可以timing borrow,在高速电路设计中(timing会很紧),有时候就需要用latch。

latch的缺点:

1. latch是电平触发,无法实现同步操作,与我们正常的时序逻辑电路设计思路不符。

2. latch会对输入电平敏感,受布线延迟影响较大,比较容易导致输出有毛刺产生。

3. latch会导致静态时序分析和DFT会很复杂。

4. 在ASIC中使用latch的集成度比DFF高,但在FPGA中正好相反,因为FPGA中没有标准的latch单元,但有DFF单元,一个LATCH需要多个LE才能实现。

所以ASIC中一般用latch,fpga中一般用DFF,或者没有时钟的时候用latch

timing borrow:比如现在用一个clk接到latch的使能端(假设是高电平使能),这样需要的setup时间,就是数据在时钟的下降沿之前需要的时间,但是如果是一个DFF,那么setup时间就是在时钟的上升沿需要的时间。这就说明如果数据晚于控制信号的情况下,只能用 latch,这种情况就是,前面所提到的latch timing borrow。基本上相当于借了一个高电平时间。也就是说,latch借的时间也是有限的。

RTL级低功耗设计的更多相关文章

- (数字IC)低功耗设计入门(四)——RTL级低功耗设计

二.RTL级低功耗设计 前面介绍了系统级的低功耗设计,换句话说就是在系统级降低功耗可以考虑的方面.系统级的低功耗设计,主要是由系统级设计.具有丰富经验的人员实现,虽然还轮不到我们设计,我们了解一下还是 ...

- (数字IC)低功耗设计入门(五)——RTL级低功耗设计(续)

二.RTL级低功耗设计(续) 前面一篇博文我记录了操作数隔离等低功耗设计,这里就主要介绍一下使用门控时钟进行低功耗设计. (4)门控时钟 门控时钟在我的第一篇博客中有简单的描述,这里就进行比较详细的描 ...

- (数字IC)低功耗设计入门(八)——物理级低功耗设计&to be continued?

前面学习了从系统级到门级的低功耗设计,现在简单地了解了一下物理级设计.由于物理级的低功耗设计与后端有关了,这里就不详细学习了.这里主要是学习了一些基本原则,在物理级,进行低功耗设计的基本原则是: ...

- (数字IC)低功耗设计入门(三)——系统与架构级

前面讲解了使用EDA工具(主要是power compiler)进行功耗分析的流程,这里我们将介绍在数字IC中进行低功耗设计的方法,同时也结合EDA工具(主要是Design Compiler)如何实现. ...

- (数字IC)低功耗设计入门(六)——门级电路低功耗设计优化

三.门级电路低功耗设计优化 (1)门级电路的功耗优化综述 门级电路的功耗优化(Gate Level Power Optimization,简称GLPO)是从已经映射的门级网表开始,对设计进行功耗的优化 ...

- (数字IC)低功耗设计入门(七)——门级电路低功耗设计优化(续)

前面讲解了门级功耗的优化方法,包括静动态和总体的功耗.现在来记录一下门级层次(有点书也说是在系统级)常用的一种低功耗方法--电源门控. ①电源门控概述与原理 电源门控是指芯片中某个区域的供电电源被关掉 ...

- (数字IC)低功耗设计入门(二)——功耗的分析

前面学习了进行低功耗的目的个功耗的构成,今天就来分享一下功耗的分析.由于是面向数字IC前端设计的学习,所以这里的功耗分析是基于DC中的power compiler工具:更精确的功耗分析可以采用PT,关 ...

- 行为级和RTL级的区别(转)

转自:http://hi.baidu.com/renmeman/item/5bd83496e3fc816bf14215db RTL级,registertransferlevel,指的是用寄存器这一级别 ...

- (数字IC)低功耗设计入门(一)

低功耗设计这个专题整理了好久,有一个月了,有图有证据: 然而最近一直有些烦心事.郁闷事,拖延了一下,虽然现在还是有点烦,但是还是先发表了吧.下面我们就来聊聊低功耗设计吧,由于文章比较长,因此我就不一次 ...

随机推荐

- 基于SSH开发银行个人业务管理系统 附源码

开发环境: Windows操作系统开发工具: MyEclipse+Jdk+Tomcat+MySql数据库 运行效果图

- 浅谈python中__str__和__repr__的区别

很多时候我们在创建一个类的时候,在终端打印类或者查看的时候一般都不会得到一个太满意的结果 class T: def __init__(self): self.color="red" ...

- Nginx 反向代理报400错误解决方法!

如果后端真是的服务器设置有类似防盗链或者根据http请求头中的host字段来进行路由或判断功能的话,如果反向代理层的nginx不重写请求头中的host字段,将会导致请求失败,报400错误,解决办法: ...

- python集合操作方法详解

前言 说集合之前,我们先说一个小例子,假设某公司有五个人喜欢打篮球,五个人喜欢打游戏,问即打游戏有打篮球的人都有哪些? play_basketball = ['a','b','c','d','e'] ...

- idea选择主题

主题下载地址1:http://color-themes.com/?view=index 主题下载地址2:http://www.themesmap.com/ 主题下载地址3:http://www.ria ...

- 02使用GitHub远程仓库

一.远程库配置 由于本地的GIT仓库和GitHub仓库之间的传输是通过SSH加密的,所以需要以下配置: 1.创建SSH key 为什么GitHub需要SSHKey:根据key来授权,有哪些key可以往 ...

- python知识点总结以及15道题的解析

先看知识点总结 一.序列操作符x in s 如果x是列表s的元素,返回True,否则Falses + t 连接两个序列s和ts*n或者n*s 将序列s复制n次s[i] 返回s中第i元素s[i:j]或s ...

- Elasticsearch 6.8.4 启动报错解决方法

运行环境:centos 7,jdk 1.8 问题一: ERROR: bootstrap checks failed max ] ] 原因:无法创建本地文件问题,用户最大可创建文件数太小 解决方案:切换 ...

- selenium webdriver 屏幕滚动

//山寨法 String setscroll = "document.documentElement.scrollTop=100"; JavascriptExecutor jse= ...

- 吴裕雄 Bootstrap 前端框架开发——Bootstrap 排版:标题

<!DOCTYPE html> <html> <head> <meta charset="utf-8"> <title> ...