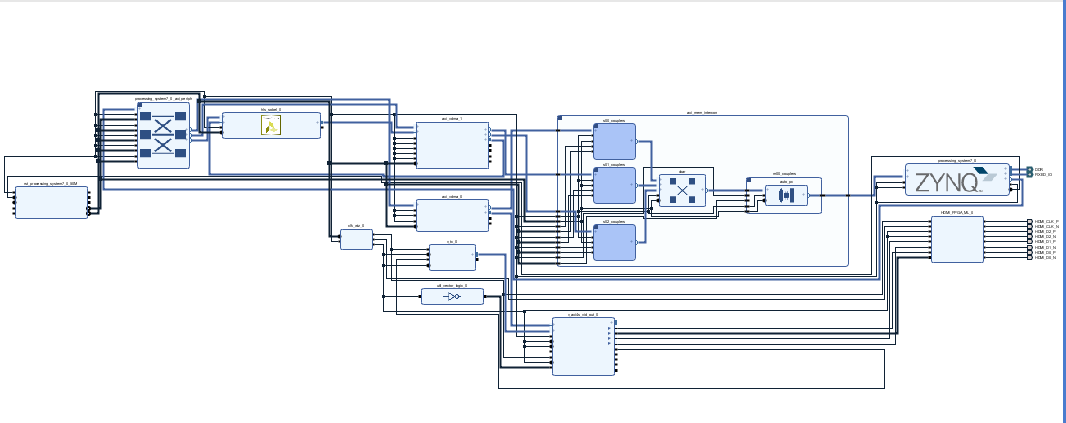

sobel算法的Soc FPGA实现之框架分析(二)

重点分析一、AXI_VDMA_1

之前一直认为这个就是内含有DDR的ip核(......最近才搞懂是个啥),后来经过对FDMA的分析发现这就是个框架,通AXI总线挂载到bus总线,可以实现PL端FPGA代码直接读写PS侧的DDR。

几个关键的AXI(AXIS)总线接口:

(1)、S_AXI_LITE接口:该接口收到ZYNQ核和GP总线控制,M_AXI_GP接口通过AXI-Lite总线控制VDMA的配置

(2)、M_AXIS_MM2S接口:本接口将从DDr中读取的数据发送到sobel处理ip

(3)、M_AXIS_S2MM接口:该接口接收sobel处理ip核的输出数据流

(4)、M_AXI_S2MM接口:该接口将数据输出到ZYNQ处理器,然后数据可以刷入DDR

(5)、M_AXI_MM2S接口:该接口接收来自DDR的像素数据

学习完FDMA之后,对VDMA才有了一个初步的了解,VDMA就是通过AXI(AXIS)总线挂载到总线的典型应用,M_AXI_MM2S接口接收到来自ps侧DDR的像素数据,然后通过M_AXI_MM2S将数据发送到sobel ip核,ip对图片数据进行处理后进行将数据转换为AXI_STREAM格式,可以在上一篇博文中看到,输出数据通过S_AXIS_S2MM进入VDMA,然后,由于在VDMA中设置的是三帧缓存,这三帧数据并不是在VDMA中缓存的,是在DDR中进行缓存。那么VDMA与三帧数据的关系是什么?参考FDMA中的设计,CDMA就是对输入数据设计了一个标志位flag,保证有三帧数据传送到DDR进行缓存。数据通过M_AXI_MM2S接口进入DDR。

那么,AXI_CONNECT1的作用中有一个S00_AXI的作用=是什么?可以看到该总线发出读请求,读取ps侧DDR缓存的像素数据。

其他分析二、AXI_VDMA

框架流程:就是将图像数据以二进制形式进行存储,ZYNQ通过AXI_GP接口对各个模块进行配置,将sobel处理的结构通过stream数据流发送到vdma0,再经过stream2video进行转换,将输出图像发送到HDMI核,video timing核的作用是进行时钟约束,其中HDMI的主时钟是74.25Mhz,除此之外还输入一个串转并数据时钟,为主时钟的5M:74.25*5Mhz。

复位管理单元的作用是将复位信号于时钟进行同步处理,所以主时钟连接到复位管理单元的同步时钟端,由ZYNQ产生的复位信号连接到ext_reset_in,就是extern外部复位信号输入。输出两个信号,一个信号用于专用于AXI总线互联模块,另一个用于模块以及AXI传输的复位信号。个人理解是这个peripheral_reset的作用是局部模块的复位信号,但是它好就好在与AXI_CLK同步,可以在AXI的局部传输中进行复位,AXI_CONNECT的总复位信号是interconnect_aresetn,在信号处理中,复位判断语句应该是(interconnect_aresetn||M02_ARESETN),此处的M02_ARESETN仅是用来举例,还可以是其他的复位信号

VDMA0为什么不用设置成可写呢?

因为数据通过MM2S仅可从GP来到VDMA0,然后经过三帧缓存之后从MM2S到stream视频流输出IP, 将HDMI核需要的信号给HDMI控制器,比较关键的一点是Video Out的vtg_ce,用于暂停时序发生器以达到同步的的目的。

sobel算法的Soc FPGA实现之框架分析(二)的更多相关文章

- PHP 面向对象及Mediawiki 框架分析(二)

mediaHandler可以理解为处理media文件的 /includes/filerepo/file/File.php /** * Get a MediaHandler instance for t ...

- 14FPGA综设之图像边沿检测的sobel算法

连续学习FPGA基础课程接近一个月了,迎来第一个有难度的综合设计,图像的边沿检测算法sobel,用verilog代码实现算法功能. 一设计功能 (一设计要求) (二系统框图) 根据上面的系统,Veri ...

- SoC FPGA JTAG电路设计 要点

JTAG协议制定了一种边界扫描的规范,边界扫描架构提供了有效的测试布局紧凑的PCB板上元件的能力.边界扫描可以在不使用物理测试探针的情况下测试引脚连接,并在器件正常工作的过程中捕获运行数据. SoC ...

- SoC FPGA开发板的FPGA配置数据下载和固化

小梅哥编写,未经许可,严禁用于任何商业用途 2018年7月2日星期一 soc fpga的烧写和固化方式与传统的纯fpga固化方式即存在形式上的相同,也存在细节上的差异,特整理此文. AC501-So ...

- Intel Cyclone SoC FPGA介绍

3.1 Intel Cyclone SoC FPGA介绍 3.1.1 SoC FPGA的基本概念 Intel Cyclone V SoC FPGA是Intel PSG(原Altera)于2013年发布 ...

- Sobel算法

最近看了一些Sobel算法,并试了一下,源码如下: private void Sobel(Bitmap img) { int width = img.Width; int height = img.H ...

- opencl+opencv实现sobel算法

这几天在看opencl编程指南.照着书中的样例实现了sobel算法: 1.结合opencv读取图像,保存到缓冲区中. 2.编写和编译内核.并保存显示处理后的结果. 内核: const sampler_ ...

- 【原创】Linux v4l2框架分析

背景 Read the fucking source code! --By 鲁迅 A picture is worth a thousand words. --By 高尔基 说明: Kernel版本: ...

- Python遗传算法工具箱DEAP框架分析

本文主要介绍python遗传算法工具箱DEAP的实现.先介绍deap的如何使用,再深入介绍deap的框架实现,以及遗传算法的各种实现算法. 代码可以参考 https://github.com/suma ...

随机推荐

- 【Heaven Cow与God Bull】题解

题目 Description __int64 ago,there's a heaven cow called sjy... A god bull named wzc fell in love with ...

- awk基础学习

2019-12-20 需要巧记,很多格式,学习难度:grep.sed.awk awk知识概述 1三剑客awk命令介绍2三剑客awk命令执行原理语法结构3三剑客awk命令实操练习查询替换信息排除(取反) ...

- Android 拖拽功能的使用实例

图片的拖拉功能是处理图片进一个有用且常用的功能,由于手机屏幕尺寸的限制,往往无法在手机上一次性的显示一张比较大的图片,也就是说,我们在手机上一次性只能看到图片的一部分,此时就可以使用图片的拖动功能来拖 ...

- Linux用户和用户组指令

1.创建用户 >useradd username 创建用户 >passwd username 给用户设置密码 ======================================= ...

- SQL字串截取函数编写及应用

SQL里面一种用来截取字符串的方法,用的是表函数实现字符串截取并应用的SQL操作语句中. .截取字符串表函数 ALTER FUNCTION [dbo].[SplitToTable] ( -- Add ...

- [CSP-S模拟测试]:木叶下(图论)

题目传送门(内部题77) 输入格式 第一行一个整数$n$,表示原先的树的点数接下来$n-1$行每行两个整数$a,b$,表示原先的树上的$n-1$条边,保证这$n-1$条边形成一棵树. 接下来一行一个整 ...

- mui初级入门教程(四)— 再谈webview,从小白变“大神”!

文章来源:小青年原创发布时间:2016-06-05关键词:mui,html5+,webview转载需标注本文原始地址: http://zhaomenghuan.github.io/#!/blog/20 ...

- 阶段1 语言基础+高级_1-2 -面向对象和封装_16this关键字的作用

this主要是在重名的情况下 ,起到区分的效果 新建demo04的包,里面新建类Person 通过this.进行区分 this关键字可以解决重名 分不开的问题 这里的person调用的sayHello ...

- laravel使用artisan报错SQLSTATE[42S02]: Base table or view not found: 1146

说明你在应用初始化阶段使用到了数据库层面的东西,然而当时数据库不存在这个表/字段,所以会报错 需要在初始化比如 config 目录配置中,使用了数据库,在使用前需要添加一层判断,如果不存在 你需要用到 ...

- vue-router路由详细

由于Vue在开发时对路由支持的不足,于是官方补充了vue-router插件.vue的单页面应用是基于路由和组件的,路由用于设定访问路径,并将路径和组件映射起来.传统的页面应用,是用一些超链接来实现 ...