6层PCB设计技巧和步骤

6层PCB设计技巧和步骤

一、原理图的编辑

6层板由于PCB板中可以有两层地,所以可以将模拟地和数字地分开。对于统一地还是分开地,涉及到电磁干扰中信号的最小回流路径问题,绘制完原理图,别忘检查错误和查看封装管理器,检查元器件封装。

二、新建PCB文件、设置层结构

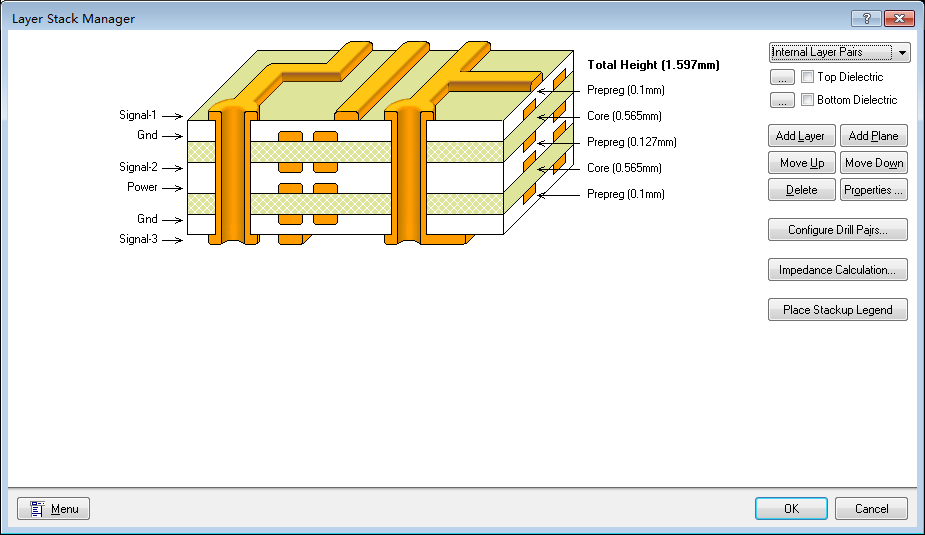

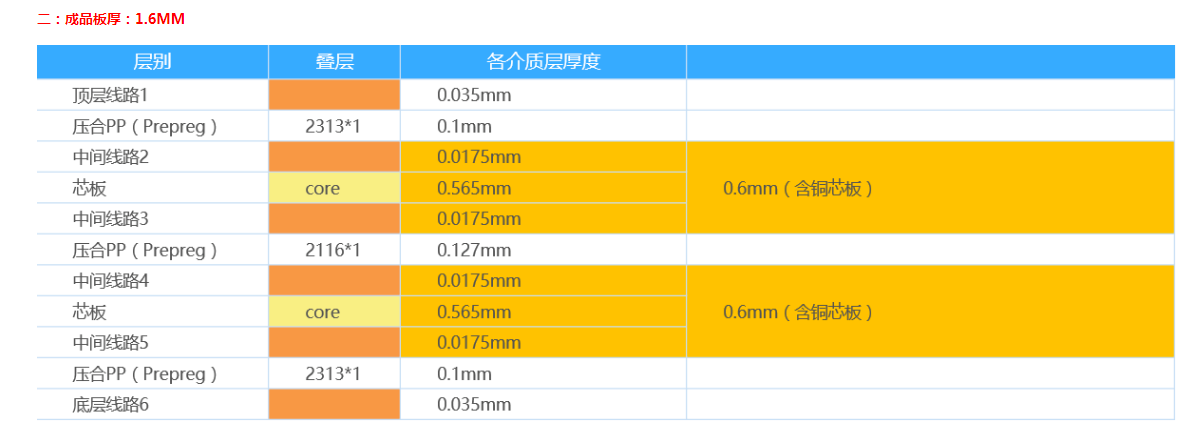

新建好后,就可以将原理图网络表导入到PCB文件。接下来要做的就是层的结构设置(layer stack manager),add layer是添加中间信号层,add plane是添加内部电源和内部地层。中间信号层和顶层、底层一样,放置信号线的,信号线就代表铜,没有信号线的地方就是绝缘的。而内部电源和地层,生成的是一层铜模,在分割内电层时使用的line,代表腐蚀掉的铜,也就是说深红的代表被腐蚀掉的,其他区域代表铜模。还有一点就是电源层和主地层应紧密耦合,可取间隔5mil(prepreg)。

三、布局

布局主要的原则是做好分区,也就是模拟器件和数字器件的分区,这样可以减少干扰,因为数字信号产生的干扰大,抗干扰也强,而模拟信号产生的干扰相对小点,但易受数字信号干扰。还有一点就是注意工作电压不同的元器件布局,压差大的器件应相距远。对于一些芯片的去耦电容,离引脚越近越好。其他要注意的就是相同网络的引脚靠近,注意布局的美观。

原则上3层信号层,3层电源层,其中GND为2、5两层,3、4中间层为Power和中间信号层。若中间信号层走线较少,可适当在中间信号层对Power进行敷铜。

每个信号层都与内电层, 相邻,没有直接相邻的信号层,避免了层间信号的串扰;

高速信号线可布置到信号层5上,这样它就可以被地层和电源层有效的屏蔽起来。

四、地平面的制作

由于六层板有两层地,AGND与DGND分开,分别位于第二层和第四层,所以对地网络的操作就相对容易点。把顶层和地层元器件的地网络引脚,用导线引出,接过孔连到相应地网络即可(考虑制作成本,尽量少用盲孔、埋孔,用焊盘代替通孔)。连接过程中尽量少用些焊盘,因为焊盘会带来电容效应,增大干扰。

五、电源平面的制作

由于多层板不会只有一个工作电压值,所以电源层一般都需要进行分割。分割具体步骤如下:

1、高亮显示某个电压网络,切换到内电源层,使用line,绘制出一个封闭的图形,该封闭的区域就是该电压的网络;

2、把顶层、地层的引脚用导线引出,通过焊盘连到内电源层;3、绘制下一个电源网络,line就是两个网络的分割线,是被腐蚀掉的部分。内电层应注意:电压差大的区域分割距离应较宽;不用的铜模可以放置plane,以在制作时将其区域腐蚀掉;不要将焊盘放置在分割线上,以影响其与内电层的接触。

六、走线

做好电源层和地层,接下来就可以进行信号线的走线了。走线时重要的高速信号线最好走在内信号层,还有一个原则就是信号要走在自己的地层上,例如,若顶层走的多数是模拟信号,则第二层最好设置为AGND。由于层的结构在前面已经设置好,所以在走信号线时需考虑这一点。此外在走线时,还需适当调整元器件布局,以方便走线。顶层与地层的走线与两层板没有区别。

对于内信号层,走线方法就是导线—焊盘—内电层。 对于DDR FPGA FPC排线等进行优先布局和布线。使用5mil(0.127mm)的信号线走线线宽,电源线采用(16mil)0.4mm的线宽,理论上10mil的线可过电流为1A。

1、对于重要信号,要进行差分布线,设定布线组,并进行绕等长处理。

2、对于FPGA等多引脚功能无关引脚,可设置成组,方便进行swap pin操作。

3、对于BGA封装器件,先进行排线,引出最外侧两层引脚,然后进行排线,对于内层较难引出排线的引脚,可适当引到其它层。

4、对于DDR数据线尽量保证数据线为一簇,时钟线与数据线隔离。

5、两个芯片的连线最多经过两个过孔。

6、可以选中原理图,然后链接到PCB,通过这样的方式,可以有效选中特定的元器件。

7、对于不能再引脚旁,引出线的,可以引到外面,更远的地方引线。

8、对于BGA中的GND和Power,在布线的时候就要引出线,避免走线过密,出现未连接的GND和Power。

在元器件不密集,存在一定的空区域时,最好进行铺地,铺地也分AGND与DGND,所以应分开进行局部铺地操作。对于补泪滴,一般都需要进行。

七、DRC检查

这一步非常重要,在板子绘制完成后,必须进行,检查是否有违背规则而未发现的地方。

6层PCB设计技巧和步骤的更多相关文章

- 硬件十万个为什么——运放篇(五)PCB设计技巧

1.在PCB设计时,芯片电源处旁路滤波等电容应尽可能的接近器件.典型距离是小于3MM 2.运算放大器芯片电源处的小陶瓷旁路电容在放大器处于输入高频信号时能够为放大器的高频特性提供能量电容值的选择依据输 ...

- 电子技术经典资料汇总:PCB设计篇

电子技术经典资料汇总:PCB设计篇,下面的链接是一个一个的文件下载的,也是压缩包的内容,只不过我把他们给汇总成了一个压缩包,方便大家下载,还有更多电子技术必备基础资料,通信无线类的,C语言篇的,关于电 ...

- 《FPGA全程进阶---实战演练》第三章之PCB设计之过孔

在画电路板时,往往需要过孔来切换层之间的信号.在PCB设计时,过孔的选择有盲孔,埋孔,通孔.如图3.1所示.盲孔是在表面或者底面打通到内层面,但不打穿,埋孔是在内层面之间的孔,不在表面和底面漏出:通孔 ...

- AD9 如何画4层pcb板

新建的PCB文件默认的是2层板,教你怎么设置4层甚至更多层板. 在工具栏点击Design-->Layer Stack Manager.进入之后显示的是两层板,添加为4层板,一般是先点top la ...

- PCB设计中新手和老手都适用的七个基本技巧和策略

本文将讨论新手和老手都适用的七个基本(而且重要的)技巧和策略.只要在设计过程中对这些技巧多加注意,就能减少设计回炉次数.设计时间和总体诊断难点. 技巧一:注重研究制造方法和代工厂化学处理过程 在这个无 ...

- 开关电源PCB设计中的布线技巧

开关电源PCB设计中的布线技巧关键字:布线 开关电源 走线 一.引言 开关电源是一种电压转换电路,主要的工作内容是升压和降压,广泛应用于现代电子产品.因为开关三极管总是工作在 “开” 和“关” 的状态 ...

- Protel99se教程九:protel99se中PCB设计的高级应用

在上一节我们PCB资源网的protel99se教程当中,我们给大家讲解了在protel99se进行原理图设计中的一些高级应用技巧,在这一节protel99se教程当中,我们将给大家讲解的是,在prot ...

- 用于COB工艺的PCB设计指导

绑定角度尽量在45°之内,多于这个角度,绑定时候,银线不好打入焊盘.而且打入焊盘的尾部可能短路到相邻的焊盘,绑定焊盘之间的间距一般在4MIL为极限,半场的工艺一般就这样了.而且焊盘离被绑定的IC引脚最 ...

- PCB设计资料:看到最后才知道是福利

參考资料 通过以下的关键词直接从网络上Google或Baidu就能非常easy的找到以下的资料,这里仅仅是以參考文献的方式做一个整理以及简单的说明. 刘雅芳,张俊辉. 抗干扰角度分析六层板的布线技巧. ...

随机推荐

- 冒泡排序算法-python

冒泡排序:每两个相互比较,总是选出大的相互交换,直至最后选出该列表中最大的数字 def bubbleSort(myList): for i in range(len(myList)-1):#一共进行几 ...

- HashMap接口测试

package com.iotek.map; import java.util.Collection;import java.util.HashMap;import java.util.Map;imp ...

- 2,ArrayList

一,ArrayList简介 1,ArrayList 是一个数组队列,相当于动态数组.与Java中的数组相比,它的容量能动态增长. 2,ArrayList 继承了AbstractList,实现了List ...

- postman 简单使用教程

Postman 安装 Postman 接口测试(Collection) Postman 接口测试(测试用例)Postman 接口测试(变量与参数化)Postman 接口测试(非 UI 运行模式 ...

- spash和selenium浅析

Splash是什么: Splash是一个Javascript渲染服务.它是一个实现了HTTP API的轻量级浏览器,Splash是用Python实现的,同时使用Twisted和QT.Twisted(Q ...

- CodeForces - 587E[线段树+线性基+差分] ->(线段树维护区间合并线性基)

题意:给你一个数组,有两种操作,一种区间xor一个值,一个是查询区间xor的结果的种类数 做法一:对于一个给定的区间,我们可以通过求解线性基的方式求出结果的种类数,而现在只不过将其放在线树上维护区间线 ...

- 移动端rem布局屏幕适配插件(放js中便可使用)

/* doc:不用管:document对象 win:不用管:window对象 design:注意:设计稿的尺寸/物理像素*/ (function (doc, win,design) {// alert ...

- 使div弹窗可拖拽指令

在项目开发过程中,有些情况dialog弹窗,直接使用div模拟弹窗效果,并需要支持div可拖拽. div模拟弹窗效果: (1)在用于存放指令的文件夹内,新建js文件,命名为:drag.js.具体代码如 ...

- __I、 __O 、__IO是什么意思?怎么用?

出处:http://www.chuxue123.com/forum.php?mod=viewthread&tid=122&ctid=3 __I. __O .__IO是什么意思?这是ST ...

- kali 修改MariaDB密码

use mysql; update user set authentication_string=PASSWORD("") where User='root'; update us ...