Vscode生成verilog例化

前言

veirlog模块例化的时候,辣么多的信号端子,手动例化又慢又容易出错,葵花妈妈开课啦,孩子手残老犯错怎么办?

当然是脚本一劳永逸,妈妈再也不担心手残党。

流程

(1)在vscode中安装如下插件。

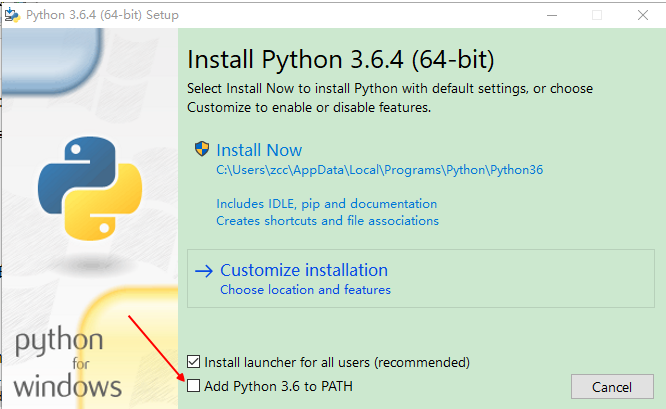

(2)在电脑中安装python3以上的环境。

下载地址:https://www.python.org/downloads/release/python-373/

安装记得一定要勾选添加路径,记得管理员安装。重启你的电脑。

在cmd窗口输入python即可验证是否安装成功!

(3)安装chardet。为确保插件可用,这个需要安装。

参考链接:https://blog.csdn.net/sinat_28631741/article/details/80483064

方式一 源码按照:

第一步:下载压缩文件,例如: 'chardet-3.0.4.tar.gz';

第二步:解压文件到python安装位置下的‘site-packages’目录下,例如:‘D:\python2.7\Lib\site-packages’;

第三步:打开终端命令窗口,进入解压的‘chardet’目录下,执行命令:python setup.py install

(4)修改插件的原始py文件,觉得开发者的py有瑕疵,让帅气的同事重新整了个,把以下代码替换进原始py文件即可。

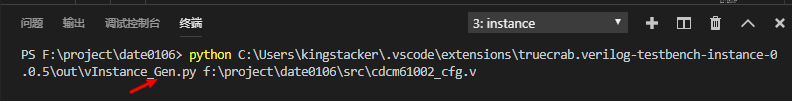

在打开v文件的vscode下按ctrl+p,输入instance可出现下述界面。

替换此py文件的代码即可。

#! /usr/bin/env python '''

vTbgenerator.py -- generate verilog module Testbench

generated bench file like this: fifo_sc #(

.DATA_WIDTH ( 8 ),

.ADDR_WIDTH ( 8 )

)

u_fifo_sc (

.CLK ( CLK ),

.RST_N ( RST_N ),

.RD_EN ( RD_EN ),

.WR_EN ( WR_EN ),

.DIN ( DIN [DATA_WIDTH-1 :0] ),

.DOUT ( DOUT [DATA_WIDTH-1 :0] ),

.EMPTY ( EMPTY ),

.FULL ( FULL )

); Usage:

python vTbgenerator.py ModuleFileName.v '''

import random

import re

import sys

from queue import Queue import chardet def delComment(Text):

""" removed comment """

single_line_comment = re.compile(r"//(.*)$", re.MULTILINE)

multi_line_comment = re.compile(r"/\*(.*?)\*/", re.DOTALL)

Text = multi_line_comment.sub('\n', Text)

Text = single_line_comment.sub('\n', Text)

return Text def delBlock(Text):

""" removed task and function block """

Text = re.sub(r'\Wtask\W[\W\w]*?\Wendtask\W', '\n', Text)

Text = re.sub(r'\Wfunction\W[\W\w]*?\Wendfunction\W', '\n', Text)

return Text def findName(inText):

""" find module name and port list"""

p = re.search(r'([a-zA-Z_][a-zA-Z_0-9]*)\s*', inText)

mo_Name = p.group(0).strip()

return mo_Name def paraDeclare(inText, portArr):

""" find parameter declare """

pat = r'\s' + portArr + r'\s[\w\W]*?[;,)]'

ParaList = re.findall(pat, inText) return ParaList def portDeclare(inText, portArr):

"""find port declare, Syntax:

input [ net_type ] [ signed ] [ range ] list_of_port_identifiers return list as : (port, [range])

"""

port_definition = re.compile(

r'\b' + portArr +

r''' (\s+(wire|reg)\s+)* (\s*signed\s+)* (\s*\[.*?:.*?\]\s*)*

(?P<port_list>.*?)

(?= \binput\b | \boutput\b | \binout\b | ; | \) )

''',

re.VERBOSE | re.MULTILINE | re.DOTALL

) pList = port_definition.findall(inText)

t = []

for ls in pList:

if len(ls) >= 2:

t = t + portDic(ls[-2:])

return t def portDic(port):

"""delet as : input a =c &d;

return list as : (port, [range])

"""

pRe = re.compile(r'(.*?)\s*=.*', re.DOTALL) pRange = port[0]

pList = port[1].split(',')

pList = [i.strip() for i in pList if i.strip() != '']

pList = [(pRe.sub(r'\1', p), pRange.strip()) for p in pList] return pList def formatPort(AllPortList, isPortRange=1):

PortList = AllPortList str = ''

if PortList != []:

l1 = max([len(i[0]) for i in PortList])+2

l3 = max(18, l1) strList = []

str = ',\n'.join([' ' * 4 + '.' + i[0].ljust(l3)

+ '(' + (i[0]) + ')' for i in AllPortList])

strList = strList + [str] str = ',\n\n'.join(strList) return str def formatDeclare(PortList, portArr, initial=""):

str = '' if PortList != []:

str = '\n'.join([portArr.ljust(4) + ' '+(i[1]+min(len(i[1]), 1)*' '

+ i[0]) + ';' for i in PortList])

return str def formatPara(ParaList):

paraDec = ''

paraDef = ''

if ParaList != []:

s = '\n'.join(ParaList)

pat = r'([a-zA-Z_][a-zA-Z_0-9]*)\s*=\s*([\w\W]*?)\s*[;,)]'

p = re.findall(pat, s) l1 = max([len(i[0]) for i in p])

l2 = max([len(i[1]) for i in p])

paraDec = '\n'.join(['parameter %s = %s;'

% (i[0].ljust(l1 + 1), i[1].ljust(l2))

for i in p])

paraDef = '#(\n' + ',\n'.join([' .' + i[0].ljust(l1 + 1)

+ '( ' + i[1].ljust(l2)+' )' for i in p]) + ')\n'

return paraDec, paraDef def portT(inText, ioPadAttr):

x = {}

count_list = []

order_list = []

for i in ioPadAttr:

p = port_index_list(inText, i)

for j in p:

count_list.append(j)

x[j] = i

count_list = quick_sort(count_list, 0, len(count_list)-1)

for c in count_list:

order_list.append(x.get(c))

return order_list def quick_sort(myList, start, end):

if start < end:

i, j = start, end

base = myList[i]

while i < j:

while (i < j) and (myList[j] >= base):

j = j - 1 myList[i] = myList[j] while (i < j) and (myList[i] <= base):

i = i + 1

myList[j] = myList[i]

myList[i] = base quick_sort(myList, start, i - 1)

quick_sort(myList, j + 1, end)

return myList def formatPort_order(padAttr, orderList): for p in padAttr:

q = Queue()

for i in padAttr.get(p):

q.put(i)

padAttr[p] = q

AllPortList = []

for o in orderList:

AllPortList.append(padAttr.get(o).get())

return AllPortList def port_index_list(intext, text):

l = []

t = intext

index = t.find(text)

while index > -1:

t = t.replace(text, random_str(len(text)), 1)

l.append(index)

index = t.find(text)

return l def random_str(size):

s = ''

for i in range(size):

s += str(random.randint(0, 9))

return s def getPortMap(AllPortList, ioPadAttr):

if len(AllPortList) != len(ioPadAttr):

return p_map = {}

for i in range(len(AllPortList)):

p_map[ioPadAttr[i]] = AllPortList[i]

return p_map def writeTestBench(input_file):

""" write testbench to file """

with open(input_file, 'rb') as f:

f_info = chardet.detect(f.read())

f_encoding = f_info['encoding']

with open(input_file, encoding=f_encoding) as inFile:

inText = inFile.read() # removed comment,task,function

inText = delComment(inText)

inText = delBlock(inText) # moduel ... endmodule #

moPos_begin = re.search(r'(\b|^)module\b', inText).end()

moPos_end = re.search(r'\bendmodule\b', inText).start()

inText = inText[moPos_begin:moPos_end] name = findName(inText)

paraList = paraDeclare(inText, 'parameter')

paraDec, paraDef = formatPara(paraList) ioPadAttr = ['input', 'output', 'inout']

orlder = portT(inText, ioPadAttr)

input = portDeclare(inText, ioPadAttr[0])

output = portDeclare(inText, ioPadAttr[1])

inout = portDeclare(inText, ioPadAttr[2]) portList = formatPort(formatPort_order(

getPortMap([input, output, inout], ioPadAttr), orlder)) input = formatDeclare(input, 'reg')

output = formatDeclare(output, 'wire')

inout = formatDeclare(inout, 'wire') # write Instance # module_parameter_port_list

if(paraDec != ''):

print("// %s Parameters\n%s\n" % (name, paraDec)) # list_of_port_declarations

#print("// %s Inputs\n%s\n" % (name, input))

#print("// %s Outputs\n%s\n" % (name, output))

#if(inout != ''):

# print("// %s Bidirs\n%s\n" % (name, inout))

print("\n")

# UUT

print("%s %s inst_%s (\n%s\n);" % (name, paraDef, name, portList)) if __name__ == '__main__':

writeTestBench(sys.argv[1])

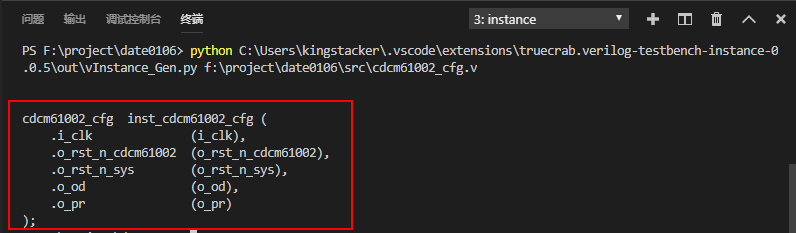

(5)享受一下吧。

比如我们有如下代码:

crtl+p,输入instance,按回车即可。

复制粘贴大法好。

以上。

Vscode生成verilog例化的更多相关文章

- Xilinx Spartan6常用资源Verilog例化

// DSP48A1 : In order to incorporate this function into the design, // Verilog : the following insta ...

- 利用python自动生成verilog模块例化模板

一.前言 初入职场,一直忙着熟悉工作,就没什么时间更新博客.今天受“利奇马”的影响,只好宅在家中,写写技术文章.芯片设计规模日益庞大,编写脚本成了芯片开发人员必要的软技能.模块端口动不动就几十上百个, ...

- Verilog与VHDL的混合模块例化

1,大小写与转义 对VHDL解释器而言,对于模块名和端口名, (1) 若有转义 a) 先不考虑转义,寻找与字符串完全相同的VHDL模块: 若找不到: b) 考虑转义,寻找对应的Verilog模块. ( ...

- Kotlin入门(28)Application单例化

Application是Android的又一大组件,在App运行过程中,有且仅有一个Application对象贯穿应用的整个生命周期,所以适合在Application中保存应用运行时的全局变量.而开展 ...

- Xilinx 7系列例化MIG IP core DDR3读写

昨晚找了一下,发现DDR3读写在工程上多是通过例化MIG,调用生成IPcore的HDL Functional Model.我说嘛,自己哪能写出那么繁琐的,不过DDR读写数据可以用到状态机,后期再添砖加 ...

- 62.在cdc文件上某些例化模块看不到的原因

比如在顶层文件中,例化了几个模块,综合后打开cdc文件,会在structure/net中少几个例化模块,即看不到,但在顶层文件中还是存在的,只是ISE软件综合的问题而已,原因是在顶层或子模块中,有些应 ...

- Quartus中例化工程

一般的例化工程,需要将要例化的对象的硬件语言放入到当前工程中,比如A要例化B,需要将B的编程文件加入当前工程进来. 还有一种方法不用这么麻烦,A工程用要例化B时,在library添加B的工程路径,就可 ...

- testbench中$display查看例化model里面信号方法以及$realtime用法

前言 此为测试语法,不可综合: 流程: 1.在tb中可以这么写,检测clk_t_en的高电平,输出仿真时间位置,想查看的cnt_t是底层模块中的.这么会使得时间延迟一个周期: always @(pos ...

- 基于MATLAB2016b图形化设计自动生成Verilog语言的积分模块及其应用

在电力电子变流器设备中,常常需要计算发电量,由于电力电子变流器设备一般是高频变流设备,所以发电量的计算几乎时实时功率的积分,此时就会用到一个积分模块.发电量计算的公式如下:Q=∫P. FPGA由于其并 ...

随机推荐

- javascript小记四则:用JS写一个滚动横条文字,可以根据需要进行修改;

网页上的一些广告文字,一直会滚动是怎么做到的,今天给大家演示下,非常简单,源码如下(本案例是在.net平台上,但HTML是通用的): <!DOCTYPE html> <html> ...

- 学JAVA第十七天,接口与抽象方法

JAVA接口可以让代码更加有合理的规范性,就想一个项目小组,组长要负责把成员的代码整合,但是每个成员写的方式都是按照他们自己的想法来写的, 所以,整合起来就非常麻烦. 但是,如果我们的组长制作了一个接 ...

- MVC各层介绍使用---初步理解

controller层负责请求的转发,以及数据的转发: service层负责项目的业务逻辑处理: dao层负责与数据库的数据查询与连接,其中的bean层负责数据的整理转发: view层负责JSP,ht ...

- webstorm 2018.2.3 cmd+w无法关闭文件

- animate-queue和step-animate

Step-animate: 分为3部分:{配置},{step:function(){...},duration:1000} <div id="warpper" style=& ...

- 基于Html5 Plus + Vue + Mui 移动App 开发(二)

基于Html5 Plus + Vue + Mui 移动App 开发(二) 界面效果: 本页面采用Html5 Plus + Vue + Mui 开发移动界面,本页面实现: 1.下拉刷新.上拉获取更多功能 ...

- 报表平台对CRM系统价值几何

CRM系统即客户关系管理系统,其利用信息科学技术实现市场营销.销售.服务等活动自动化,使企业能高效地为客户提供周到的服务,以提升客户满意度与忠诚度为目的的一种管理经营方式.而CRM报表平台作为一个枢纽 ...

- C#基础委托回顾

C#基础委托回顾 前言 快忘记了. 委托的特点 委托类似于 C++ 函数指针,但它们是类型安全的. 委托允许将方法作为参数进行传递. 委托可用于定义回调方法. 委托可以链接在一起:例如,可以对一个事件 ...

- Spark 基本函数学习笔记一

Spark 基本函数学习笔记一¶ spark的函数主要分两类,Transformations和Actions. Transformations为一些数据转换类函数,actions为一些行动类函数: ...

- 使用Server Trigger保护重要的数据库对象

一 .Server Trigger的简单介绍 在SQL Server数据库中,Server Trigger 是一种特殊类型的存储过程,它可以对特定表.视图或存储中的必然事件自动响应,不由用户调用.创建 ...