FPGA - 认识FPGA

一、何为FPGA?

FPGA,英文全拼:Field-Programmable Gate Array

现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

二、FPGA生产厂家有哪些?

Altera(被Intel收购),开发平台Quartus

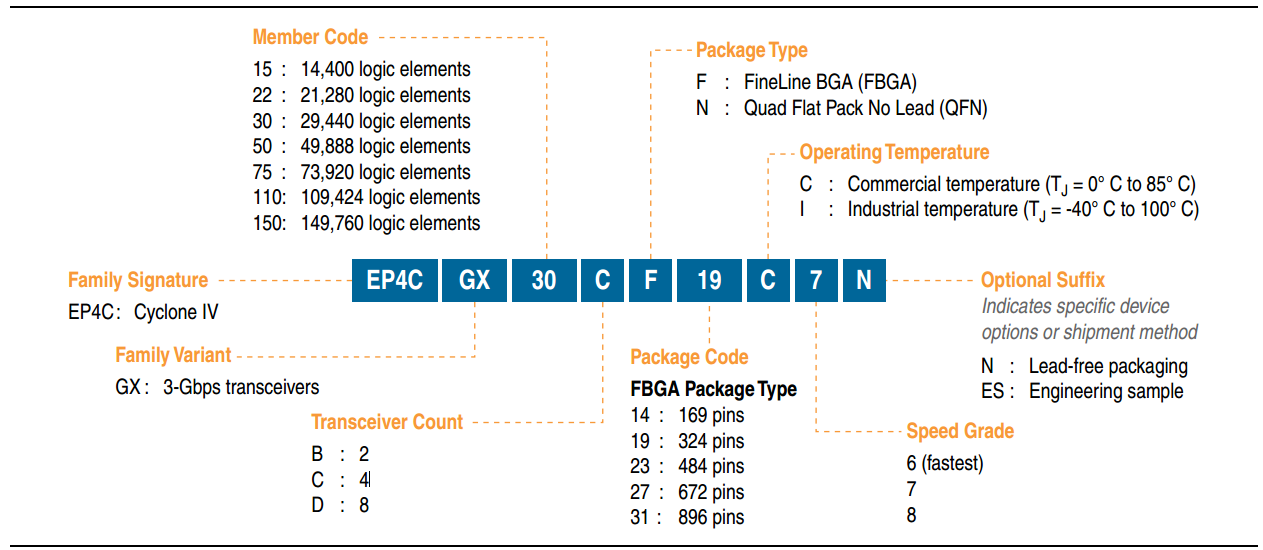

下图是Altera Cyclone IV的产品信息说明

Cyclone IV GX系列资源列表

xilinx(赛灵思),开发平台SDSoC

Actel ,开发平台是Libero

Lattice,开发平台是ispLEVER

Atmel

三、FPGA内部组成

FPGA 芯片主要由 6 部分完成,分别为 :

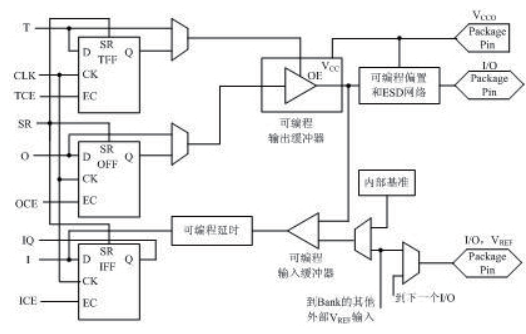

1.可编程输入输出单元(IOB Input Output Block)

可编程输入 / 输出单元简称 I/O 单元,是芯片与外界电路的接口部分,完成不同电气特性下对输入 / 输出信号的驱动与匹配要求,其示意结构如图所示。FPGA 内的 I/O 按组分类,每组都能够独立地支持不同的 I/O标准。通过软件的灵活配置,可适配不同的电气标准与 I/O 物理特性,可以调整驱动电流的大小,可以改变上、下拉电阻。目前,I/O 口的频率也越来越高,一些高端的 FPGA 通过 DDR 寄存器技术可以支持高达 2Gbps 的数据速率。

外部输入信号可以通过 IOB 模块的存储单元输入到 FPGA 的内部,也可以直接输入 FPGA 内部。当外部输入信号经过 IOB 模块的存储单元输入到 FPGA 内部时,其保持时间 (Hold Time) 的要求可以降低,通常默认为 0。为了便于管理和适应多种电器标准,FPGA 的 IOB 被划分为若干个组 (bank),每个 bank 的接口标准由其接口电压 VCCO 决定,一个 bank 只能有一种 VCCO,但不同 bank 的 VCCO 可以不同。只有相同电气标准的端口才能连接在一起,VCCO 电压相同是接口标准的基本条件。

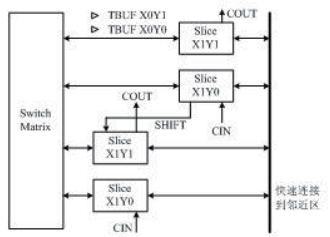

2.可配置逻辑块(CLB)

CLB 是 FPGA 内的基本逻辑单元。CLB 的实际数量和特性会依器件的不同而不同,但是每个 CLB 都包含一个可配置开关矩阵,此矩阵由 4 或 6 个输入、一些选型电路 ( 多路复用器等 ) 和触发器组成。 开关矩阵是高度灵活的,可以对其进行配置以便处理组合逻辑、移位寄存器或 RAM。在赛灵思公司公司的 FPGA 器件中,CLB 由多个 ( 一般为 4 个或 2 个 ) 相同的 Slice 和附加逻辑构成,如图 所示。每个 CLB 模块不仅可以用于实现组合逻辑、时序逻辑,还可以配置为分布式 RAM 和分布式 ROM。

3.完整的时钟管理

提供数字时钟管理和相位环路锁定。业内大多数 FPGA 均提供数字时钟管理 ( 赛灵思公司的全部 FPGA 均具有这种特性 )。赛灵思公司推出最先进的 FPGA 提供数字时钟管理和相位环路锁定。相位环路锁定能够提供精确的时钟综合,且能够降低抖动,并实现过滤功能。

4.嵌入块式 RAM

块RAM可被配置为单端口RAM、双端口RAM、内容地址存储器(CAM)以及FIFO等常用存储结构。单片块RAM的容量为18k比特,即位宽为18比特、深度为1024,可以根据需要改变其位宽和深度,但要满足两个原则:首先,修改后的容量(位宽 深度)不能大于18k比特;其次,位宽最大不能超过36比特。当然,可以将多片块RAM级联起来形成更大的RAM,此时只受限于芯片内块RAM的数量,而不再受上面两条原则约束。

5.丰富的布线资源

FPGA芯片内部有着丰富的布线资源,根据工艺、长度、宽度和分布位置的不同而划分为4类不同的类别。第一类是全局布线资源,用于芯片内部全局时钟和全局复位/置位的布线;第二类是长线资源,用以完成芯片 Bank间的高速信号和第二全局时钟信号的布线;第三类是短线资源,用于完成基本逻辑单元之间的逻辑互连和布线;第四类是分布式的布线资源,用于专有时钟、复位等控制信号线。

6.内嵌的底层功能单元和内嵌专用硬件模块

内嵌功能模块主要指DLL(Delay Locked Loop)、PLL(Phase Locked Loop)、DSP 等软处理核(Soft Core)。现在越来越丰富的内嵌功能单元,使得单片FPGA 成为了系统级的设计工具,使其具备了软硬件联合设计的能力,逐步向SOC 平台过渡。

DLL 和PLL 具有类似的功能,可以完成时钟高精度、低抖动的倍频和分频,以及占空比调整和移相等功能。赛灵思公司生产的芯片上集成了DCM 和DLL,Altera 公司的芯片集成了PLL,LatTIce 公司的新型芯片上同时集成了PLL 和DLL。PLL 和DLL 可以通过IP 核生成的工具方便地进行管理和配置。

内嵌专用硬核是相对底层嵌入的软核而言的,指FPGA 处理能力强大的硬核(Hard Core),等效于ASIC 电路。为了提高FPGA 性能,芯片生产商在芯片内部集成了一些专用的硬核。例如:为了提高FPGA 的乘法速度,主流的FPGA 中都集成了专用乘法器;为了适用通信总线与接口标准,很多高端的FPGA 内部都集成了串并收发器(SERDES),可以达到数十Gbps 的收发速度。

FPGA - 认识FPGA的更多相关文章

- 如何学习FPGA?FPGA学习必备的基础知识

如何学习FPGA?FPGA学习必备的基础知识 时间:2013-08-12 来源:eepw 作者: 关键字:FPGA 基础知识 FPGA已成为现今的技术热点之一,无论学生还是工程师都希望 ...

- FPGA的引脚VCCINT 、VCCIO VCCA

首先是看到FPGA在配置的时候有三种不同的电VCCINT .VCCIO VCCA,于是就查了下有什么不同: FPGA一般会有许多引脚,那它们都有什么用呢? VCCINT为施加于 FPGA 内核逻辑的电 ...

- FPGA与simulink联合实时环路系列——实验一 测试

实验一 测试 实验内容 在simulink创建测试模块,通过测试模块产生信号,再传送到FPGA,FPGA读出后再将信号无处理传送回simulink进行显示.由此来测试整个硬件在环的功能是否正常,并且熟 ...

- 谈谈我对DSP和FPGA的看法

1.DSP 在DSP里,你是一个软件设计者,硬件已经完全固化,你所要做的,就是在这个固定的硬件平台实现算法改进与优化, DSP的关键优势在于能够运行多种算法的灵活性: 2.FPGA 对于FPGA来说, ...

- CPLD VS FPGA

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL.GAL.CPLD等可编程器件的基础上进一步发展的产物.它是作为专用集成电路(ASIC)领域中的 ...

- 【原创】MIPS·Verilog·FPGA

时至今日,终于将全部的计划55条MIPS指令在FPGA上全部验证完毕,通过这近一个月的不断的修改调试.修改调试,我对整个流程对MIPS有了深刻的体会和认识.借着刚刚现阶段任务的兴奋和短暂的空闲时间,将 ...

- 《那些年,我们拿下FPGA》做笔记

spld.cpld和fpga等可不管什么样的逻辑是大自然来实现.任何逻辑可以由多项式来表示(要么逼关闭).比多项式乘法和处理操作仅此而已. 而就.您可以在门线上用.或门添加剂. fpga扩展架构SOP ...

- FPGA计算3行同列数据之和

实验:FPGA计算3行同列数据之和 实验要求:PC机通过串口发送3行数据(一行有56个数据,3行共有56*3=168个数据)给FPGA,FPGA计算3行同一列数据的和,并将结果通过串口返回给上位机. ...

- 基于FPGA的Uart接收图像数据至VGA显示

系统框图 前面我们设计了基于FPGA的静态图片显示,接下来我们来做做基于FPGA的动态图片显示,本实验内容为:由PC端上位机软件通过串口发送一幅图像数据至FPGA,FPGA内部将图像数据存储,最后扫描 ...

随机推荐

- CentOS安装jdk的三种方法

方法一:手动解压JDK的压缩包,然后设置环境变量 方法二:用yum安装JDK,(全称为 Yellow dog Updater, Modified)是一个在Fedora和RedHat以及CentOS中的 ...

- js instanceof 检测某个对象是否是另一个对象的实例

例如File对象 $("#file").change(function(){ console.log($(this)[0].files[0]) console.log($(this ...

- PAT Basic 1069. 微博转发抽奖(20)

小明PAT考了满分,高兴之余决定发起微博转发抽奖活动,从转发的网友中按顺序每隔N个人就发出一个红包.请你编写程序帮助他确定中奖名单. 输入格式: 输入第一行给出三个正整数M(<= 1000).N ...

- Oracle数据库中字符型字段按数字排序

今天在转换数据时,遇到了一个主键排序的问题.字符型的主键,保存的都是数字,数据导过来以后发现数据排序都是乱的,就想着按数字规则排序. 但发现to_number总是报错,就想着里面应该是有字符存在.后来 ...

- Git Flow,Git团队协作最佳实践

规范的Git使用 Git是一个很好的版本管理工具,不过相比于传统的版本管理工具,学习成本比较高, 实际开发中,如果团队成员比较多,开发迭代频繁,对Git的应用比较混乱,会产生很多不必要的冲突或者代码丢 ...

- js条件语句初步练习

var a=18 if(a<10){ alert("便宜") } else{ ...

- python基础——字符串、编码、格式化

1.三种编码:ascii Unicode utf8 2.字符串和编码数字的两个函数:ord(字符转数字ord(‘A’)=65)和 chr(数字转字符chr(65)=A) 3.bytes存储编码,记住两 ...

- net core体系-web应用程序-4asp.net core2.0 项目实战(1)-1目录

Asp.Net Core 2.0 项目实战(1) NCMVC开源下载了 Asp.Net Core 2.0 项目实战(2)NCMVC一个基于Net Core2.0搭建的角色权限管理开发框架 Asp.Ne ...

- 从入门到深入FIDDLER 2

在开发的过程中使用过不少的HTTP网络抓包工具,如:HTTPAnalyzer,HttpWatch. Fiddler几乎囊括了大部分的抓包请求,当然最给力的还是它的断点调试功能,尤其还有使用本地文件代替 ...

- php 操作数据库

$datetoday = date('Y-m-d'); $datetime = $thedate; $data_info = $data; $db = array( 'dsn' => 'mysq ...