xilinx fpga 生成3*3窗口

在写滤波程序的时候在网上看了好几篇大佬的笔记,都有提到使用3*3窗口,由于小白一个,看到复杂的理论就惧怕的不行。但是现在不得不上,自己调用移位寄存器ip核然后做了个3*3窗口出来,自己动手作出来忽然感觉到也不难嘛。

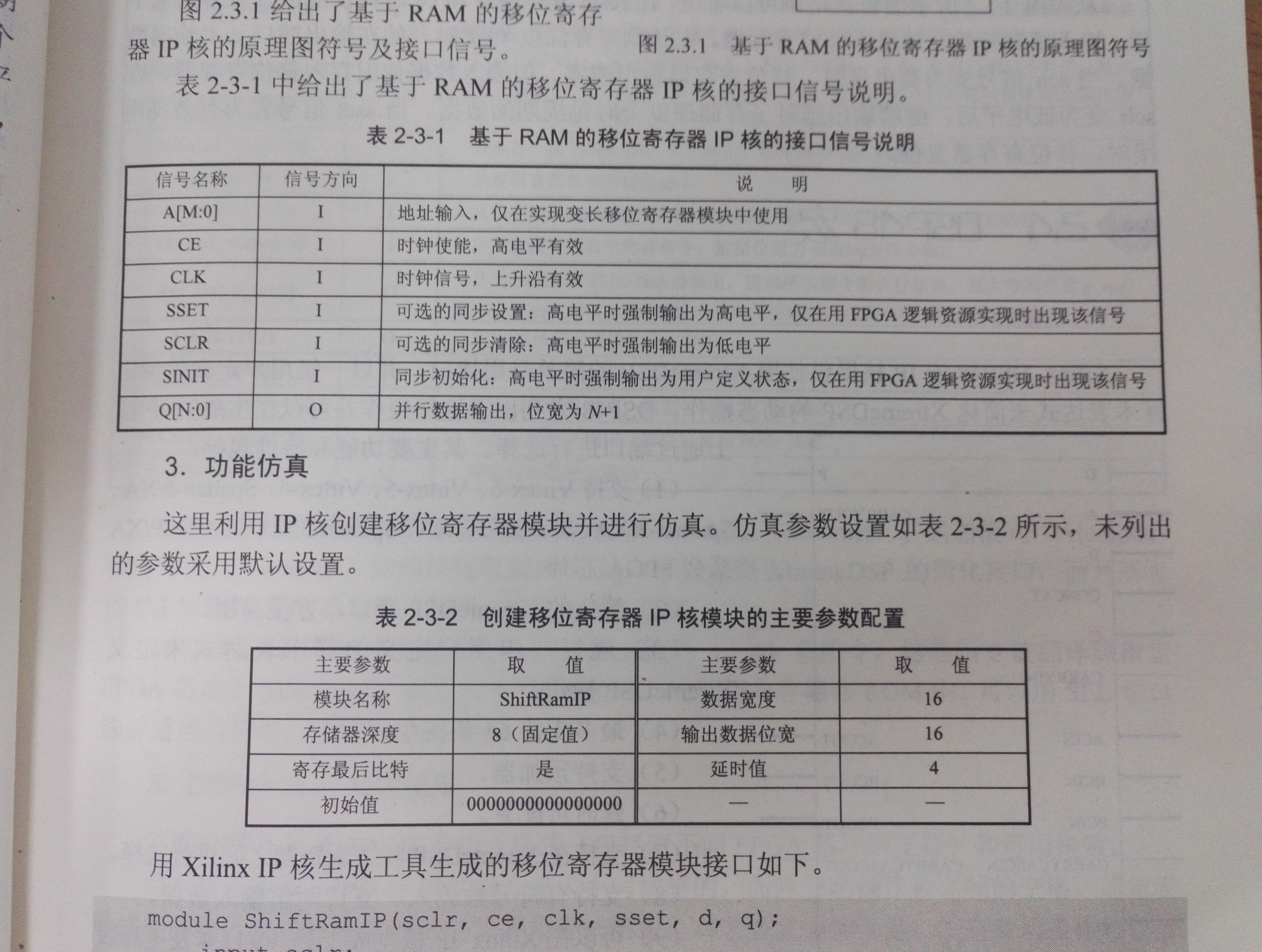

先贴一张ip核模块的接口参数图

生成3*3窗口需要两个寄存器,参数设置为数据宽度8,深度一个为4,另一个为3,选sclr端口

然后把两个移位寄存器串联起来就可以了

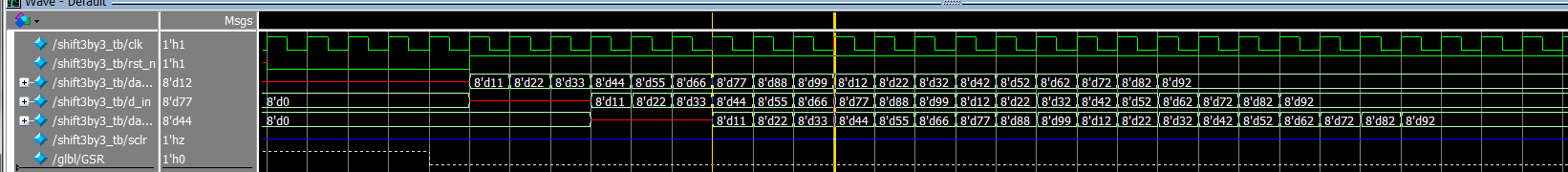

仿真的时候写好激励就行

放上最后仿真图

两条线那会是不是3*3矩阵呀,然后往右推就行。

顶层模块

module shift3by3(

clk,

rst_n,

datain,

dataout

);

input clk;

input rst_n;

input [:] datain;

output [:] dataout; wire [:] d_in;

wire sclr; shiftip shift2(

.clk(clk),

.sclr(~rst_n),

.d(datain),

.q(d_in)

); shift3 shift3(

.clk(clk),

.sclr(~rst_n),

.d(d_in),

.q(dataout)

); endmodule

tesrbench

module shiftiptb;

// Inputs

reg clk;

reg [:] d;

// Outputs

wire [:] q;

// Instantiate the Unit Under Test (UUT)

shiftip uut (

.clk(clk),

.d(d),

.q(q)

);

initial clk=;

always # clk=!clk;

initial begin

// Initialize Inputs

# d=;

# d=;

# d=;

# d=;

# d=;

# d=;

# d=;

# d=;

# d=;

// Wait 100 ns for global reset to finish

#;

// Add stimulus here

end

endmodule

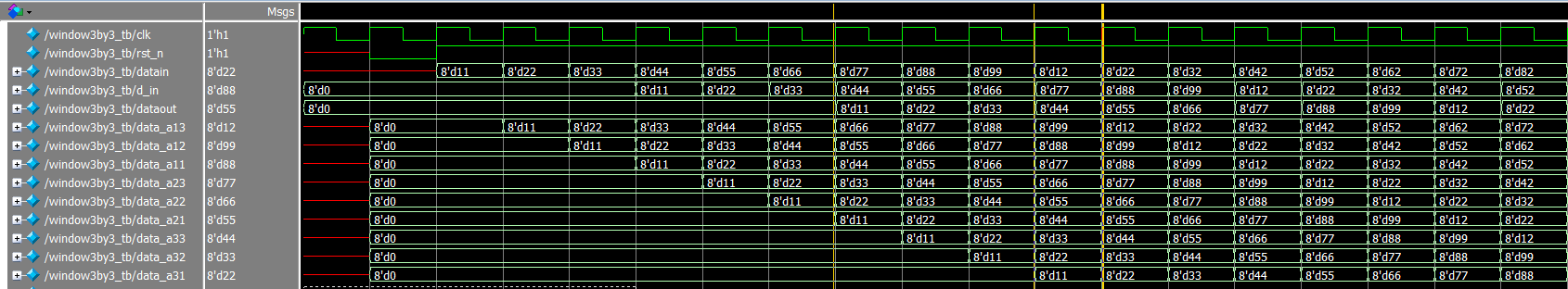

之前没有将矩阵里的9个元素列出来,现在将9个元素列出来,

赋值代码如下:

always @(posedge clk or negedge rst_n)

if(!rst_n)

begin

{a11,a12,a13} <= {'b0,8'b0,'b0};

{a21,a22,a23} <= {'b0,8'b0,'b0};

{a31,a32,a33} <= {'b0,8'b0,'b0};

row <= 'b0;

end

else

begin

row <= row3;//row3就是datain,这里延迟一个时钟

{a11,a12,a13} <= {a12,a13,row};

{a21,a22,a23} <= {a22,a23,row2};//row2是d_in

{a31,a32,a33} <= {a32,a33,row1};//row1是dataout

end

仿真图像如下图所示:

xilinx fpga 生成3*3窗口的更多相关文章

- 基于Xilinx FPGA的视频图像采集系统

本篇要分享的是基于Xilinx FPGA的视频图像采集系统,使用摄像头采集图像数据,并没有用到SDRAM/DDR.这个工程使用的是OV7670 30w像素摄像头,用双口RAM做存储,显示窗口为320x ...

- Xilinx FPGA开发环境vivado使用流程

Xilinx FPGA开发环境vivado使用流程 1.启动vivado 2016.1 2.选择Create New Project 3.指定工程名字和工程存放目录 4.选择RTL Project 5 ...

- Xilinx FPGA控制器的Everspin STT-DDR4设计指南

自旋转移扭矩磁阻随机存取存储器(STT-MRAM)是一种持久性存储技术,可利用各种工业标准接口提供性能,持久性和耐用性. Everspin推出了STT-MRAM产品,该产品利用称为JE-DDR4的JE ...

- Xilinx FPGA全局介绍

Xilinx FPGA全局介绍 现场可编程门阵列 (FPGA) 具有诸多特性,无论是单独使用,抑或采用多样化架构,皆可作为宝贵的计算资产:许多设计人员并不熟悉 FPGA,亦不清楚如何将这类器件整合到设 ...

- Xilinx FPGA LVDS应用

最近项目需要用到差分信号传输,于是看了一下FPGA上差分信号的使用.Xilinx FPGA中,主要通过原语实现差分信号的收发:OBUFDS(差分输出BUF),IBUFDS(差分输入BUF). 注意在分 ...

- Xilinx FPGA引脚txt文件导入excel中

需求 为了把xilinx FPGA的官方引脚文件txt转成excel文件(实际官网中有对应的csv文件就是excel文件了...) xilinx FPGA引脚地址:https://china.xili ...

- Xilinx FPGA复位逻辑处理小结(转)

Xilinx FPGA复位逻辑处理小结 1. 为什么要复位呢? (1)FPGA上电的时候对设计进行初始化: (2)使用一个外部管脚来实现全局复位,复位作为一个同步信号将所有存储单元设置为一个已知的状态 ...

- 你真的会Xilinx FPGA的复位吗?

Get Smart About Reset: Think Local, Not Global. 对于复位信号的处理,为了方便我们习惯上采用全局复位,博主在很长一段时间内都是将复位信号作为一个I/O口, ...

- Xilinx FPGA高速串行收发器简介

1 Overview 与传统的并行实现方法相比,基于串行I/O的设计具有很多优势,包括:器件引脚数较少.降低了板空间要求.印刷电路板(PCB)层数较少.可以轻松实现PCB设计.连接器较小.电磁干扰降低 ...

随机推荐

- skywalking的核心概念

在 SkyWalking 中,TraceSegment 是一个介于 Trace 与 Span 之间的概念,它是一条 Trace 的一段,可以包含多个 Span.在微服务架构中,一个请求基本都会涉及跨进 ...

- Spring Bean各阶段生命周期的介绍

一.xml方式配置bean 二.Aware接口 2.1 BeanNameAware 2.2 BeanFactoryAware 2.3 ApplicationContextAware 2.4 Aware ...

- python之单元测试及unittest框架的使用

例题取用登录模块:代码如下 def login_check(username,password): ''' 登录校验的函数 :param username:账号 :param password: 密码 ...

- FreeSql 使用 ToTreeList/AsTreeCte 查询无限级分类表

关于无限级分类 第一种方案: 使用递归算法,也是使用频率最多的,大部分开源程序也是这么处理,不过一般都只用到四级分类. 这种算法的数据库结构设计最为简单.category表中一个字段id,一个字段fi ...

- 豆瓣Top250爬取

第一次做爬虫项目,真的开心,非常顺利爬出了豆瓣Top250的电影 @^_^@ 自从今年6月份就开始自学python,断断续续一直没好好学.直到看了‘’老男孩python3全栈教育‘’,才有所收获.但是 ...

- JQ三种提示框:提示信息框、确认框、输入文本框

浏览器的三种提示框: alert()提示信息框 confirm()提示确认框 prompt()提示输入文本框 1.alert()提示信息框 效果: 实现代码: <script> alert ...

- 【部分】@using (Html.BeginForm())参数示例

原文:https://www.cnblogs.com/firstcsharp/p/3238321.html 1.指定表单提交方式和路径等 @using (Html.BeginForm("In ...

- Feign拦截器应用 (F版)

Spring Cloud 为开发者提供了在分布式系统中的一些常用的组件(例如配置管理,服务发现,断路器,智能路由,微代理,控制总线,一次性令牌,全局锁定,决策竞选,分布式会话集群状态).使用Sprin ...

- elasticsearch7.6 安装 并且开启外网访问,真的好累。

下载 下载页面 https://www.elastic.co/cn/downloads/elasticsearch wget https://artifacts.elastic.co/download ...

- SpringCloud之OpenFeign

SpringCloud之openFeign Spring Cloud的子项目之一,Spring Cloud OpenFeign以将OpenFeign集成到Spring Boot应用中的方式,为微服务架 ...