VHDL之concurrent之operators

Using operators

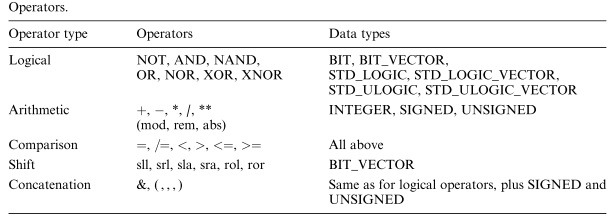

Operators can be used to implement any combinational circuit. However, as will become apparent later, complex circuits are usually easier to write using sequential code, even if the circuit does not contain sequential logic.

Example Multiplexer

---------------------------------------

LIBRARY ieee;

USE ieee.std_logic_1164.all;

---------------------------------------

ENTITY mux IS

PORT ( a, b, c, d, s0, s1: IN STD_LOGIC;

y: OUT STD_LOGIC);

END mux;

---------------------------------------

ARCHITECTURE pure_logic OF mux IS

BEGIN

y <= (a AND NOT s1 AND NOT s0) OR

(b AND NOT s1 AND s0) OR

(c AND s1 AND NOT s0) OR

(d AND s1 AND s0);

END pure_logic;

---------------------------------------

Miscellaneous operators

** Exponentiation

abs Absolute value

The exponentiation operator has two operands. This operator is defined for any integer or floating point number. The right operand (exponent) must be of integer type. When the exponent is the positive integer, then the left operand is repeatedly multiplied by itself. When the exponent is the negative number, then the result is a reverse of exponentiation with the exponent equal to the absolute value of the right operand. If the exponent is equal to 0 the result will be 1.

The abs operator has only one operand. It allows defining the operand's absolute value. The result is of the same type as the operand.

2 ** =

3.8 ** = 54.872

** (-) = / (**) = 0.0625

VHDL之concurrent之operators的更多相关文章

- VHDL之concurrent之generate

GENERATE It is another concurrent statement (along with operators and WHEN). It is equivalent to the ...

- VHDL之concurrent之when

WHEN (simple and selected) It is one of the fundamental concurrent statements (along with operators ...

- VHDL之concurrent之block

1 Simple BLOCK The simple block represents only a way of partitioning the code. It allows concurrent ...

- Concurrent.Thread.js

(function(){ if ( !this.Data || (typeof this.Data != 'object' && typeof this.Data != 'functi ...

- how to forget about delta cycles for RTL design

A delta cycle is a VHDL construct used to makeVHDL, a concurrent language, executable on asequential ...

- VHDL基础1

Description Structure 一个可综合的VHDL描述中一般由3部分组成:LIBRARY declarations.ENTITY.ARCHITECTURE Library(库)用来设计重 ...

- ConCurrent in Practice小记 (3)

ConCurrent in Practice小记 (3) 高级同步技巧 Semaphore Semaphore信号量,据说是Dijkstra大神发明的.内部维护一个许可集(Permits Set),用 ...

- ConCurrent in Practice小记 (2)

Java-ConCurrent2.html :first-child{margin-top:0!important}img.plugin{box-shadow:0 1px 3px rgba(0,0,0 ...

- 让WPS支持VHDL的关键词加粗

WPS的VBA在这里下载:http://bbs.wps.cn/forum.php?mod=viewthread&tid=22347925 语法高亮是参考Word的,这篇文章:http://bl ...

随机推荐

- Matplotlib基本使用简介

目录 Matplotlib基本使用简介 1. Matplotlib简介 2. Matplotlib操作简介 Matplotlib基本使用简介 1. Matplotlib简介 Matplotlib是 ...

- python json结构

=====================================================json==============================import reques ...

- Windows独享主机如何修改远程登录3389端口

” 完 成数值修改操作后,我们再将鼠标定位于注册表分支HKEY_LOCAL_MACHINE\SYSTEM\CurrentControlSet \Control\Terminal Server\WinS ...

- dinic算法求最大流的学习

http://trp.jlu.edu.cn/software/net/lssx/4/4.38.htm http://www.cnblogs.com/zen_chou/archive/0001/01/0 ...

- 使用JQUERY的flexselect插件来实现将SELECT下拉菜单变成自动补全输入框

这也是下拉列表太长了之后,使用的同事提出来的意见, 然后,本来开始想将DJANGO的那个后台下拉菜单移植过来的,但发现不现实,也麻烦, 就找了几个JQUERY的插件测试了一下,最后选中了flexsel ...

- Spring MVC-控制器(Controller)-可参数化视图控制器(Parameterizable View Controller )示例(转载实践)

以下内容翻译自:https://www.tutorialspoint.com/springmvc/springmvc_parameterizableviewcontroller.htm 说明:示例基于 ...

- javascript 获取当前对象

<a href="dsfjlsdjf" onclick="testGet()"> 请教编写testGet()函数获取这个超链接href属性,限制例如 ...

- [字典树] poj 2418 Hardwood Species

题目链接: id=2418">http://poj.org/problem?id=2418 Hardwood Species Time Limit: 10000MS Memory ...

- 使用Pods和自定义静态库实现多工程联编

使用Pods和自定义静态库实现多工程联编 字数607 阅读112 评论0 喜欢0 近来随着公司项目开发的深入,项目的规范也就越来越高了,为了更加方便的管理自定义静态库与pods之间的联系,好好的研究了 ...

- Codeforces--617B--Chocolate(规律)

Chocolate Time Limit: 1000MS Memory Limit: 262144KB 64bit IO Format: %I64d & %I64u Submit ...